# This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

Design implementation low energy fast fourier transform/inverse fast fourier transform (FFT/IFFT) processor based on asynchronous-logic

Chong, Kwen Siong

2007

Chong, K. S. (2007). Design implementation low energy fast fourier transform/inverse fast fourier transform (FFT/IFFT) processor based on asynchronous-logic. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/3447

https://doi.org/10.32657/10356/3447

Nanyang Technological University

Downloaded on 09 Apr 2024 14:34:58 SGT

# DESIGN AND IMPLEMENTATION OF A LOW ENERGY FAST FOURIER TRANSFORM / INVERSE FAST FOURIER TRANSFORM (FFT/IFFT) PROCESSOR BASED ON ASYNCHRONOUS-LOGIC

Chong Kwen Siong

School of Electrical and Electronic Engineering

A thesis submitted to the Nanyang Technological University in fulfilment of the requirement for the degree of Doctor of Philosophy

2007

Acknowledgements

Acknowledgements

Throughout this PhD program, I owe much to my main supervisor, Dr Gwee Bah

Hwee, and co-supervisor, Dr Joseph S. Chang. I attribute to them for kindling

my interest in research, particularly in the solid-state circuit design and later more

specifically, asynchronous-logic design. Dr Gwee gave me many invaluable

advice, encouragement, and support throughout my candidature. He has helped

me to develop a positive attitude toward difficulty. Dr Chang, a philosopher I

could say, inspired me to look at my project and even my life in different

perspectives. He has motivated me, through writing and speaking, to think as

critically as possible; I consider this critical thinking priceless.

Countless thanks and appreciation to those who have helped me with this thesis

- especially those who have instructed and guided me and whom I have worked

and studied with. They include Mr Loy Teck Pui, Mr Victor Adrian, Miss Ng

Lay Suan, Mr Thet Naing Kyaw, Mr Maung Myo Tun, Mr Chua Chien Chung, Mr

Chang Khia Ho, Mr Lim Khoon Aun, Mr Zhao Qingda, Mr Yang Jin, Mr Victor

Putra Lesmana, Mr Ricky Setiawan, and Miss Xu Wen. Their friendship is

greatly appreciated.

I would like to express my gratitude to my parents and family members for their

consistent support and understanding throughout my life. Finally, I would not

forget my love, Miss Kee Pei Ling, for her patience, sharing, and support,

especially accompanying me to the lab during the weekends and holidays. This

thesis is dedicated to her.

*Acknowledgements* ii

This research work was funded by the ASEAN-EU University Network Programme (AUNP), the Singapore Millennium Foundation PhD Scholarship, and the Nanyang Technological University Research Student Scholarship. The support I received from these organizations and foundation is greatly appreciated.

Table of Contents iii

# **Table of Contents**

| Acknowledgments                                               | 1    |

|---------------------------------------------------------------|------|

| Table of Contents                                             | iii  |

| Summary                                                       | vi   |

| List of Figures                                               | viii |

| List of Tables                                                | xii  |

| Symbols and Abbreviations                                     | xiv  |

| Chapter 1 Introduction                                        | 1    |

| 1.1 Motivation                                                | 1    |

| 1.2 Objectives                                                | 5    |

| 1.3 Contributions                                             | 6    |

| 1.4 Organization                                              | 11   |

| Chapter 2 Literature Review                                   | 13   |

| 2.1 Low Power Low Energy Design Techniques                    | 13   |

| 2.1.1 Mechanisms of Power Dissipation                         | 13   |

| 2.1.2 Low Power/Energy Design Methodologies                   | 18   |

| 2.1.3 Noise Margin                                            | 20   |

| 2.2 Synchronous-Logic and Asynchronous-Logic Design Approache | s 21 |

| 2.2.1 Synchronous-Logic Design Approach                       | 21   |

| 2.2.2 Asynchronous-Logic Design Approach                      | 25   |

| 2.2.2.1 Fundamental Concepts of Asynchronous-Logic            |      |

| Design                                                        | 26   |

| 2.2.2.2 Asynchronous-Logic EDA Tools                          | 34   |

| 2.2.2.3 Basic Asynchronous-Logic Microcells                   | 36   |

| 2.2.2.4 Potential Advantages of the Asynchronous-Logic        |      |

| Approach                                                      | 43   |

| 2.3 Fast Fourier Transform and Inverse Fast Fourier Transform |      |

| (FFT/IFFT)                                                    | 47   |

| 2.4 Summary                                                   | 51   |

| Table of Contents                                              | iv  |

|----------------------------------------------------------------|-----|

| Chapter 3 Asynchronous-Logic Microcells                        | 53  |

| 3.1 Introduction                                               | 53  |

| 3.2 Proposed Latch Adder and Latch Accumulator                 | 56  |

| 3.2.1 Latch Adder                                              | 56  |

| 3.2.2 Latch Accumulator                                        | 63  |

| 3.3 Asynchronous-Logic Adder Cell                              | 66  |

| 3.3.1 Review of Asynchronous-Logic Adder Cells                 | 66  |

| 3.3.2 Proposed 2-bit Asynchronous-Logic <i>Type-γ</i> Adder    | 71  |

| 3.4 Proposed Broad B Latch Controller                          | 75  |

| 3.5 Summary                                                    | 77  |

| Chapter 4 Macrocells: Multiplier and Memory Designs            | 79  |

| 4.1 Introduction                                               | 79  |

| 4.2 Multiplier Macrocell                                       | 82  |

| 4.2.1 Review of Multiplier Designs                             | 82  |

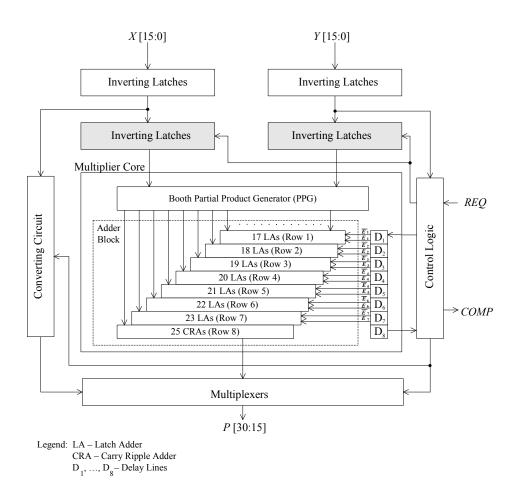

| 4.2.2 Proposed 16×16-bit Booth Array-Based Multiplier Core     | 86  |

| 4.2.3 Proposed Asynchronous-Logic 16×16-bit Control-Multiplier | 98  |

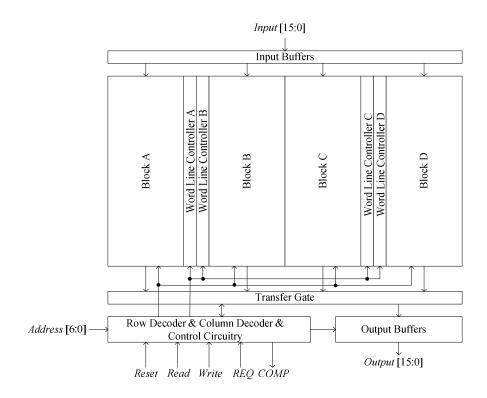

| 4.3 Proposed Asynchronous-Logic 128×16-bit Memory              | 102 |

| 4.4 Summary                                                    | 108 |

| Chapter 5 Synchronous-Logic and Asynchronous-Logic FFT/IFFT    |     |

| Processors                                                     | 110 |

| 5.1 Introduction                                               | 110 |

| 5.2 Synchronous-Logic FFT/IFFT Processor                       | 112 |

| 5.3 Proposed Asynchronous-Logic FFT/IFFT Processor             | 116 |

| 5.3.1 Control Portion                                          | 125 |

| 5.3.2 Data Paths                                               | 128 |

| 5.3.2.1 Memory Data Path                                       | 128 |

| 5.3.2.2 Shifter Data Path                                      | 129 |

| 5.3.2.3 Multiplier Data Path                                   | 131 |

| 5.3.2.4 Adder Data Path                                        | 132 |

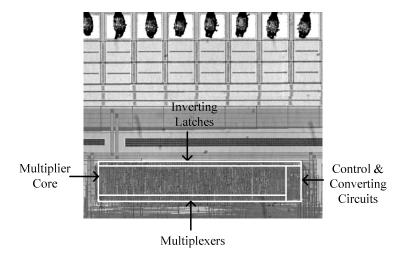

| 5.3.2.5 Write Back Data Path                                   | 133 |

| 5.4 Measurements and Comparisons                               | 134 |

Table of Contents 5.5 Summary 148 **Chapter 6 Conclusions and Recommendations** 149 6.1 Conclusions 149 6.2 Recommendations: Future Research 152 6.2.1 Development of Advanced Asynchronous-Logic Design Tools 152 6.2.2 Design of Microcells and Macrocells 152 6.2.3 Leakage Current Reduction by Asynchronous-Logic Techniques in Advanced CMOS Processes 154 6.2.4 Adoption of Asynchronous-Logic Circuits in the Sub-Threshold Region 155 **Author's Publications** 156 **Bibliography** 158

Summary vi

# **Summary**

This thesis pertains to circuit designs using the promising asynchronous-logic (async) approach as opposed to the prevalent synchronous-logic (sync) approach, with emphases on low voltage operation and low energy dissipation. The circuits designed herein span from low-level circuits (microcells, where the transistor count is < 100), mid-level circuits (macrocells, where the transistor count is > 100) to a complete system – a Fast Fourier Transform/Inverse Fast Fourier Transform (FFT/IFFT) processor that in part embodies these microcells and macrocells. The application of the processor is for energy-critical portable audio biomedical applications, including hearing aids.

The novel microcells include a Latch Adder (LA), a Latch Accumulator, a *Type-\gamma* adder (a 2-bit async carry completion sensing adder), and an async latch controller in broad data validation. The novelty of these microcells includes the incorporation of different functional features (e.g. latch and delay enhancements), resulting in increased versatility, compactness, and lower energy dissipation. The novel macrocells include a 16×16-bit Booth array-based multiplier core, a 16×16-bit 'Control-Multiplier' specifically for an FFT algorithm, and a 128×16-bit memory macrocell. The novelty of these macrocells includes reduced spurious switching (e.g. by means of latching and gating), resulting in reduced energy dissipation. The functionality and attributes of these microcells and macrocells are verified by computer simulations and on the basis of practical measurements on prototype ICs.

Summary vii

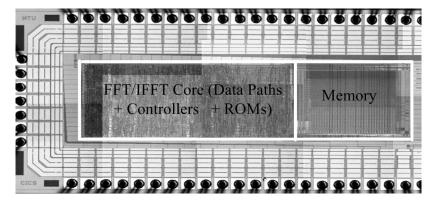

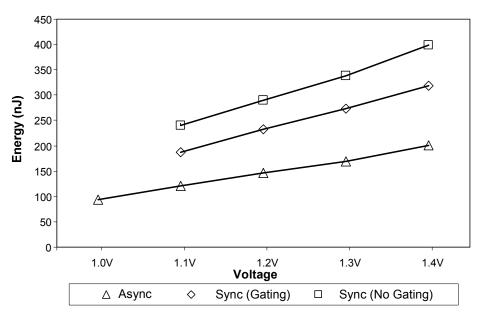

The FFT/IFFT processor is an async 128-point radix-2 decimation-in-time FFT/IFFT processor. The prototype processor IC dissipates 93nJ - 201nJ per FFT/IFFT computation @  $V_{\text{DD}} = 1.0\text{V} - 1.4\text{V}$ , features a delay of < 1.95ms @  $V_{\text{DD}} \geq 1.0\text{V}$ , and occupies  $1.6\text{mm}^2$  IC area @  $0.35\mu\text{m}$  CMOS process. When benchmarked against its sync counterpart with and without clock gating, the async processor dissipates ~ 37% and ~ 50% lower energy respectively. The minor drawbacks of the async processor are a largely inconsequential 10% larger IC area and an inconsequential 1.4 times worse delay (inconsequential due to the intended low speed (< 5MHz) hearing aid application).

The work reported in this thesis demonstrates that by means of appropriate design techniques, designs based on the promising async approach can feature superior (lower) energy attributes over designs based on the prevalent sync approach.

List of Figures viii

# **List of Figures**

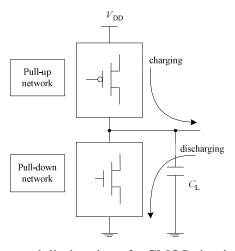

| Fig. 2.1  | Charging and discharging of a CMOS circuit during           |    |

|-----------|-------------------------------------------------------------|----|

|           | switching                                                   | 14 |

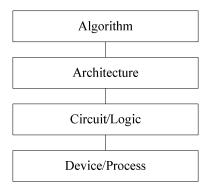

| Fig. 2.2  | Power/energy methodology hierarchy                          | 18 |

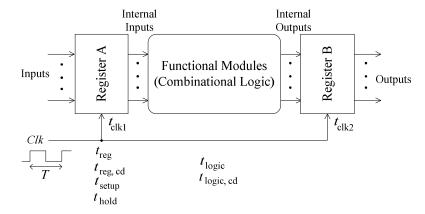

| Fig. 2.3  | A sync circuit                                              | 22 |

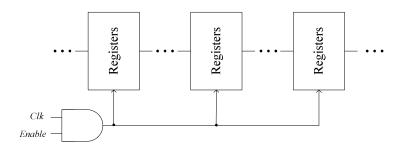

| Fig. 2.4  | Clock gating approach                                       | 24 |

| Fig. 2.5  | (a) Two-phase handshaking protocol, and (b) four-phase      |    |

|           | handshaking protocol                                        | 28 |

| Fig. 2.6  | Four channel types: (a) nonput, (b) push, (c) pull, and     |    |

|           | (d) biput                                                   | 29 |

| Fig. 2.7  | Push channel data valid schemes for (a) two-phase           |    |

|           | handshaking protocol, and (b) four-phase handshaking        | 31 |

|           | protocol                                                    |    |

| Fig. 2.8  | A simple four-phase bundled data pipeline                   | 33 |

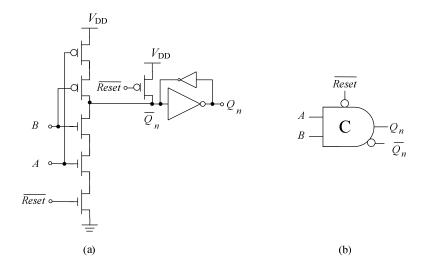

| Fig. 2.9  | C-Muller circuit: (a) schematic, and (b) symbol             | 37 |

| Fig. 2.10 | Different C-Muller gate designs: (a) three-input            |    |

|           | asymmetric C-Muller gate with low reset, (b) three-input    |    |

|           | asymmetric C-Muller gate with high reset, (c) two-input     | 38 |

|           | asymmetric C-Muller gate with low reset, and (d) two-       |    |

|           | input asymmetric C-Muller gate with high reset              |    |

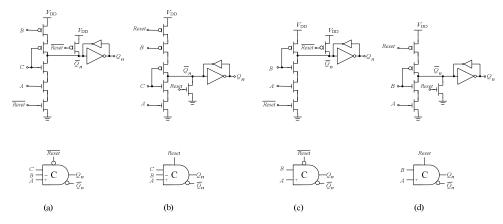

| Fig. 2.11 | Different latch designs: (a) TG latch, (b) NSP latch, (c)   |    |

|           | Trans latch, and (d) Mux latch                              | 39 |

| Fig. 2.12 | Different async latch controller designs: (a) Broadish, and |    |

|           | (b) Broad A                                                 | 41 |

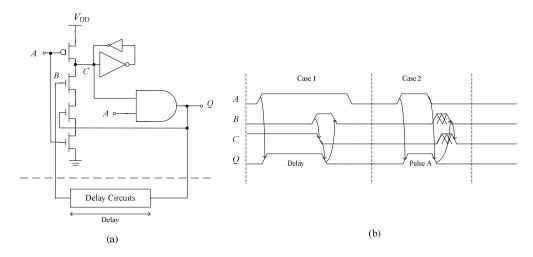

| Fig. 2.13 | The pulse generator (a) schematic, and (b) its timing       |    |

|           | diagram                                                     | 42 |

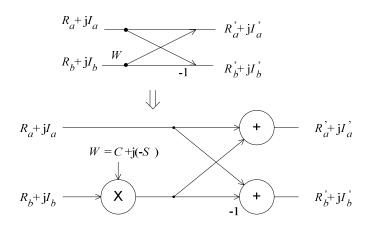

| Fig. 2.14 | A radix-2 butterfly                                         | 49 |

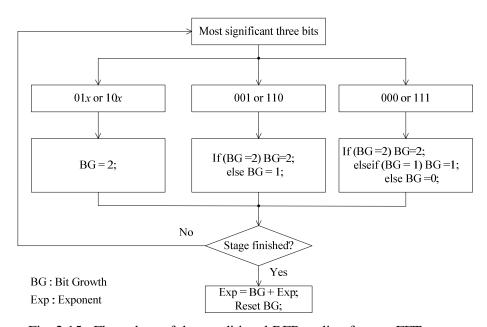

| Fig. 2.15 | Flow chart of the conditional BFP scaling for one FFT       |    |

|           | stage                                                       | 51 |

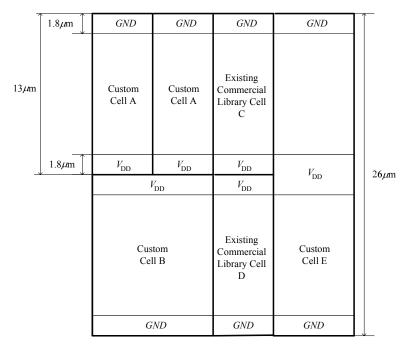

| Fig. 3.1  | A symbolic template for library cells                       | 54 |

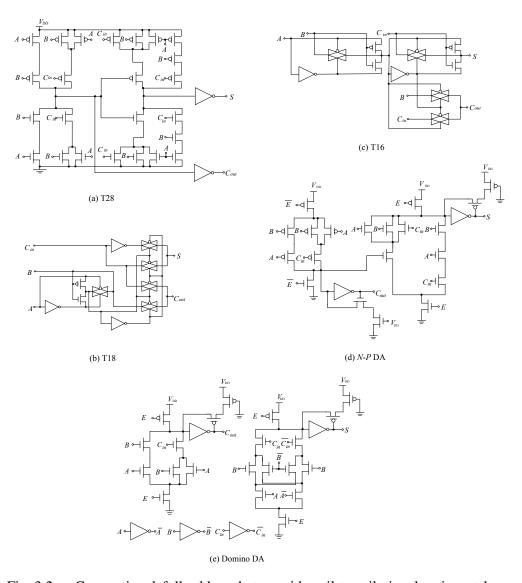

| Fig. 3.2  | Conventional full adders that provide rail-to-rail signal   |    |

|           | swing at low voltage operation: (a) T28 adder, (b) T18      | 57 |

|           | adder, (c) T16 adder, (d) N-P DA, and (e) Domino DA         |    |

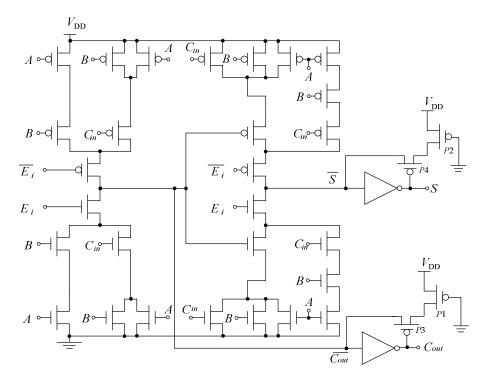

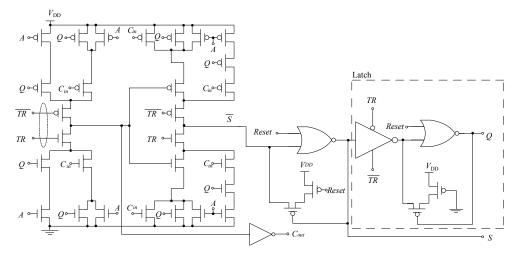

| Fig. 3.3  | Circuit schematic of the Latch Adder (LA)                   | 59 |

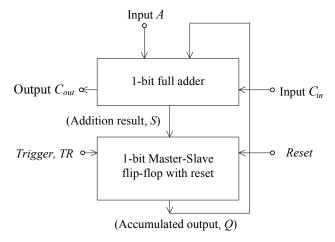

| Fig. 3.4  | The simplified block diagram of an accumulator realized     |    |

|           | by usual design (a standard adder and a separate flip-flop) | 64 |

| Fig. 3.5  | The proposed Latch Accumulator                              | 65 |

|           |                                                             |    |

List of Figures ix

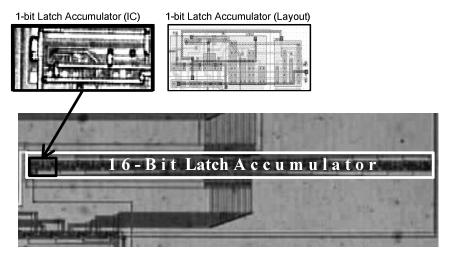

| Fig. 3.6  | Microphotograph of the proposed 16-bit Latch                   |     |

|-----------|----------------------------------------------------------------|-----|

|           | Accumulator                                                    | 66  |

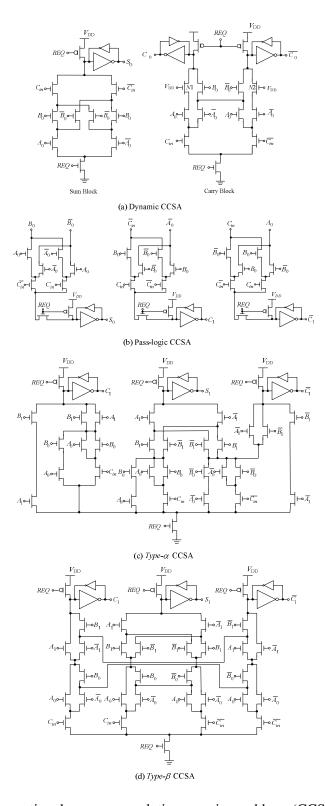

| Fig. 3.7  | Conventional carry completion sensing adders (CCSAs):          |     |

|           | (a) 1-bit dynamic CCSA, (b) 1-bit pass-logic CCSA,             | 69  |

|           | (c) 2-bit $Type-\alpha CCSA$ , and (d) 2-bit $Type-\beta CCSA$ |     |

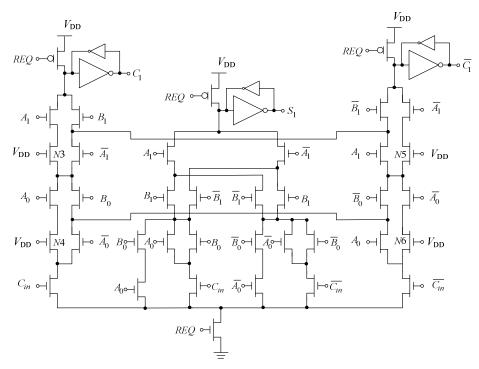

| Fig. 3.8  | Circuit schematic of the proposed CCSA, $Type-\gamma$          | 72  |

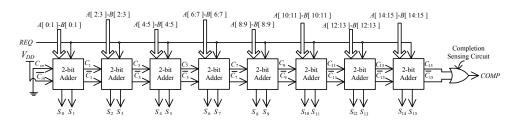

| Fig. 3.9  | Block diagram of a 16-bit async adder embodying the            |     |

|           | proposed <i>Type-γ</i> CCSAs                                   | 73  |

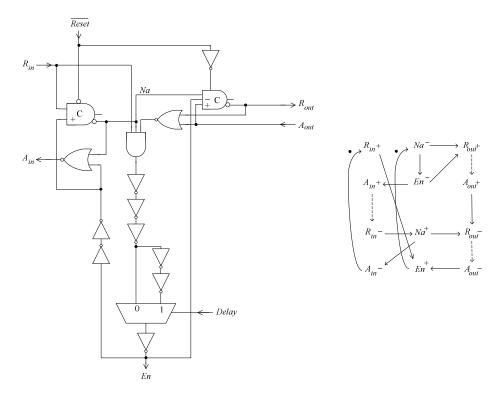

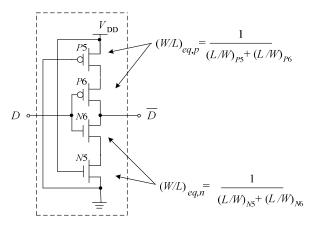

| Fig. 3.10 | The proposed latch controller: Broad B latch controller        | 76  |

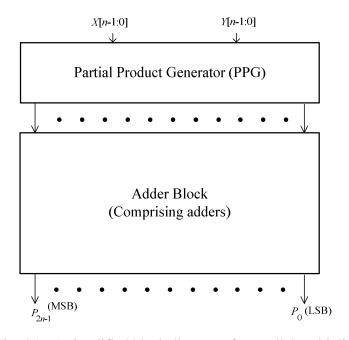

| Fig. 4.1  | A simplified block diagram of a parallel multiplier            | 83  |

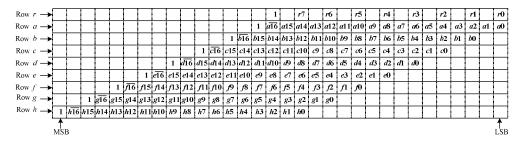

| Fig. 4.2  | The partial products in a 2's complement 16×16-bit Booth       |     |

|           | radix-4 multiplier                                             | 87  |

| Fig. 4.3  | Block diagram of the proposed 16×16-bit Booth array            |     |

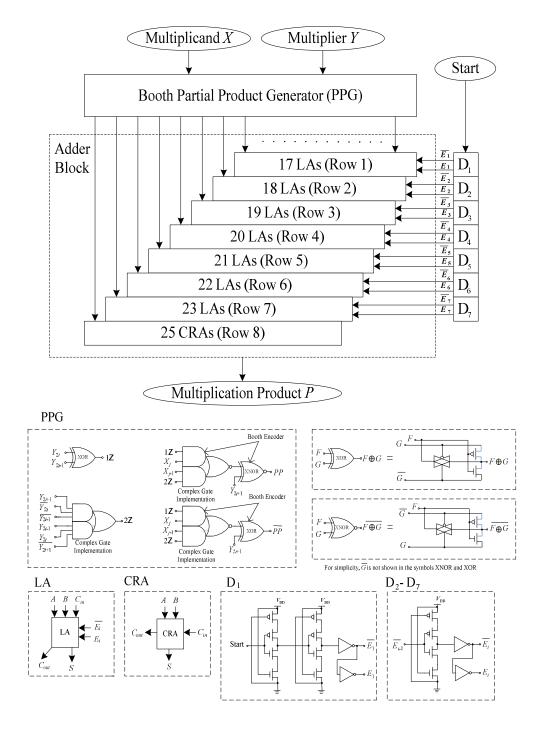

|           | multiplier, SB-Proposed16                                      | 88  |

| Fig. 4.4  | Delay circuit                                                  | 90  |

| Fig. 4.5  | Power breakdown (in % and $\mu$ W) of different array          |     |

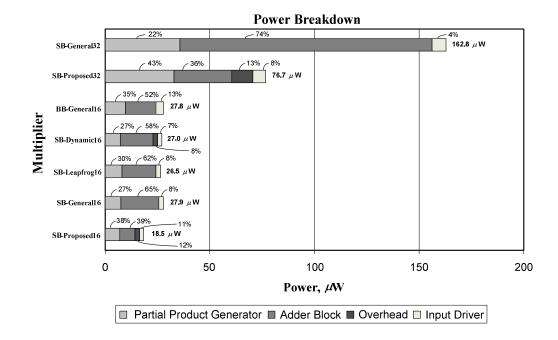

|           | multipliers based on simulations @ 1.1V, 1MHz                  | 91  |

| Fig. 4.6  | Switching analysis in the Adder Block of various               |     |

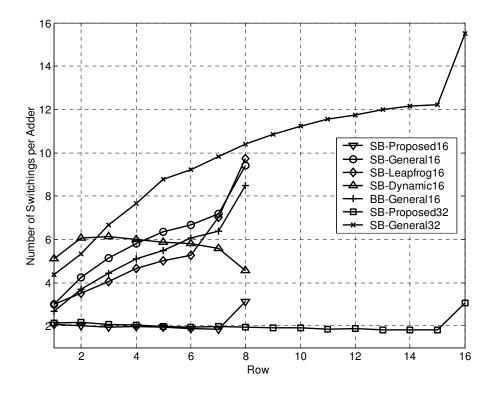

|           | multipliers                                                    | 94  |

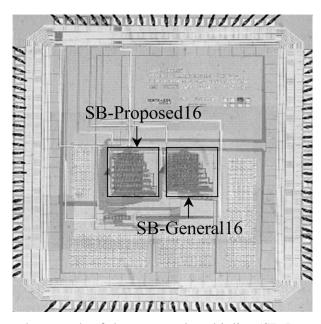

| Fig. 4.7  | Microphotograph of the proposed multiplier                     |     |

|           | (SB-Proposed16) and the conventional multiplier                | 95  |

|           | (SB-General16)                                                 |     |

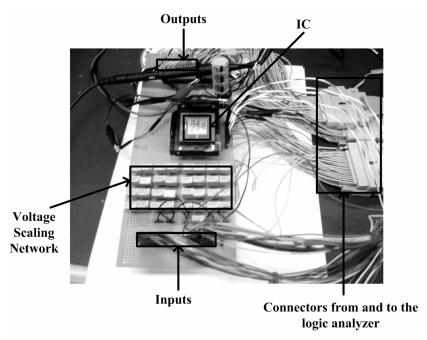

| Fig. 4.8  | The test jig for the multiplier IC                             | 96  |

| Fig. 4.9  | Block diagram of the Control-Multiplier                        | 99  |

| Fig. 4.10 | Microphotograph of the Control-Multiplier (part of the         |     |

|           | FFT/IFFT prototype IC)                                         | 101 |

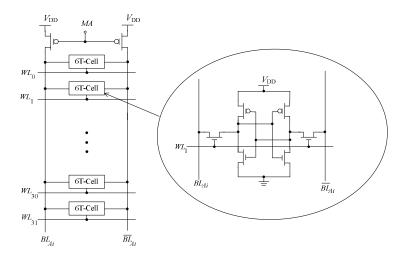

| Fig. 4.11 | Block diagram of the 128×16-bit single-port async memory       | 102 |

| Fig. 4.12 | Circuit schematic of the storage cells for one column of a     |     |

|           | 32×16-bit sub-memory block; 16 columns required for one        | 103 |

|           | sub-memory block                                               |     |

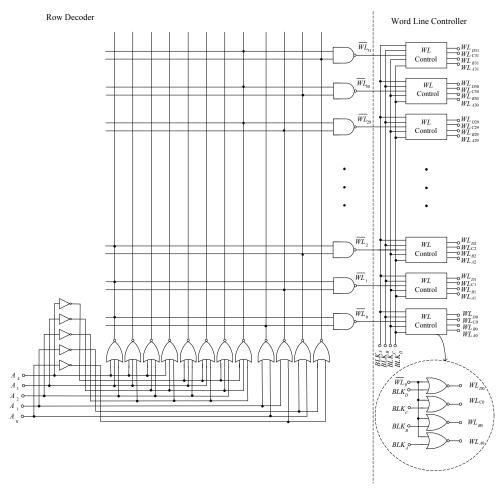

| Fig. 4.13 | Circuit schematics of the Row Decoder and the Word Line        |     |

|           | Controller                                                     | 104 |

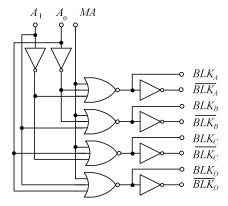

| Fig. 4.14 | Circuit schematic of the Column Decoder                        | 104 |

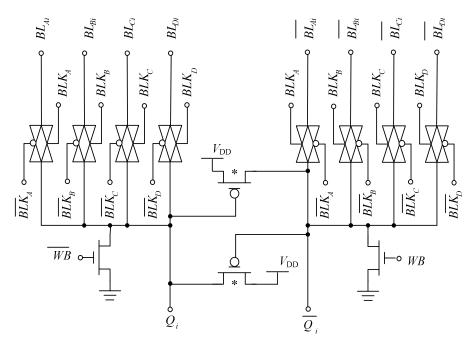

| Fig. 4.15 | Circuit schematic of the Transfer Gate                         | 105 |

| Fig. 4.16 | Circuit schematic of the Input Buffer                          | 105 |

| Fig. 4.17 | Circuit schematic of the completion detection circuit for      |     |

|           | the memory macrocell                                           | 106 |

List of Figures x

| Fig. 4.18 | The async 128×16-bit memory macrocell (part of the             |     |

|-----------|----------------------------------------------------------------|-----|

|           | FFT/IFFT prototype IC)                                         | 107 |

| Fig. 5.1  | Block diagram of the sync FFT/IFFT processor                   | 112 |

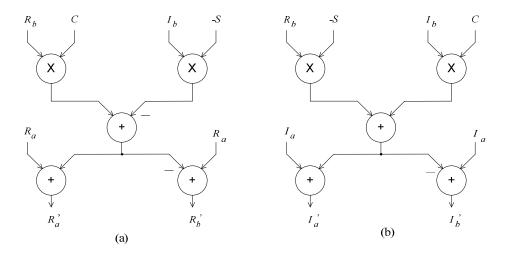

| Fig. 5.2  | Data flows for each butterfly operation: (a) to compute the    |     |

|           | real outputs, and (b) to compute the imaginary outputs         | 113 |

| Fig. 5.3  | Pipeline sequences for each data flow                          | 114 |

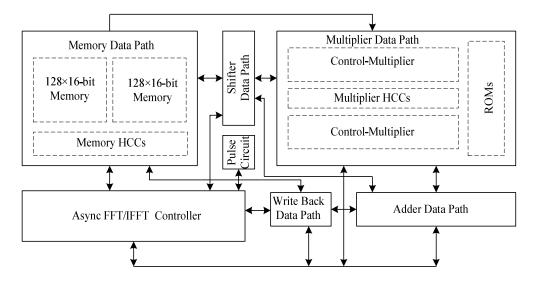

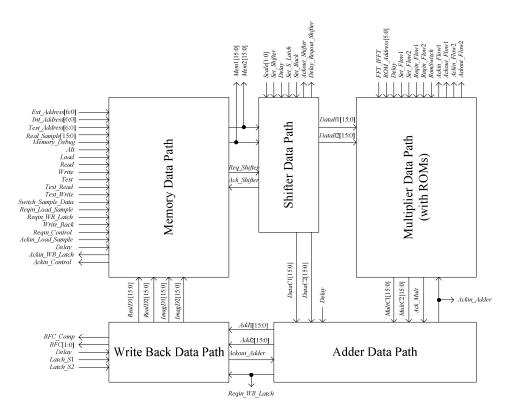

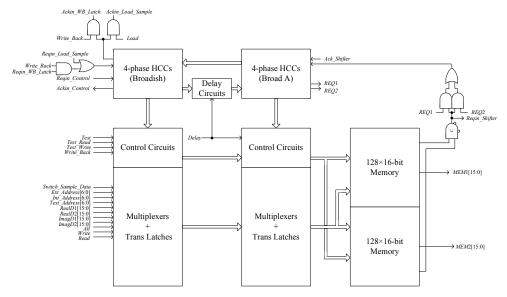

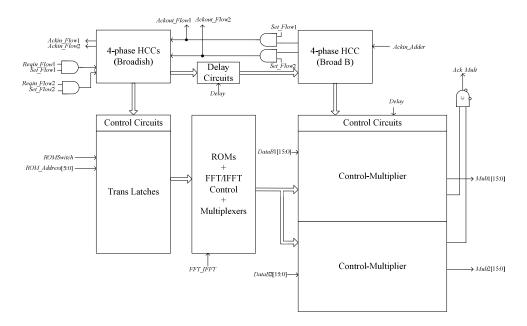

| Fig. 5.4  | The block diagram of the async FFT/IFFT processor              | 116 |

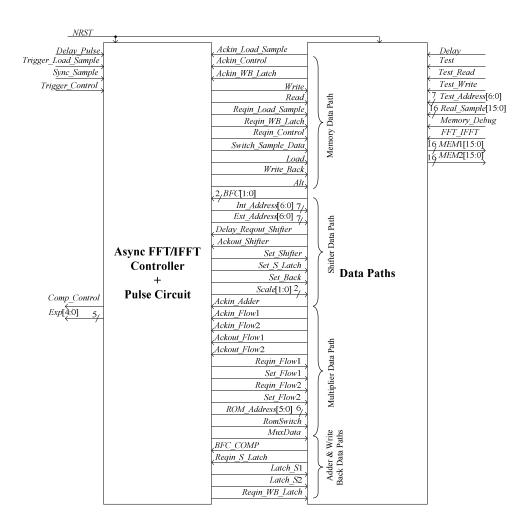

| Fig. 5.5  | The interface signals in the async FFT/IFFT processor          | 117 |

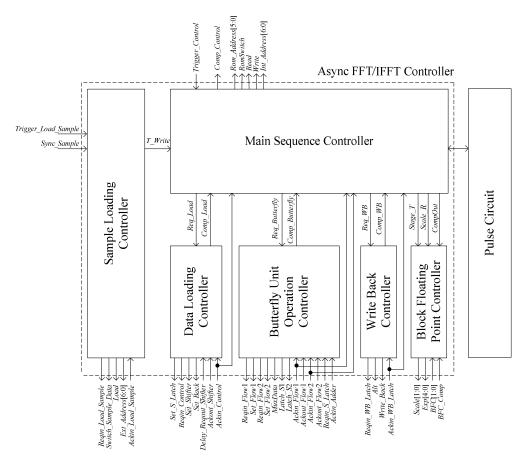

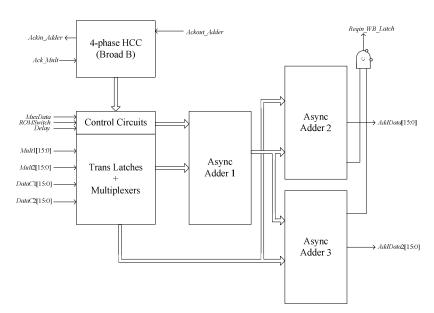

| Fig. 5.6  | Architecture of the control portion in the FFT/IFFT            |     |

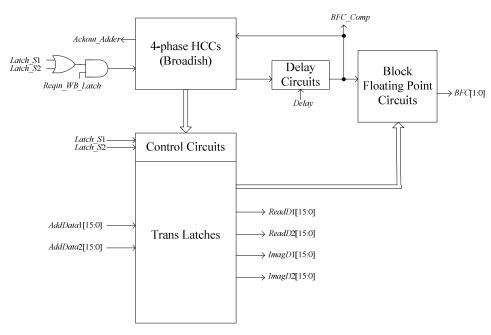

|           | processor                                                      | 120 |

| Fig. 5.7  | Architecture of the data paths in the async FFT/IFFT           |     |

|           | processor                                                      | 121 |

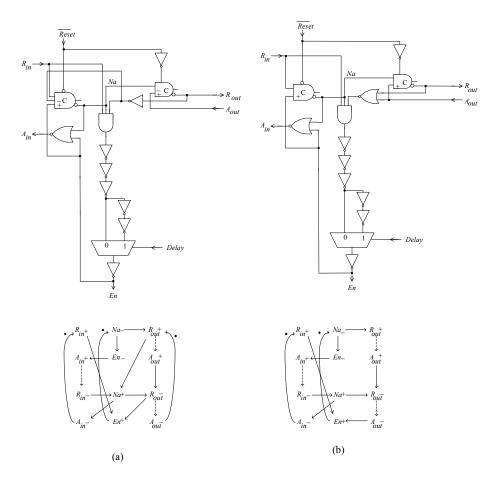

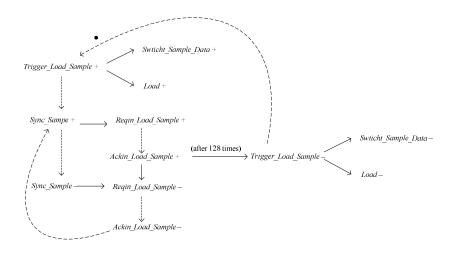

| Fig. 5.8  | The simplified signal transition graph for loading new         |     |

|           | samples                                                        | 122 |

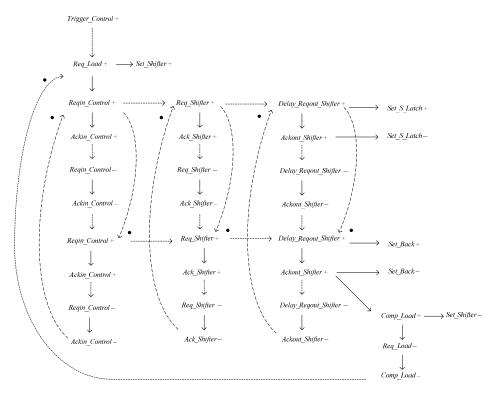

| Fig. 5.9  | The simplified signal transition graph for loading data for    |     |

|           | butterfly operations                                           | 123 |

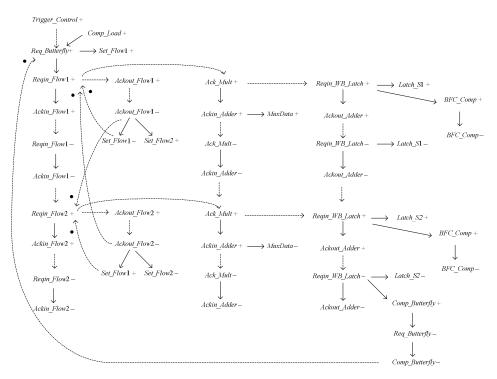

| Fig. 5.10 | The simplified signal transition graph for executing a         |     |

|           | butterfly operation                                            | 124 |

| Fig. 5.11 | The simplified signal transition graph for writing outputs     |     |

|           | into the memory                                                | 125 |

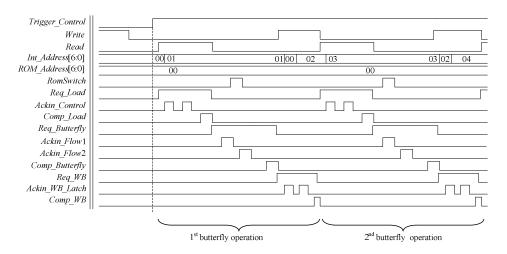

| Fig. 5.12 | A modeling timing diagram for the Async FFT/IFFT               |     |

|           | Controller. Note that the pertinent signals are only shown     | 126 |

|           | and the delays herein do not reflect the actual circuit delays |     |

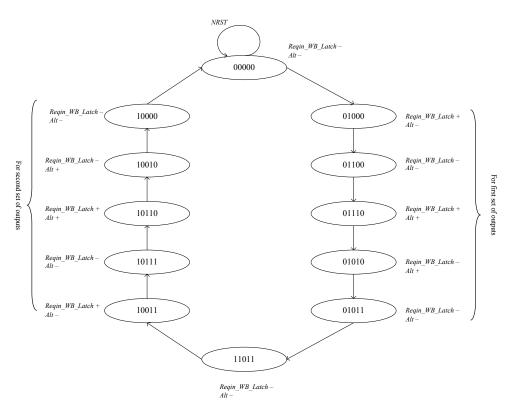

| Fig. 5.13 | The control-state signal transition flow (from the current     |     |

|           | state to the next state) in the Write Back Controller          | 127 |

| Fig. 5.14 | Block diagram of the Memory Data Path                          | 129 |

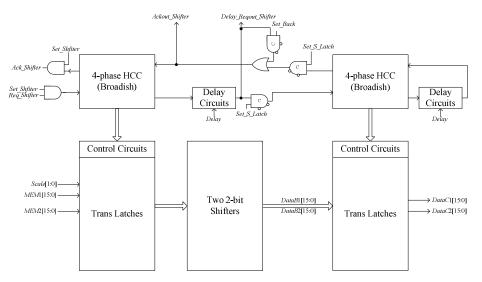

| Fig. 5.15 | Block diagram of the Shifter Data Path                         | 130 |

| Fig. 5.16 | Block diagram of the Multiplier Data Path                      | 131 |

| Fig. 5.17 | Block diagram of the Adder Data Path                           | 132 |

| Fig. 5.18 | Block diagram of the Write Back Data Path                      | 134 |

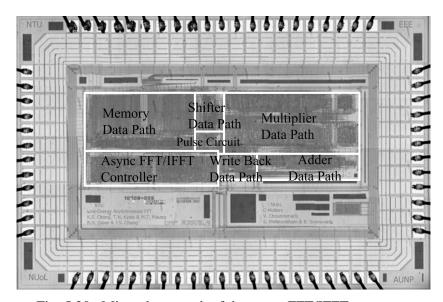

| Fig. 5.19 | Microphotograph of the sync FFT/IFFT processor                 | 135 |

| Fig. 5.20 | Microphotograph of the async FFT/IFFT processor                | 135 |

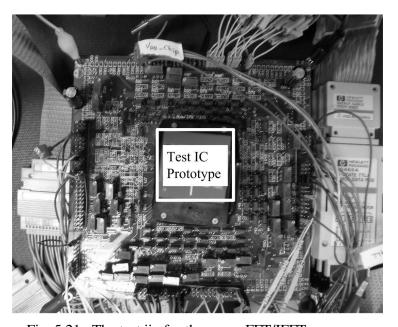

| Fig. 5.21 | The test jig for the async FFT/IFFT processor                  | 136 |

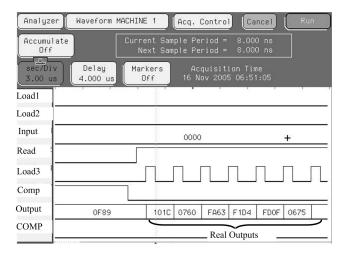

| Fig. 5.22 | The real outputs obtained using the logic analyzer             | 137 |

| Fig. 5.23 | Energy dissipation for the async and sync (@ 1MHz)             |     |

|           | FFT/IFFT processors at 1.0V to 1.4V                            | 139 |

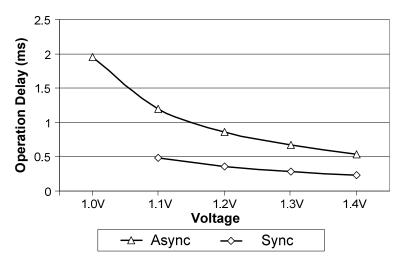

| Fig. 5.24 | Delays for the async and sync FFT/IFFT processors              | 142 |

|                                                          | xi                                                                                                                                                                                                        |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

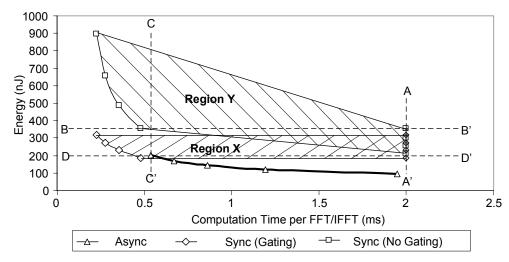

| Energy-delay curves of the async and sync FFT/IFFT       |                                                                                                                                                                                                           |

| processors                                               | 144                                                                                                                                                                                                       |

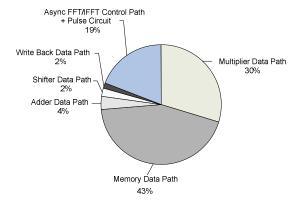

| The distribution of the number of transistors in various |                                                                                                                                                                                                           |

| modules in the async FFT/IFFT processor; the total       | 145                                                                                                                                                                                                       |

| number of transistors is ~ 74K                           |                                                                                                                                                                                                           |

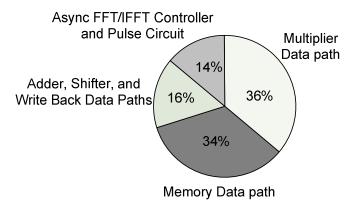

| The energy breakdown (in %) of the async FFT/IFFT        |                                                                                                                                                                                                           |

| processor at 1.1V to 1.4V                                | 146                                                                                                                                                                                                       |

|                                                          | processors  The distribution of the number of transistors in various modules in the async FFT/IFFT processor; the total number of transistors is ~ 74K  The energy breakdown (in %) of the async FFT/IFFT |

List of Tables xii

# **List of Tables**

| TABLE 1.1 | Specifications of the FFT/IFFT Processor                                                                    | 6   |

|-----------|-------------------------------------------------------------------------------------------------------------|-----|

| TABLE 2.1 | Noise Margins for the Targeted Hearing Aid Application in                                                   |     |

|           | the Chosen 0.35 µm CMOS Process                                                                             | 21  |

| TABLE 2.2 | Timing Notations for the Sync Circuit                                                                       | 22  |

| TABLE 2.3 | Dual-rail Coding                                                                                            | 32  |

| TABLE 2.4 | Comparisons between Sync and Async Designs                                                                  |     |

|           | (Normalized to a Fully Sync Design)                                                                         | 44  |

| TABLE 3.1 | Energy, Delay, Energy-delay-product (EDP) & IC Area of                                                      |     |

|           | the Proposed Latch Adder Against that of Other Full                                                         | 62  |

|           | Adders @ 1.1V, 1MHz                                                                                         |     |

| TABLE 3.2 | Energy, Delay, Energy-delay-product (EDP) & IC Area of                                                      |     |

|           | the Proposed Latch Adder Against that of Other Adders                                                       | 63  |

|           | with Latches @ 1.1V, 1MHz                                                                                   |     |

| TABLE 3.3 | Delay, Energy, Energy-delay-product (EDP) & IC Area of                                                      |     |

|           | Various 16-bit Accumulators @ 1.1V, 1MHz Based on                                                           |     |

|           | Post-layout Simulations and Measurements on Prototype                                                       | 66  |

|           | ICs                                                                                                         |     |

| TABLE 3.4 | Delay (Best-case, Average-case, and Worst-case), Energy                                                     |     |

|           | (E), Number of PTVs & IC Area of Various Adders                                                             | 74  |

| TADLE 4.1 | @ 1.1V, 1MHz                                                                                                |     |

| TABLE 4.1 | Average Number of Switchings, Energy, Delay, Area & Energy-delay-product (EDP) of Various Array Multipliers |     |

|           | @ 1.1V, 1MHz based on Post-layout Simulations and                                                           | 96  |

|           | Measurements on Prototype ICs                                                                               | 70  |

| TABLE 4.2 | Number of Trivial Multiplications and its % in 8- to 512-                                                   |     |

|           | point Radix-2 FFT Algorithms                                                                                | 99  |

| TABLE 4.3 | The Energy and IC Area for the Control-Multiplier and the                                                   |     |

|           | Multiplier Cores @ 1.1V, 1MHz                                                                               | 101 |

| TABLE 4.4 | The Characteristics of the Async 128×16-bit Memory                                                          |     |

|           | Macrocell @ 1.1V, 1MHz                                                                                      | 108 |

| TABLE 5.1 | The Top-level Signals and Functions of the Async                                                            |     |

|           | FFT/IFFT Processor                                                                                          | 118 |

| TABLE 5.2 | The Characteristics of the Sync and Async FFT/IFFT                                                          |     |

|           | Processors                                                                                                  | 138 |

List of Tables

| TABLE 5.3 | Operating Conditions for the Sync and Async FFT/IFFT      |     |

|-----------|-----------------------------------------------------------|-----|

|           | Processors                                                | 139 |

| TABLE 5.4 | Characteristics of Recent FFT Processors and the Proposed |     |

|           | Async and Benchmarked Sync FFT/IFFT Processors            | 147 |

# **Symbols and Abbreviations**

$\alpha$  — switching activity  $\tau_r$  — rise time/fall time

$\varphi$  — truncated portion for the multiplier

$\Delta f$  — frequency resolution

$\Sigma\Delta$  — sigma-delta

C<sub>L</sub> — load/output capacitance

E — energy

f — switching frequency  $f_{\text{sampling}}$  — sampling frequency

$I_a$ ,  $I_b$  — imaginary input data for a radix-2 DIT butterfly  $I_a$ ,  $I_b$  — imaginary output data for a radix-2 DIT butterfly

$I_{\rm sc}$  — short-circuit current

*k* — transistor gain

$L_{\rm eff}$  — effective transistor length

N — number of points  $NM_{\rm H}$  — noise margin high  $NM_{\rm L}$  — noise margin low

P — power

$P_{\text{leakage}}$  — leakage power  $P_{\text{sc}}$  — short-circuit power

$P_{\text{static}}$  — static power

$P_{\text{switching}}$  — switching (dynamic) power

T — time period  $t_{\text{clk1}}, t_{\text{clk2}}$  — clock delay

$t_{\text{hold}}$  — hold time for the register

$t_{

m logic}$  — maximum delay of the logic circuits  $t_{

m logic,cd}$  — contamination delay of the logic circuits

$t_{\text{reg}}$  — maximum delay of the registers  $t_{\text{reg,cd}}$  — contamination delay of the register

$t_{\text{setup}}$  — setup time for the register

$R_a$ ,  $R_b$  — real input data for a radix-2 DIT butterfly  $R_a$ ,  $R_b$  — real output data for a radix-2 DIT butterfly

$V_{

m DD}$  — supply voltage  $V_{

m out}$  — output voltage

$V_{\rm T}$  — threshold voltage of the transistor

$V_{\text{Tn}}$  — threshold voltage of the NMOS transistor  $V_{\text{Tp}}$  — threshold voltage of the PMOS transistor

$W_{\text{bit}}$  — wordlength  $W_N^{nk}$  — twiddle factor

*ACK* — the acknowledge signal

ASIC — application-specific-integrated-circuit

Async — asynchronous-logic

BB — balanced Booth

BFP — block floating point

BG — bit growth

CCSA — carry completion sensing adder

CHP — communication hardware process

COMP — the completion signal CRA — carry ripple adder

CSP — communication sequential processes

DA — dynamic adder

DCVS — differential cascode voltage swing

DFT — discrete Fourier transform

DI — delay-insensitive

DIF — decimation-in-frequency

DIT — decimation-in-time

DSP — digital signal processor

ECDL — enabled/disable CMOS differential logic

EDA — electronic design automation

EDP — energy-delay-product

EMI — electro-magnetic interference

Exp — exponent

FFT/IFFT — fast Fourier transform/inverse fast Fourier transform

HCC — handshaking control circuit

IC — integrated circuit

IP — intellectual property

IR — current-resistance

LA — Latch Adder

LSB — least significant bit

MSB — most significant bit

Mux — multiplexer

NORA — no race

NSP — N-typed single phase

NTU — Nanyang Technological University

PDP — power-delay-product

PPG — partial product generator

Symbols and Abbreviations

xvi

PTV — potential timing violation

QDI — quasi-delay-insensitive

REQ — the request signal

SB — standard Booth

SI — speed-independent

SoC — system-on-chip

SRAM — static random access memory

ST — self-timed

STG — signal transition graph

Sync — synchronous-logic

TG — transmission gate

VLSI — very large scale integration

*W/L* — width/length

#### 1

# Chapter 1

# Introduction

## 1.1 Motivation

Hearing aids (hearing instruments) are assistive high efficacy biomedical devices to improve the speech intelligibility of hearing impaired users. The primary challenges in these subminiature devices are often power dissipation related [1]–[9] due to the need to realize a number of advanced signal processing algorithms, including a filter bank [10], [11], noise reduction [12], acoustic feedback cancellation [13], [14], low-distortion output amplification [15], [16], etc. Physically, the constraints of such devices are largely due to the low voltage (1.1V – 1.4V) low energy capacity (~ 100mA·h) miniature-size battery used, and to aesthetics (e.g. small size [17]). As the life span of the battery in typical hearing aids is usually expected to be  $\sim$  100 hours or more, the current drawn (hence power dissipation) is expected to be  $\leq$  1mA @ 1.1V – 1.4V. In view of this tight power constraint, simplified versions of highly desirable complex signal processing algorithms (such as the real-time noise reduction [12]) are realized in practical hearing aids.

To satisfy the power constraint in the current-art power-critical mixed-signal hearing aids, low power (and energy) methodologies are routinely adopted to both the analog and digital circuits therein. The analog circuits include a high power-efficient Class-D amplifier [15] (~ 90% power-efficiency over a large range of

modulation index as opposed to the conventional Class-AB amplifier with  $\sim 30\%$  power-efficiency) and a high signal-to-noise ratio sigma-delta ( $\Sigma\Delta$ ) modulator [7]. The digital circuits include a low voltage medium-to-low speed but energy-efficient application-specific-integrated-circuit (ASIC) digital signal processor (DSP) [1]–[3]. The DSP therein is usually highly optimized – from the system level down to the transistor level, including a small feature-size fabrication process – and employing many low power/energy design techniques [18]–[23].

The Fast Fourier Transform (FFT) [24], [25] is one of the most fundamental signal processing algorithms in audio signal processing and it serves to provide spectrum analysis (frequency resolution) of a given set of input signals (see Chapter 2 later). In some current-art hearing aids and advanced audio devices, the DSP therein embodies the FFT as one of its core macrocells. The computation of the FFT algorithm is relatively complex and essentially comprises multiplications and additions. For high frequency resolution analysis required in some advanced audio applications, the number of points (N) of the FFT algorithm is usually large (e.g.  $N \ge 128$ ), resulting in a large number of multiplication and addition operations and correspondingly, a large number of memory accesses. In the overall hardware perspective, the FFT processor is a complex macrocell and is hence often the most power dissipative cell and that occupies a major portion of the integrated circuit (IC) real estate of the DSP.

In virtually all FFT realizations reported [26]–[34] to date, the synchronous-logic (sync) approach is the approach adopted. This sync approach is the same

approach adopted by the electronics community at large for the majority of complex digital circuit designs; the sync approach will be reviewed in Chapter 2. The sync approach is prevalent arguably due to the maturity of its design methodologies, design simplicity and the availability of many excellent commercial electronic design automation (EDA) tools [35]–[37] and established library cells. Despite the general acceptance of the sync design approach, power dissipation and speed are often difficult parameters to satisfy in ever increasing signal processing demands of advanced electronic devices. To alleviate these parameters, there has been considerable research and intensive on-going research effort on low power dissipation techniques [20]–[23] and since the 1990s, renewed research interest on the 'less accepted' asynchronous-logic (async) approach [38]–[46].

The async approach is an alternative (to sync approach) with potentially lower power dissipation and higher speed advantages largely due to the absence of a global clock infrastructure (required in the sync approach) and due to its inherent fine-grain gating operations (resulting in potentially reduced redundant operations and spurious switching/glitch). The async approach is essentially the design of circuits that are self-timed and does not require a global clock and the signaling therein is hence localized; the async approach will be reviewed in Chapter 2. Other potential merits of the async approach include adaptive voltage scaling [45], data-dependant operations [4], etc [38]–[44].

Despite these potential advantages, only a small number of async designs [38], [41]–[44] have been demonstrated to date. Arguably, the adoption of async approach remains stymied, to a large part, by their unavailability of advanced EDA tools (the async EDA tools are nascent when compared to sync EDA tools) and by the lack of established async library cells. Of the few async designs reported to date, some have indeed demonstrated superior (lower) power dissipation and higher speed attributes [4], [38], [41]–[44], [47]. However, many async designs have not shown to have improved attributes (over sync designs) [38], [46], [48]–[52] largely due to the 'unsophisticated' approach taken. 'unsophisticated' approach simply involves using standard sync circuits (using synchronous-based EDA tools and standard library digital cells) and modifying their input/output interfaces to satisfy the async signaling protocol. In view of this simple modification of sync circuits to make them asynchronous, such async designs are expected to be inefficient, resulting in high circuit overhead, hence higher power dissipation and slower speed.

The research work reported in this thesis is part of a larger Nanyang Technological University (NTU) research effort on async design, including the development of sophisticated async EDA tools (async design compiler [53]), async library cells, and the integration of the EDA tools and a cell library. The specific research effort in this PhD program delineated in this thesis pertains to an exploitation of the low power/energy attributes of the async approach to realize a relatively complex digital signal processing circuit (> 50K transistors) – an async FFT/inverse FFT (FFT/IFFT) processor for advanced audio devices including hearing aids. This research exercise involves the development of async library

cells with specific emphases on low voltage (1.1V-1.4V) and power-/energy-critical operations, and the design and handcrafting layout (fully and partially) of the async FFT/IFFT processor. This FFT/IFFT processor herein also serves as a benchmark for comparison when a later async FFT/IFFT processor is designed using the async tools (and the async library cells) that are currently developed by other members of the NTU async research team. For sake of clarity, note that in this thesis, two FFT/IFFT processors are designed, one sync and the other async. These are compared to determine the attributes of the sync and the async approaches.

# 1.2 Objectives

The overall objective of this thesis is to demonstrate the low power low energy attributes of the async approach (over the prevalent sync approach) in the design and realization of a low voltage low energy FFT/IFFT processor. The specifications of the FFT/IFFT processor are tabulated in Table 1.1.

Specifications

Wordlength

16-bit

Number of points

128-point

Operating voltage

1.1V – 1.4V

Energy dissipation

Speed performance

< 2.0ms per transform

IC Area

< 2mm² @ 0.35 µm CMOS process

TABLE 1.1 SPECIFICATIONS OF THE FFT/IFFT PROCESSOR

In view of the overall objective, the specific objectives are:

- (i) To design basic rudimentary low energy async microcells, including novel adders, an accumulator and a latch controller;

- (ii) To design specific macrocells, including multipliers and a memory; and

- (iii) To design an async FFT/IFFT processor (in part embodying the proposed microcells and macrocells). It is an objective to demonstrate that by means of the async approach, the async FFT/IFFT processor is more energy-efficient than its sync counterpart, specifically for low voltage low-to-medium speed (< 5MHz) energy-critical applications including hearing aids.

## 1.3 Contributions

The contributions of the work presented in this thesis pertain to circuit designs and async design techniques, and the design of several microcells and macrocells and

an async FFT/IFFT processor, all with emphases on low voltage operation and low energy dissipation. Of the microcells designed, the Latch Adder (LA), Latch Accumulator, *Type-\gamma* adder and Broad B latch controller arguably feature the most significant novelty. The async macrocells designed are a multiplier (embodying a novel multiplier core) and a memory. The async FFT/IFFT processor, in part, comprises these microcells and macrocells. The contributions in these proposed designs will now be described.

#### (i) Proposed microcell designs

#### (a) Latch Adder (LA)

The proposed LA is a latch-cum-adder design (an integrated latch and adder) whose novelty is the synchronization (in time) of its adder inputs (with different arrival times) by means of the integrated latch, thereby reducing spurious switching (see Chapters 3 and 4). Its primary attributes are lower energy dissipation, shorter delay and smaller IC area than the conventional adder with latches, which would otherwise comprise an independent adder and three independent latches.

#### (b) Latch Accumulator

The proposed Latch Accumulator is an accumulator comprising an LA as its core and an added latch. Its novelty is that the integrated LA can latch the output, hence only an added latch is required whilst the conventional accumulator would otherwise comprise an independent adder and two independent latches. Consequently, its primary attributes are slightly shorter

delay, lower energy dissipation and smaller IC area than the conventional accumulator.

#### (c) *Type-γ* adder

The proposed  $Type-\gamma$  adder is an async 2-bit carry completion sensing adder (CCSA) whose novelties are the employment of a transistor sharing technique in its Sum and Carry blocks, and an insertion of delay balancing transistors in its Carry block. It features comparable (slightly higher) energy dissipation to the lowest energy dissipation CCSA, the  $Type-\beta$  CCSA [54], [55], but is more robust (against delay variations) than the latter. The  $Type-\gamma$  CCSAs can be augmented with the author's earlier disclosed [54] less robust  $Type-\alpha$  CCSAs (see Chapter 3) to construct a longer wordlength adder. This augmentation results in shorter delay and lower energy dissipation (than an adder design comprising only  $Type-\gamma$  CCSAs) without compromising its delay robustness.

#### (d) Broad B latch controller

The proposed Broad B latch controller is an async latch controller in the broad data valid scheme (see Chapter 2). Its primary novelty is its assurance that the input signals are always successfully latched into the latches before it triggers the successive functional modules, thereby eliminating the possibility of malfunction of the functional modules. Unlike the proposed Broad B latch controller where there is no need to account for any delays to obtain this assurance, other conventional latch controllers may otherwise suffer from

malfunction unless sufficient delay is carefully inserted to accommodate the delays to properly trigger the successive functional modules.

#### (ii) Proposed macrocell designs

#### (a) 16×16-bit Booth array-based multiplier core

The proposed 16×16-bit Booth array-based multiplier core is a multiplier design based on the Booth algorithm and whose structure is the array structure. The primary novelties are the embodiment of the abovementioned proposed LAs and timing controls (by means of proposed delay line circuits), thereby significantly reducing the spurious switching (~ 62%) and hence, energy dissipation (~ 32%). A Singapore patent and a USA patent embodying the reduced spurious switching technique have been granted.

#### (b) Control-Multiplier

The proposed Control-Multiplier is an async  $16\times16$ -bit multiplier design and its primary novelties are added control circuits to specially compute trivial multiplications ( $\times$  1,  $\times$  -1, and  $\times$  0). The non-trivial multiplications are, as usual, computed by its multiplier core, the abovementioned Booth array-based multiplier core. The primary attribute of the Control-Multiplier is the further reduction in energy dissipation (22% reduction compared to the proposed  $16\times16$  multiplier core) by taking advantage of the fact that  $\times$  40% of the multiplications are trivial in the computation of the 128-point FFT algorithm.

#### (c) 128×16-bit memory design

The proposed 128×16-bit memory macrocell is a single-port async SRAM where several well-established low energy techniques including the partition of the memory into several sub-memory blocks are adopted. The primary novelty of the memory macrocell is the embodiment of a proposed Word Line Controller to activate the particular sub-memory block of interest and this prevents multiple assertions of unselected sub-memory blocks. This results in reduced energy dissipation.

#### (iii)Proposed async FFT/IFFT processor design

The proposed async FFT/IFFT processor is a dedicated audio processor to compute 128-point radix-2 decimation-in-time (DIT) FFT/IFFT algorithm. The async FFT/IFFT processor embodies established and proposed async microcells, and proposed macrocells. The primary novelty is its extremely low energy attribute (as benchmarked against reported designs to date). The slight drawbacks are a slightly larger IC area and an inconsequential longer delay (inconsequential due to the intended low speed hearing aid application).

The above contributions will be delineated in Chapters 3-5 and have been published in literature [56], [61]–[65] or accepted for publication [57], [58]. The summary of these published/accepted papers is delineated in pages 156 and 157 of this thesis.

11

Chapter 1 Introduction

1.4 Organization

The remainder of this thesis is organized as follows.

Chapter 2 reviews the literature of the work presented in this thesis and three

topics are reviewed. The first topic is a review of the mechanisms of power

(energy) dissipation in CMOS circuits, low power low energy design

methodologies, and noise margin analysis. The second topic is a review of sync

and async design approaches. The third topic is an overview of the FFT/IFFT

algorithm and this provides a preamble to the architecture adopted for the sync

and async realizations.

Chapter 3 describes the design of several proposed microcells, including a Latch

Adder, a Latch Accumulator, a  $Type-\gamma$  adder and a Broad B latch controller.

These microcells serve as basic building blocks for more complex designs,

including the designs delineated in Chapters 4 and 5.

Chapter 4 describes the two major async macrocells embodied in the proposed

async FFT/IFFT processor. The first async macrocell is an async multiplier

design, embodying a novel Booth array-based multiplier core and added control

circuits, specifically for the FFT algorithm. The second async macrocell is the

proposed async memory design and the techniques to obtain a low energy memory

design are presented.

Chapter 1 Introduction

12

Chapter 5 describes the design and implementation of the sync and the proposed async FFT/IFFT processors. The proposed async FFT/IFFT processor is thereafter benchmarked against the sync FFT/IFFT processor and against other reported designs to depict its attributes.

Chapter 6 concludes this thesis and provides recommendations for future research.

# Chapter 2

# **Literature Review**

The research work described in this thesis pertains to the design and realization of async circuits, ranging from microcells and macrocells and to a full FFT/IFFT processor. This chapter will review the literature pertaining to the research work herein. First, a review of low power low energy design techniques and noise margin analysis will be presented. An overview of the sync and async design approaches is thereafter reviewed followed by a review of the FFT/IFFT algorithm. Finally, a summary will be given.

# 2.1 Low Power Low Energy Design Techniques

Power (P) and energy (E) [20], [21] are two related figure-of-merits (see (2.1)) often used to qualify the power/energy parameter of digital circuits. This section reviews the mechanisms of power dissipation, discusses low power/energy design methodologies and provides noise margin analysis for the targeted application.

$$P = \frac{\partial E}{\partial t} \tag{2.1}$$

#### 2.1.1 Mechanisms of Power Dissipation

In digital CMOS circuits, there are four mechanisms of power dissipation [20], [21], [66] – the switching (dynamic) power ( $P_{\text{switching}}$ ), short-circuit power ( $P_{\text{sc}}$ ),

leakage power ( $P_{\text{leakage}}$ ), and static power ( $P_{\text{static}}$ ). These mechanisms are well established and well accepted.

Switching power ( $P_{\text{switching}}$ ) is dissipated during transistor switching events, when either charging the load/output capacitance  $C_{\text{L}}$  to  $V_{\text{DD}}$  or discharging the load/output capacitance  $C_{\text{L}}$  to ground, as depicted in Fig. 2.1. The switching power can be expressed analytically [20], [66] as:

$$P_{\text{switching}} = \alpha \cdot \frac{1}{T} \left[ \int_{0}^{T/2} V_{\text{out}} \left( -C_{\text{L}} \cdot \frac{\partial V_{\text{out}}}{\partial t} \right) \partial t + \int_{T/2}^{T} (V_{\text{DD}} - V_{\text{out}}) \left( C_{\text{L}} \cdot \frac{\partial V_{\text{out}}}{\partial t} \right) \partial t \right]$$

(2.2a)

$$= \alpha \cdot f \cdot C_{\text{L}} \cdot V_{\text{DD}}^{2}$$

where  $\alpha$  is the switching activity,

$C_{\rm L}$  is the load/output capacitance,

$V_{\rm out}$  is the output voltage,

$V_{\rm DD}$  is the supply voltage, and

$$f = \frac{1}{T}$$

, the switching frequency.

Fig. 2.1 Charging and discharging of a CMOS circuit during switching

For a well designed CMOS circuit based on non-deep-submicron processes, the switching power dissipation is usually dominant (e.g. 80% ~ 90% of the total power dissipation) [20]. However in deep-submicron processes [67], [68], the leakage power dissipation (see later) becomes increasingly significant. From (2.2b), it is apparent that the switching power dissipation can be reduced by reducing the switching activity, load/output capacitance, supply voltage, and the switching frequency.

Switching power dissipation in (2.2a) and (2.2b) can be re-expressed [20], [66] as switching energy required for operations within time T as:

$$E_{\text{switching}} = \alpha \cdot \left[ \int_{0}^{T/2} V_{\text{out}} \left( -C_{\text{L}} \cdot \frac{\partial V_{\text{out}}}{\partial t} \right) \partial t + \int_{T/2}^{T} (V_{\text{DD}} - V_{\text{out}}) \left( C_{\text{L}} \cdot \frac{\partial V_{\text{out}}}{\partial t} \right) \partial t \right]$$

(2.3a)

$$= \alpha \cdot C_{\rm L} \cdot V_{\rm DD}^{2} \tag{2.3b}$$

Short-circuit power ( $P_{sc}$ ) arises due to the short-circuit current,  $I_{sc}$ , when both the PMOS and NMOS transistors are simultaneously turned on. During this short transient interval,  $I_{sc}$  conducts from  $V_{DD}$  to ground. The short-circuit power dissipation can be expressed [20], [66] as:

$$P_{\rm sc} = I_{\rm sc} \cdot V_{\rm DD} \tag{2.4a}$$

$$\approx \frac{1}{12} \cdot k \cdot \tau_r \cdot f \cdot (V_{DD} - 2V_T)^3 \tag{2.4b}$$

where k is the transistor gain,

$\tau_r$  is the rise time (fall time) of the input, and

$V_{\rm T}$  is the threshold voltage of the transistors (assuming that  $|V_{\rm Tp}| = V_{\rm Tn}$ ).

From (2.4b), it is apparent that the short-circuit power dissipation can be minimized (almost negligible) when the supply voltage ( $V_{\rm DD}$ ) is close to  $2V_{\rm T}$  or less (i.e. no  $I_{\rm sc}$ ). Other factors such as the transistor gain, rise time, and switching frequency also influence the short-circuit power dissipation.

Leakage power ( $P_{\text{leakage}}$ ) arises when the quiescent (steady state) current flows from  $V_{\text{DD}}$  to ground even when the transistors do not conduct. The leakage power components [67], [68] include sub-threshold leakage, gate leakage, reversed-biased junction band-to-band-tunneling leakage, and others. For non-deep-submicron CMOS processes (e.g. feature size >  $0.18\mu\text{m}$ ), the leakage currents are typically in the order of nano amperes and can usually be neglected. However, if the transistors are of very short channel or nano-scaled lengths, the leakage current becomes significant (relative to switching power). The phenomena of leakage power dissipation [68] are well established and techniques to reduce leakage current are also well investigated and some techniques well established.

Static power ( $P_{\rm static}$ ) is dissipated only when a continuous current (not short-circuit current during the short transient interval) is established between  $V_{\rm DD}$  and ground. In contemporary static CMOS digital circuits (constructed by pull-up and pull-down networks), there is ideally zero static power dissipation. Other circuits such as ratioed logics [20] and analog circuits dissipate static power because a continuous current is needed to provide proper operation, usually for biasing conditions.

For the purpose of comparing different designs, a simplistic comparison based strictly on the power parameter may be a misleading metric if the performance or operating conditions of the circuits are not properly specified. This is because power is a time-averaged metric, and the reading of power dissipation can be increased or decreased by changing the time. In order to fairly compare the power dissipation of different circuits, the circuits have to be quantified for an equivalent (or similar) operation subject to delay constraints. In this respect, power and energy are similar. For a fair comparison, the other parameters such as process technology,  $V_{\rm DD}$  (if voltage is not used as a means for power/energy reduction) and other parameters have to be considered and accounted for accordingly.

In view of the above considerations, for the purpose of benchmarking the designs proposed in this thesis against reported designs, energy dissipation (as opposed to power dissipation) is used as a figure-of-merit. In most cases, the proposed designs are constructed and reported designs reconstructed for the same operations, fabricated using the same process technology, and simulated and measured under the same  $V_{\rm DD}$  and timing constraints. The  $\mu W/{\rm MHz}$  (equivalent to  $\mu W$  per million operations per second) or J (Joule) unit measure is used for qualifying the microcells and macrocells, and J unit measure is used for the FFT/IFFT processors (for one complete FFT/IFFT computation).

For completeness, the delay (computation time), energy-delay-product (EDP) [20], [69] and IC area are also used as figure-of-merits. The other prevalent figure-of-merit sometimes used in literature, power-delay-product (PDP) [20], however, is

not considered in this thesis. This is because PDP is usually interpreted as the average energy per switching event [20]. In this respect, the energy dissipation adopted is somewhat similar to PDP but the former is arguably more generic as it qualifies the circuits for a given operation that may comprise many switchings.

#### 2.1.2 Low Power/Energy Design Methodologies

The design methodologies for low power/energy dissipation span all levels of design, from the high level algorithm, architecture, circuit/logic down to the low level device/process parameters [18]–[23] as shown in Fig. 2.2.

Fig. 2.2 Power/energy methodology hierarchy

The algorithmic-level low power/energy design methodology generally includes a selection of data processing algorithms, specifically to minimize the computational complexity and switching events for a given task. For example, in this thesis, the FFT algorithm [25] is selected over the Discrete Fourier Transform (DFT) [24], and in other designs, considerations include algorithm transformations to match computational resources [21], etc. The architecture-level low power/energy design methodology generally includes smart power

management of the various system blocks [66], utilization of pipelining and parallelism [66], resource sharing [70], etc. The circuit-/logic-level low power/energy design methodology generally includes the proper choice of logic family (e.g. complementary static CMOS vs pass-logic vs dynamic logic [20], [70], [71]), synchronization (e.g. synchronous-logic vs asynchronous-logic [20], [38], [70]), glitch (spurious switching) reduction [70], operand isolation [72], etc. The device-/process-level low power/energy design methodology is often process technology related, including the threshold voltage, device geometries, interconnect properties, etc [21]. In short, a low power/energy design requires concurrent optimization at all levels, taking into consideration the interdependencies among these levels [23].

Many low power/energy techniques (including some of the abovementioned low power/energy methodologies) are employed in the design of the proposed microcells, macrocells and the async FFT/IFFT processor (in part embodying the microcells and macrocells). These techniques include low supply voltage ( $V_{\rm DD}$  = 1.1V – 1.4V), low leakage CMOS process, spurious switching reduction, async approach, FFT/IFFT algorithm, low speed and energy efficient architecture, low power standard library cells, etc. Similarly, the same low power/energy techniques (including the  $V_{\rm DD}$ , process technology, and the same low power standard library cells adopted in the async design) and clock-related low power/energy techniques (see later) are also applied to the sync FFT/IFFT processor (that serves as a benchmark for comparison).

It can be argued that a circuit operated @  $V_{\rm DD}$  = 1.1V - 1.4V is no longer considered a low voltage design because some current-art designs operate at  $\leq$  1V (e.g. circuits using 90nm CMOS process) and some designs even operate in the sub-threshold region (e.g. 0.3V) [9], [34]. However, due to cost and availability of fabrication process, the chosen CMOS process for this project is 0.35 $\mu$ m CMOS and the nominal  $V_{\rm DD}$  = 3.3V. The  $V_{\rm DD}$  of 1.1V - 1.4V, in the context of this fabrication process, is considered low voltage, and this voltage range is the typical low voltage operating range for hearing aid devices.

#### 2.1.3 Noise Margin

It is established that when  $V_{\rm DD}$  is low (for low voltage applications), the noise margin is somewhat degraded. Noise margin is a well-recognized problem and its analysis is well-established [20], and for simplicity, the noise margin low ( $NM_{\rm L}$ ) and the noise margin high ( $NM_{\rm H}$ ) are simplified as follows [20]:

$$NM_{\rm L} = V_{\rm H_{\rm L}} \ge V_{\rm Tn} \tag{2.5a}$$

$$NM_{\rm H} = V_{\rm DD} - V_{\rm IH} \approx V_{DD} - \left| V_{\rm Tp} \right|$$

(2.5b)

where  $V_{\rm IL}$  is input voltage low and  $V_{\rm IH}$  is input voltage high.

In this thesis, since  $V_{\rm DD}=1.1{\rm V}$  to 1.4V,  $V_{\rm Tn}\approx 0.5{\rm V}$  and  $|V_{\rm Tp}|\approx 0.7{\rm V}$  for the chosen  $0.35\mu{\rm m}$  CMOS process, the noise margins for the targeted hearing aid application can be determined. These are tabulated in Table 2.1.

0.5V

0.4V

THE CHOSEN  $0.35\mu$ M CMOS PROCESS  $V_{\rm DD}$   $NM_{\rm L}^*$   $NM_{\rm H}$ Minimum noise margin  $1.4{\rm V}$   $0.5{\rm V}$   $0.7{\rm V}$   $0.5{\rm V}$   $1.3{\rm V}$   $0.5{\rm V}$   $0.6{\rm V}$   $0.5{\rm V}$

0.5V

0.4V

TABLE 2.1 Noise Margins for the Targeted Hearing Aid Application in the Chosen  $0.35\mu\mathrm{m}$  CMOS Process

0.5V

0.5V

1.2V

1.1V

It is remarked that for the targeted application, the maximum tolerable noise (e.g. due to noise in the PCB, voltage variation, ambient noise, etc.) is < 140mV (10% of 1.4V). On the basis of Table 2.1, the minimum noise margin allowable is sufficient for the targeted application.

# 2.2 Synchronous-Logic and Asynchronous-Logic Design Approaches

This section will first review the sync design approach and then the async design approach. The sync and async design approaches are well-established in literature [20], [38].

## 2.2.1 Synchronous-Logic Design Approach

The sync approach uses a global clock (global synchronization) to synchronize digital circuits [20]. Fig. 2.3 depicts a basic structure of sync pipeline circuit and Table 2.2 tabulates timing notations.

<sup>\*</sup> Worst-case scenario

Fig. 2.3 A sync circuit

TABLE 2.2 TIMING NOTATIONS FOR THE SYNC CIRCUIT

| Symbol            | Notation                                                  |

|-------------------|-----------------------------------------------------------|

| $t_{ m logic}$    | maximum delay of the logic circuits                       |

| $t_{ m logic,cd}$ | contamination delay (minimum delay) of the logic circuits |

| $t_{ m reg}$      | maximum delay of the registers                            |

| $t_{\rm reg,cd}$  | contamination delay (minimum delay) of the registers      |

| $t_{ m setup}$    | setup time for the register                               |

| $t_{ m hold}$     | hold time for the register                                |

| $t_{ m clk1}$     | clock delay to the register A                             |

| $t_{ m clk2}$     | clock delay to the register B                             |

| T                 | clock period                                              |

Under the ideal condition when  $t_{\text{clk1}} = t_{\text{clk2}}$ , the proper operations of the sync circuits are constrained by the following expressions [20].

$$T \ge t_{\text{reg}} + t_{\text{logic}} + t_{\text{setup}}$$

(2.6)

$$t_{\text{reg,cd}} + t_{\text{logic,cd}} \ge t_{\text{hold}}$$

(2.7)

Equation (2.6) indicates that the clock period must be long enough for the data to propagate through the registers and logic (including all wire delays) and to be setup at the input registers before the next rising edge of the clock [20]. Equation (2.7) indicates that the hold time of the input registers must be shorter than the sum of the minimum delays of the logic circuits and registers [20]. These restrictions make the sync circuits easy to understand and design. This, in part, explains why most digital circuits are synchronous based.

However, in real-life, the clock signal is never ideal. As a result, two additional clock-related parameters, namely clock skew and jitter, need to be considered in the sync system. Clock skew is referred to as the spatial variation in arrival time of a clock transition on a circuit, and is caused by static mismatches in the clock paths and differences in the clock loads [20]. The clock skew makes the circuit more susceptible to race conditions, which may harm the correct operation of the system. In other words, the design of a low skew clock network is essential. The low skew clock network, however, usually requires a large number of clock buffers to balance the loads at different blocks and may result in higher power dissipation.

Clock jitter refers to the temporal variation of the clock period at a point on the circuit and the clock period may be reduced or expanded on a cycle-to-cycle basis [20] largely due to the process, temperature, and voltage variations. The clock jitter degrades the circuit performance (speed), and to some extent, it makes the inputs (to the combinational circuits) be less synchronous, resulting in spurious switching – hence, increased power/energy dissipation.

Many sophisticated sync EDA tools have been successfully developed to resolve these clock-related issues. For a design running at up to few hundred MHz clock frequency, commercial sync EDA tools (such as tools from Synopsys [36] and Cadence [35]) can easily accommodate these issues. However, for a design running at a very high frequency (e.g. > 1GHz), clock-related issues remain formidable.

To reduce the power/energy dissipation due to the clock in a sync design, two approaches, clock gating and multiple-clock, are widely used. The clock gating approach reduces the power/energy dissipation of the circuit when computation is not required for an extended period of time (idle state). It is a relatively simple concept, as shown in Fig. 2.4. If the functional modules (not shown) do not compute any computations, the *Enable* signal is disabled. As a result, the registers (and the associated functional modules) do not dissipate unnecessary switching power/energy.

Fig. 2.4 Clock gating approach

The multiple-clock approach can reduce the power/energy dissipation of the registers, especially if some of them need not to be clocked at a high frequency clock rate. The clock signals involve multiple sub-clock signals that are

synchronized by the master clock. Consider an example when there are 500 registers in a system and they are clocked @ master clock of 2MHz. There will be 1 billion register switching activities per second in the system. However, if 400 of them are clocked @ sub-clock of 1MHz (assuming the functionality is not affected), the register switching activities per second therein will be reduced from 1 billion to 0.6 billion, a significant improvement.

Although the abovementioned techniques to reduce power/energy dissipation are effective, the degree of reduction is somewhat constrained by the global clock infrastructure. The clock gating approach, to a large extent, can only be used in a course-grain manner, that is, only a portion of the whole system can be gated. The efficiency of the multiple-clock approach, to a large extent, strongly depends on the pipeline structure and signal flow adopted. However, these two techniques tend to create more skew problems, and in turn complicate the design of the clock infrastructure.

In Section 5.2 later, the sync FFT/IFFT processor that serves as a benchmarked design employs these two techniques for low power/energy dissipation.

### 2.2.2 Asynchronous-Logic Design Approach

The research work herein pertains to async designs with general objective of low voltage operation and low energy dissipation. This section serves to review four relevant topics, namely (i) fundamental concepts of async designs, (ii) async EDA tools, (iii) basic async microcells, and (iv) potential advantages of the async

Chapter 2 Literature Review

26

approach, and this review preambles the work presented in the subsequent chapters in this thesis.

#### 2.2.2.1 Fundamental Concepts of Asynchronous-Logic Design

In this subsection, four async fundamental concepts will be introduced, namely (i) delay models, (ii) handshaking protocols and channels, (iii) data encoding, and (iv) async pipelines.

#### (i) Delay Models

Depending on the timing assumptions made [38]–[40], async circuits can be classified by the delay models. The well accepted models are the delay-insensitive (DI), speed-independent (SI), and self-timed (ST) models.

A DI circuit is an async circuit whose functionality is unaffected by the gate delays and the interconnect wire delays. The assumptions here are that both the gate and wire delays are unbounded and arbitrary. The DI circuits are extremely robust for their delay insensitive property. However, these circuits are difficult to realize [73]. Another variation, called quasi-delay-insensitive (QDI), is also delay-insensitive if 'isochronic forks' is accounted for and is accommodated in the design. An isochronic fork is a forked wire where all the branches have the same delay.

An SI circuit is an async circuit whose functionality is unaffected by the delays in its components (e.g. gates). The assumptions here are that the gate delays are unbounded and arbitrary, and that the wire delays are zero. It is clear that the assumption that the ideal zero wire delay is unrealistic (with respect to gate delays), particularly where the relative wire delay is significant in deep-submicron processes. To accommodate this, the SI model has been extended with further assumptions [38] by lumping wire delays into the gate delays.

An ST circuit is an async circuit whose correct operation relies on engineering timing assumptions [38]–[40]. Of the engineering timing assumptions, the most prevalent assumption is arguably the bounded delay model. The bounded delay model is similar to the model used in sync circuits [38], [39]. In this model, the circuit assumes that both the gate and wire delays are known, or at least bounded. Hence, the completion signal (*COMP*) is designed to be generated using a delay line matched to the delay of the gates (including the wire delays), and this completion signal indicates the availability of the outputs of the circuits. Such 'matched-delay' async circuits are usually much simpler than the DI and SI circuits. However, the drawbacks are its worst-case operation and sensitivity to variations (e.g. voltage, temperature, fabrication process, and parasitic effects). For correct operation, the matched-delay components are designed to exceed the worst-case delay of the gates, usually a 5% – 30% safety margin for aggressive designs and > 100% safety margin for less aggressive designs [74], [75].

In this thesis, a hybrid approach, by both using DI and ST circuits, is adopted for the design of the async macrocells (Chapter 4) and async FFT/IFFT processor (Chapter 5). This hybrid approach is currently well-accepted and is adopted in many designs [4], [38].

#### (ii) Handshaking Protocols and Channels

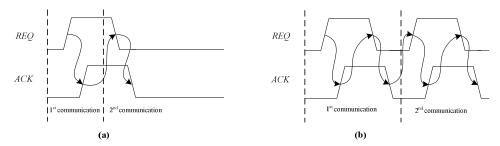

Async circuits operate according to a set of handshaking signals (the request (*REQ*) and acknowledge (*ACK*) signals) [38]–[40], [76]–[78]. In general, they can be classified into two handshaking protocols (two-phase and four-phase) as depicted in Fig. 2.5, and four different channels (nonput, push, pull, and biput) as depicted in Fig. 2.6.

Fig. 2.5 (a) Two-phase handshaking protocol, and (b) four-phase handshaking protocol

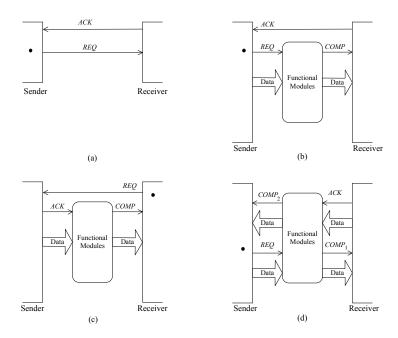

Fig. 2.6 Four channel types: (a) nonput, (b) push, (c) pull, and (d) biput

Figs. 2.5 (a) and (b) depict the two-phase and four-phase handshaking protocols respectively. The two-phase handshaking protocol is an edge-sensitive communication – any transition (rising or falling) on *REQ* or *ACK* is considered a valid communication. One complete asynchronous communication requires one transition on *REQ* and one corresponding transition on *ACK*. The four-phase handshaking protocol, on the other hand, is a level-sensitive communication. One complete asynchronous communication requires the assertion and deassertion on both the *REQ* and *ACK* signals.

In Fig. 2.6, there are two parties called the sender and receiver, and the black dot represents the active party that initials the *REQ* signal. Either the sender or receiver can be the active party. For the nonput channel type, no data is exchanged between the sender and receiver. For the push channel type, the sender pushes the data (by the *REQ* signal) to the receiver (via functional modules,

if any), and the receiver sends the *ACK* signal once it receives the data. For the pull channel type, the receiver pulls the data from the sender (via functional modules, if any), and the sender will acknowledge the data. For the biput channel type, the sender sends the *REQ* signal together with the data (via functional modules, if any) to the receiver, and the receiver sends the *ACK* signal together with another data (via functional modules, if any) to the sender.

The two-phase and four-phase handshaking protocols can be better interpreted depending on the assumptions of the data valid schemes (and the channel types) Figs. 2.7 (a) and (b) depict the data valid schemes for a push channel in [38]. two-phase and four-phase protocols respectively. In the two-phase handshaking protocol, when REQ is toggled, the data is available and remains valid until ACK is toggled to indicate the completion of the operation. In the four-phase handshaking protocol, there are four possible data valid schemes, namely early, broad, late, and broadish (extended early). In the early data valid scheme, the data is assumed to be valid when REQ is asserted until ACK is asserted. In the broad data valid scheme, the data is assumed to be valid when REQ is asserted until ACK is de-asserted. In the late data valid scheme, the data is assumed to be valid when *REQ* is de-asserted until *ACK* is de-asserted. In the broadish data valid scheme, the data is assumed valid when REQ is asserted until REQ is de-asserted. The data valid schemes for other channels (pull and biput) can be constructed accordingly and are well established [38].

Fig. 2.7 Push channel data valid schemes for (a) two-phase handshaking protocol, and (b) four-phase handshaking protocol

In this thesis, the four-phase handshaking protocol is adopted for the async macrocells and for the async FFT/IFFT processor due to its prevalence and due to its lower power attribute (over the two-phase protocol) [38], [51]. For simplicity and ease of testing, the push channel with broad and broadish data valid schemes is applied to the async macrocells and to the async FFT/IFFT processor.

#### (iii) Data Encoding

Async circuits are designed to detect the arrival time of data, that is, the data must be encoded with some timing information. For data encoding in async circuits, bundled data and dual-rail data [38] are commonly used.

The bundled data coding uses a bundle of data wires (each wire represents one-bit information) with two control wires, *REQ* and *COMP*, that indicate the timing

information. The bundled data coding is applicable to the bounded delay model discussed earlier.

The dual-rail coding uses two wires for one-bit information. One of the wires is dedicated as a 'TRUE' wire while the other one is dedicated as a 'FALSE' wire. Table 2.3 depicts the truth table for the dual-rail coding technique. Both wires cannot be '1' at the same time. Initially, both wires are '0' (no operation). Once an operation is asserted, only one of the wires can be '1', that is an event. The opposite logic states of the signals not only serve as logic information, but also detect the timing information simultaneously. The dual-rail coding technique is robust, and the circuits employing this technique can be delay-insensitive. However, this technique requires complementary signals which may increase the switching activity, and would require a larger IC area.

TABLE 2.3 DUAL-RAIL CODING

|              | TRUE wire | FALSE wire |

|--------------|-----------|------------|

| No operation | 0         | 0          |

| Logic '1'    | 1         | 0          |

| Logic '0'    | 0         | 1          |

| Not used     | 1         | 1          |

In this thesis, both the bundled data and dual-rail coding are adopted for the async FFT/IFFT processor. This hybrid approach is also well-accepted and adopted in many designs [4], [38].

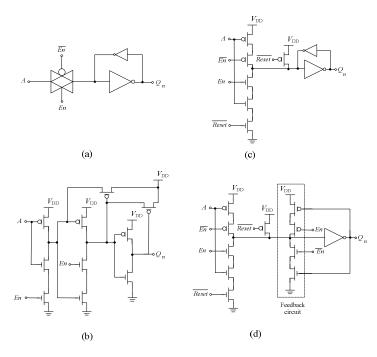

#### (iv) Asynchronous-Logic Pipelines

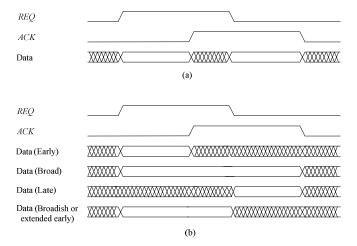

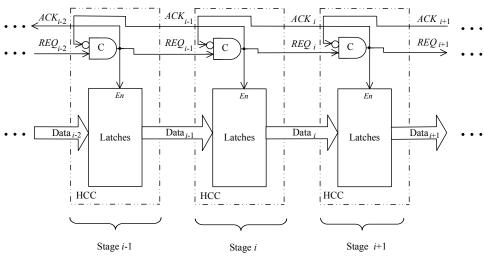

Fig. 2.8 depicts a conventional four-phase bundled data pipeline [38]. For simplicity and as an illustration, the circuit in Fig. 2.8 is the pipeline without data processing and functional modules (not shown) can be inserted between the latches in the consecutive stages for data processing.

HCC: Handshake control circuit

C: C-Muller gate

Fig. 2.8 A simple four-phase bundled data pipeline

In the four-phase handshaking protocol, either normally-closed or normally-opened latches [79], [80] can be used and the specific type affects the energy dissipation. Assuming that the initial handshaking signals are '0' and the normally-closed latches are used, when  $REQ_{i-2}$  is asserted,  $REQ_{i-1}$  (= $ACK_{i-2}$ ) will be asserted to open the latches in Stage i-1, and  $Data_{i-2}$  is passed to be  $Data_{i-1}$ . The  $ACK_{i-2}$  signal will acknowledge the receipt of the data to the preceding stage. The  $REQ_{i-1}$  signal will trigger the C-Muller gate in Stage i and  $REQ_i$  (= $ACK_{i-1}$ ) is

asserted to open the latches in Stage i, and Data $_{i-1}$  is passed to be Data $_i$ . The  $ACK_{i-1}$  signal will acknowledge the receipt of the data for Stage i-1, and  $REQ_{i-2}$  can be de-asserted, and the latches in Stage i-1 are then closed. Data $_{i-2}$  is now ready to be updated with new data. Thereafter,  $REQ_{i-1}$  (= $ACK_{i-2}$ ) is de-asserted to close the latches in Stage i, and Data $_{i-1}$  is ready to be updated (if only when  $ACK_i$  is asserted). At this time, a new operation can begin by asserting  $REQ_{i-2}$ . This scenario applies to the subsequent stages. Pipeline circuits embodying normally-opened latches can similarly be analyzed. The normally-closed latch approach is usually applied for reducing spurious switching (for low power/energy reduction) while the normally-opened latch approach, on the other hand, is usually applied for high speed operations [38], [79].

The two-phase bundled data pipeline is somewhat similar to the four-phase bundled data pipeline [38]. The pipeline structure in Fig. 2.8 is simple and features low throughput. More optimized and elaborate circuit implementations have been reported in literature [38].

In this thesis, for simplicity, testability, and low energy dissipation, the four-phase pipeline (with the broad and broadish latch controllers) and the normally-closed latch approach are adopted for the async FFT/IFFT processor design.

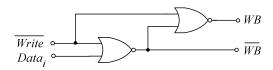

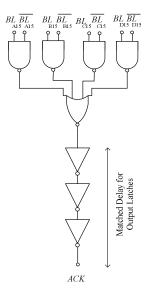

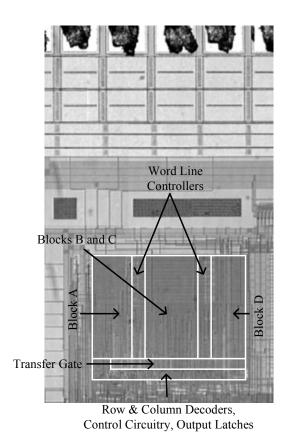

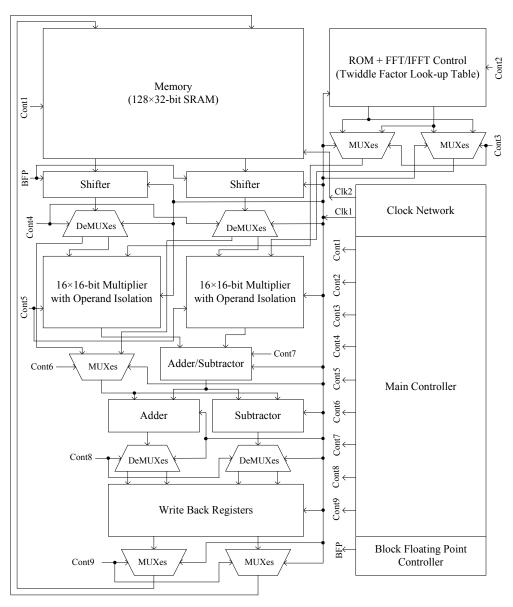

#### 2.2.2.2 Asynchronous-Logic EDA Tools