## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# A low voltage low power highly linear CMOS quadrature mixer using transconductance cancellation technique

Yeo, Kiat Seng; Wang, Keping; Ma, Kaixue; Ye, Wanxin; Zhang, Hao; Wang, Zhigong

2012

Wang, K., Ma, K., Ye, W., Yeo, K. S., Zhang, H., & Wang, Z. (2012). A low voltage low power highly linear CMOS quadrature mixer using transconductance cancellation technique. In 2012 IEEE MTT-S International Microwave Symposium Digest, pp.1-3.

https://hdl.handle.net/10356/79646

https://doi.org/10.1109/MWSYM.2012.6258257

© 2012 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. The published version is available at: [DOI: http://dx.doi.org/10.1109/MWSYM.2012.6258257].

Downloaded on 09 Apr 2024 14:10:02 SGT

## A Low Voltage Low Power Highly Linear CMOS Quadrature Mixer Using Transconductance Cancellation Technique

Keping Wang<sup>1</sup>, Kaixue Ma<sup>1</sup>, Wanxin Ye<sup>1</sup>, Kiat Seng Yeo<sup>1</sup>, Hao Zhang<sup>2</sup>, Zhigong Wang<sup>2</sup>

1 VIRTUS, IC Design Centre of Excellence, Nanyang Technological University, 639798, Singapore

2 Institute of RF- & OE-ICs, Southeast University, Nanjing, 210096, China

Abstract — This paper presents a low voltage low power high linearity quadrature mixer for software defined radio applications in a 90nm CMOS technology. A 7-dB improvement of input-referred  $3^{\rm rd}$ -order intermodulation point (IIP $_3$ ) is achieved by using a differential  $g_{\rm m}$ " (the second derivation of transconductance) canceling technology. The negative value of  $g_{\rm m}$ " in saturated pseudo differential transistor (PDT) is compensated by the positive value of PDT in subthreshold region. The even-order distortion is eliminated by differential PDTs. The mixer consumes a dc power of only 3.8 mW under 1V supply. The conversion gain with 10 samples is 3.6~7.2 dB in the frequency range of 0.3~6 GHz. The IIP $_3$  is 7.9~12.3 dBm 0.3~6 GHz, whereas the single-sideband noise figure (SSB NF) is 11.1~14.7 dB.

Index Terms — Mixer, low voltage, low power, high linearity, pseudo differential transistor (PDT), CMOS; software defined radio (SDR).

## I. INTRODUCTION

Since the energy-efficiency software radio is still a great challenge in a long time. The most practical solution is reconfigurable RF front-ends can be widely programmed to operate with all present and future standards [1], [2]. The RF front-end must be very flexible, to serve all communication standards in a cost-efficiency way. These standards include wireless local personal networks (e.g. Bluetooth), wireless local area networks (e.g. WLAN 802.11a, b, g, j, n), cellular networks (e.g. GSM, UMTS), digital broadcasting (e.g. DAB, DVB-TH), and positioning systems (e.g. GPS). As the required receiver needs to deal with the signals with input frequency from tens of MHz up to several GHz, nonlinearity may cause many problems, such as harmonic distortions, gain compression, blocking, cross modulation and intermodulation, etc. The even-order distortion can easily be reduced by using differential signal process, but it is very difficult to reduce the odd-order distortions. The 3<sup>rd</sup>-order inter-modulation distortion IM3 is the most dominant nonlinearity component. The linearity performance of mixer is expressed by the input-referred 3<sup>rd</sup>-order inter-modulation point (IIP<sub>3</sub>) divided by the DC power consumption P<sub>DC</sub> (IIP<sub>3</sub>/P<sub>DC</sub>). The IIP<sub>3</sub> is usually proportional to P<sub>DC</sub>. Therefore, it is a great challenge to increase IIP<sub>3</sub>/P<sub>DC</sub> for low power SDR systems.

In order to maximize the IIP<sub>3</sub>/P<sub>DC</sub>, some linearity improvement techniques are employed [3]-[5]. Most of them are based on negative feedback circuit using degeneration by resistors and inductors. Although the IIP<sub>3</sub> is enhanced by this method, it suffers from gain reduction. The passive mixer can provide high IIP<sub>3</sub>, but it suffers from the large conversion loss. Single-ended multiple gated transistors (MGTR) can be used to cancel the  $g_{\rm m}$ " in amplifier [6], however, it suffer from high even-order distortion. A transconductance linearization technique called differential multiple gated transistors (DMGTR) has been used to improve the  $IIP_{\gamma}/P_{DC}$  in programmable gain amplifier design [7]. The negative value of  $g_{\rm m}$ " which degrades the linearity in fully differential transistors (FDT) can be compensated with a positive value of  $g_m$ " in pseudo differential transistors (PDT). However, for FDT, there must be four-stage components stacked from power supply to ground, including tail current source,  $g_{\rm m}$  stage, switch stage, and load. This makes low-voltage low-power design unattainable.

In this paper, a low voltage low power IIP<sub>3</sub> improved quadrature down-conversion mixer with differential PDTs working in saturated and subthreshold region is present. With differential PDTs, high even-order distortion and large power consumption issues in previous work [6], [7] can be solved. To our best knowledge, this is the first paper simultaneously achieving low voltage low power high linearity performances with proposed differential PDTs.

### II. MIXER DESIGN

Generally, the non-linearity of mixer is mostly caused by the input transconductance cell. Unlike the large signal distortion caused by gain compression which can be eliminated by the automatic gain control (AGC) loop, the small signal non-linearity will greatly affect the quality of wanted signal. The  $g_m$ " which is inversely proportional to the IIP<sub>3</sub> is introduced to evaluate the small signal non-linearity [8]. The IIP<sub>3</sub> of the device can be improved by reducing  $g_m$ " effectively.

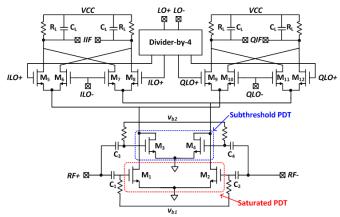

The schematic of proposed quadrature mixer is shown in Fig.1. The input transconductance cell consists of two PDTs,  $M_1$ - $M_4$ .  $M_1$  and  $M_2$  is biased in saturation region by  $v_{b1}$ , while the  $M_3$  and  $M_4$  is biased in the subthreshold region by  $v_{b2}$ .  $M_5$ - $M_{12}$  are switch cells connected to quadrature LO and IF. The I

Fig. 1. Schematic of proposed quadrature mixer

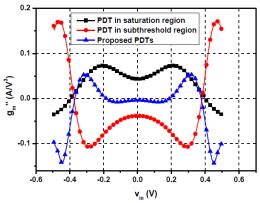

Fig. 2. g<sub>m</sub>" versus differential input voltage in the PDTs

and Q switch cells share one transconductance cell to decreasing the power consumption. The load  $R_L$  and  $C_L$  is designed to achieve proper gain as well as filtering the high frequency harmonics at the IF frequency. Neglecting channel-length modulation effect, the drain current  $I_D$  of  $M_1$  and  $M_2$  shows square low to  $V_{GS}$ ,  $I_D = (\mu_n C_{ox}/2) \times (W/L) \times (V_{GS} - V_{TH})^2$ . For small signal linearity consideration, while  $v_{in} = 0$ , the  $g_m$ " is given as:

$$g_m "|_{\Delta v_{in}=0} = \frac{-3}{4\sqrt{I_{SS}}} \left( \mu_n C_{ox} \frac{W}{L} \right)^{\frac{3}{2}} < 0$$

(1)

where the  $v_{\rm in}$  equals to  $v_{\rm RF+}$ - $v_{\rm RF-}$ . The  $\mu_{\rm n}$  and  $C_{\rm ox}$  is process related parameters.  $I_{\rm ss}$  is the total current of PDT M<sub>1</sub> and M<sub>2</sub>.

Then assume the voltages at the PDT  $M_3$  and  $M_4$  are  $v_{b2}\pm\Delta v_{in}/2$ , where  $v_{b2}$  is bias voltage and  $\Delta v_{in}$  is small signal voltage. Since the current of MOSFET in subthreshold region is  $I_D=I_0e(v_{GS}/\xi V_T)$ , where  $\xi>1$  is a non-ideal factor,  $I_0$  is a parameter related to process,  $V_T$  is thermal voltage. For small signal linearity consideration, while  $v_{in}=0$ , the  $g_m$ " is given as:

$$g_m"|_{\Delta v_{\rm in}=0} = \frac{I_0}{4(\xi V_{\rm T})^3} e^{\frac{v_{\rm b}}{\xi V_{\rm T}}} > 0$$

(2)

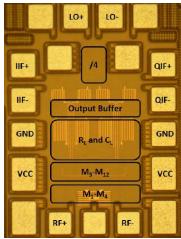

Fig. 3. Microphotograph of quadrature mixer

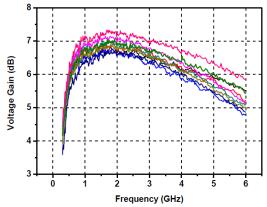

Fig. 4. Measured voltage gain (10 samples)

According to equation (1) and (2), by adjusting W/L and bias voltage  $v_{b1}$  and  $v_{b2}$  in PDT,  $g_m$ " can be set to nearly zero. Consequently, the highest IIP<sub>3</sub> can be achieved. Compared to the previous work [6]-[9], transconductance cancellation condition can be easily established by hand calculation instead of simulation.

The transistor size of  $M_1$  and  $M_2$  is set to be  $15\mu\text{m}/0.1\mu\text{m}$ , and the size of  $M_3$  and  $M_4$  is  $38\mu\text{m}/0.1\mu\text{m}$ . The current of saturation PDT is 3.5 mA, while the current of subthreshold PDT is 80  $\mu$ A. And, the  $g_m{}''$  for saturation PDT and subthreshold PDT is approximate -0.04A/V<sup>3</sup> and 0.04A/V<sup>3</sup>.

Fig.2 shows the simulated  $g_m$ " versus differential input voltage in the PDTs. In small signal operation region, the negative value of  $g_m$ " which degrades the linearity in saturation PDT can be compensated with a positive value of  $g_m$ " in subthreshold PDT. Since the performance of mixer mainly depend on saturation PDT, the linearity is greatly improved by this method without sacrificing other performance like NF, gain, and power consumption.

### III. IMPLEMENTATION AND MEASUREMENT RESULTS

The mixer was fabricated in a low-cost 90-nm CMOS process. The microphotograph of the fabricated LNA is shown

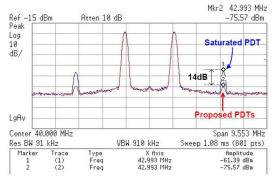

Fig. 5. Measured result of two-tone intermodulation test

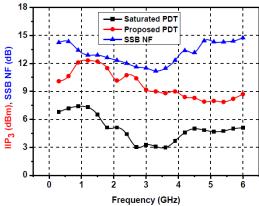

Fig. 6. Measured IIP3 improvement and SSB NF

in Fig. 3. All pins are ESD-protected using PN diodes. The dimension of the chip including PAD is  $640\mu m\times 450\mu m$ . The VCC is feed to the chip symmetrically to decrease the imbalance of I and Q mixer. A divider-by-4 circuit is designed to convert the differential LO signal to the quadrature signals. The total DC power consumption is 3.8 mW under 1V supply.

Fig.4 shows the measure voltage gain with 10 samples. The maximum gain is 7.2 dB at 1.7 GHz, and the minimum gain is 3.6 dB at 300MHz. The 3dB gain bandwidth for each sample can easily cover the interested 300MHz to 6GHz frequency range. The gain reduction in low frequency band is caused by the on-chip BIAS-T at input. The capacitors in BIAS-T can't be designed large enough for the area limitation. Because of C<sub>gs</sub> and C<sub>gd</sub>, the gain drops at high frequency. Fig.5 shows the measurement result of two-tone intermodulation test. With a similar fundamental power, the proposed mixer decrease the IM<sub>3</sub> power up to 14 dB, and the corresponding IIP<sub>3</sub> improvement is 7 dB. Fig.6 shows the IIP<sub>3</sub> improvement and SSB NF measurement results. At least 3.1 dB IIP<sub>3</sub> improvement is obtained in the frequency range 0.3-6GHz, the maximum IIP<sub>3</sub> improvement is 7.1 dB at 2.7GHz. The measured SSB NF is 11.1-14.7 dB at 0.3-6GHz. The measured performance of is summarized in Table I. Other previously published papers are also included for comparison. The mixer's figure of merit (FOM) can be expressed as [9]:

$$FOM = 10\log\left(10^{G/20} \times 10^{\left(IIP_3 - 10\right)/20} / \left(10^{NF/10} \times P\right)\right)(3)$$

TABLE I

PERFORMANCE COMPARISONS

| Reference                                        | This Work | [9]       | [10]              | [11]     |

|--------------------------------------------------|-----------|-----------|-------------------|----------|

| Frequency range(GHz)                             | 0.3-6     | 0.5-7.5   | 0.2-2             | 2-11     |

| Voltage gain(dB)                                 | 3.6-7.2   | 5.7       | 19                | 6.9      |

| IIP <sub>3</sub> (dBm)                           | 7.9-12.3  | -5.7      | 11                | 6.5      |

| SSB NF(dB)                                       | 11.1-14.7 | 15        | 6.5               | 15.5-20  |

| $I_{DD}$ (mA)/ $V_{DD}$ (V)                      | 3.8/1     | 0.62/0.77 | 50/1.2            | 14.2/1.8 |

| IQ imbalance $\Delta$ mag(dB)/ $\Delta$ phase(°) | 0.2/1     | NA        | NA                | NA       |

| Chip Area/mm <sup>2</sup>                        | 0.29      | 0.62      | 0.13 <sup>a</sup> | 0.48     |

| Technology                                       | 90-nm     | 0.18-μm   | 65-nm             | 0.18-μm  |

| IIP <sub>3</sub> /P <sub>DC</sub>                | 4.46      | 0.56      | 0.21              | 0.17     |

| FOM                                              | 17.8      | 13.2      | 15.7              | 3.9      |

<sup>&</sup>lt;sup>a</sup> Active core area exclude the Bias and LO generation and buffers.

It is observed that the mixer in this work, compared to the other state-of-the-art CMOS mixer, has achieved highest  $IIP_3/P_{DC}$ , and FOM, with smallest chip area.

### IV. CONCLUSION

A low voltage low power high linearity quadrature mixer in a 90nm CMOS is present. It covers most recent used commercial frequency band from 300MHz to 6GHz with 7dB IIP<sub>3</sub> improvement. The proposed mixer has excellent performance in comparison with other CMOS mixers.

### REFERENCES

- [1] A Abidi, "The Path to the Software-Defined Radio Receiver", *IEEE J. Solid-State Circuits*, vol 42, pp 954-966, 2007.

- [2] B. Razavi, "Cognitive Radio Design Challenges and Techniques", *IEEE J. Solid-State Circuits*, vol 45, pp 1542-1553, 2010.

- [3] V Aparin, P Burton. "Modified Derivative Superposition Method for Linearizing FET Low-noise Amplifier", IEEE Trans on Microwave Theory and Techniques, vol 53, pp 571-581, 2005.

- [4] Y. Kim, Y. Kim, and S. Lee, "Linearized Mixer Using Predistortion Technique", *IEEE Microw. Wireless Compon. Lett.*, vol. 12, pp.204-205, 2002.

- [5] I. Kwon and K. Lee, "An Integrated Low Power Highly Linear 2.4-GHz CMOS Receiver Front-end Based on Current Amplification and Mixing", IEEE Microw. Wireless Compon Lett., vol. 15, pp. 36–38, 2005

- [6] T Kim, B Kim, K Lee. "Highly Linear Receiver Front-end Adopting MOSFET Transconductance Linearization by Multiple Gated Transistors". IEEE J. Solid-State Circuits, vol 39, pp 223-229, 2004.

- [7] T Kim, B Kim. "A 13-dB IIP3 improved low-power CMOS RF programmable gain amplifier using differential circuit transconductance linearization for various terrestrial mobile D-TV applications". *IEEE J. Solid-State Circuits*, vol 41: pp. 945-953, 2006.

- [8] K Liang et al, "A New Linearization Technique for CMOS RF Mixer Using Third-Order Transconductance Cancellation", *IEEE Microw. Wireless Compon. Lett*, vol 18, pp 350-352, 2008.

- [9] K Liang et al, "A 0.5–7.5 GHz Ultra Low-Voltage Low-Power Mixer Using Bulk-Injection Method by 0.18-µm CMOS Technology", *IEEE Microw. Wireless Compon. Lett*, vol 17, pp 531-533, 2007.

- [10] M Soer, E Klumperink, Z Ru, "A 0.2-to-2.0 GHz 65 nm CMOS receiver without LNA achieving >11 dBm IIP3 and <6.5 dB NF", ISSCC Dig. Tech. Papers, pp 222-224, 2009.

- [11] P Rao, et al, "A Ultra-Wideband High-Linearity CMOS Mixer With New Wideband Active Baluns", *IEEE Trans on Microwave Theory and Techniques*, vol 59, pp 2184-2192, 2009.