# This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# An energy-aware CMOS receiver front end for low-power 2.4-GHz applications

Do, Aaron V.; Boon, Chirn Chye; Do, Manh Anh; Yeo, Kiat Seng; Cabuk, Alper

2010

Do, A. V., Boon, C. C., Do, M. A., Yeo, K. S., & Cabuk, A. (2010). An energy-aware CMOS receiver front end for low-power 2.4-GHz applications. IEEE transactions on circuits and systems Part I: Regular papers, 57(10), 2675-2684.

https://hdl.handle.net/10356/92396

https://doi.org/10.1109/TCSI.2010.2047750

© 2010 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. The published version is available at: [DOI: http://dx.doi.org/10.1109/TCSI.2010.2047750].

Downloaded on 09 Apr 2024 10:52:11 SGT

# An Energy-Aware CMOS Receiver Front End for Low-Power 2.4-GHz Applications

Aaron V. Do, *Member, IEEE*, Chirn Chye Boon, *Member, IEEE*, Manh Anh Do, *Senior Member, IEEE*, Kiat Seng Yeo, *Member, IEEE*, and Alper Cabuk, *Member, IEEE*

Abstract—A receiver front end designed in 0.18- $\mu$ m CMOS consisting of a low-noise amplifier and IQ mixers is presented. The front end's power consumption is controllable from 5.0 down to 1.4 mA. It is proposed to push the receiver requirements to the front end in order to efficiently control the overall power consumption based on the real-time required noise performance. We show that, under good channel conditions, this front end can save up to 70% of its nominal power consumption.

*Index Terms*—CMOS RF integrated circuits, low power, RF front end, system on chip (SoC)

#### I. INTRODUCTION

HE LAST decade has seen the near complete integration of the wireless transceiver, and the rise of CMOS as the choice technology in consumer-based wireless applications such as mobile phones and wireless local area networks (WLANs). Full system integration continues to be a topic of interest in the research field in order to minimize both the cost and the form factor of wireless transceivers. However, a new trend is emerging in RFIC system-on-chip (SoC) design.

In the interests of longer battery life, ultralow-power design has recently become a hot topic for applications such as wireless personal area networks (WPANs) and wireless sensor nodes. The IEEE 802.15.4 standard has been specifically designed to cater to this demand. Transceivers that follow this standard have been designed to operate using less than 10 mA of dc current [1]. These designs have relied on simplified circuit configurations to minimize power consumption [1]–[5]. Despite their relative successes, we believe that significantly more power consumption can be saved by both further simplifying the circuit structures and dynamically adjusting the performance of the receiver (RX). The latter method is termed energy-aware design, and our proposed energy-aware scheme was introduced in [6].

While a radio is designed around its sensitivity, it normally operates under significantly better conditions. The average path loss varies depending on the environment, the availability of line of sight, and the distance between the RX and transmitter (TX), among other things [7]. An energy-aware transceiver adjusts its performance according to the amount of received signal strength and uses the optimum power to receive the signal in a given situation.

Manuscript received December 09, 2009; revised February 12, 2010; accepted March 17, 2010. The work was supported by MediaTek Inc., Singapore. This paper was recommended by Associate Editor A. Demosthenous.

The authors are with Nanyang Technological University, Singapore 639798 (e-mail: doaaron@ntu.edu.sg).

Digital Object Identifier 10.1109/TCSI.2010.2047750

This paper presents the implementation of an energy-aware RX front end for low-power low-data-rate applications. We propose to dynamically control the power consumption of an RX front end based on the real-time required noise figure (NF). As a basis for comparison, we will design around the IEEE 802.15.4 standard, which operates in the 2.4-GHz industrial, scientific, and medical band. We focus on the design of the RX front end, which generally consumes a large portion of the total RX power. The standard features relaxed requirements in terms of interference rejection and noise performance, which simplifies front-end design and will allow us to implement dynamic power control circuitry.

Section II will discuss energy-saving schemes and compare the proposed energy-aware scheme to state-of-the-art methods. Section III will discuss the distribution of power consumption in an RX and how much power can practically be saved. Section IV will present the receiver design methodology and details of the individual circuit blocks. Section V will present measured results, and Section VI will conclude our work.

#### II. ENERGY-SAVING SCHEMES

# A. Proposed Energy-Aware Design

The proposed energy-aware scheme involves adjusting the RX front end's power consumption based on its *in situ* required NF. While the final design merit for an RX is its bit error rate (BER), RFIC designers generally split up the performance requirements into nearly independent specifications. In general, signal nonidealities arise due to linear distortion [8], interference, and random noise.

An example of linear distortion is nonideal filtering. In general, RF components such as the low-noise amplifier (LNA) and the downconversion mixer produce scarce linear distortion as they are generally designed to pass a much greater bandwidth than the signal bandwidth. For example, an IEEE 802.15.4 front end must pass the entire 83.5-MHz system bandwidth where the signal bandwidth is only 2 MHz [1].

The effect of interference on a signal's quality is described by the RX mth-order intercept (IIP $_n$ ), phase noise, image rejection ratio (IRR), and 1-dB gain compression ( $P_{1\text{-}dB}$ ). Such performance parameters are not suitable for energy-aware control for several reasons. Starting with linearity, we note that IIP $_n$  and  $P_{1\text{-}dB}$  are linked, and in principle, the  $P_{1\text{-}dB}$  is approximately 9.6 dB lower than the IIP $_3$  [9]. As the received signal strength increases, the required gain of the system drops. Reducing the system gain generally improves both its IIP $_n$  and  $P_{1\text{-}dB}$ . However, the required IIP $_n$  reduces, making it impractical to control. Phase noise is a parameter of the frequency synthesizer whose power consumption is impractical to control without affecting

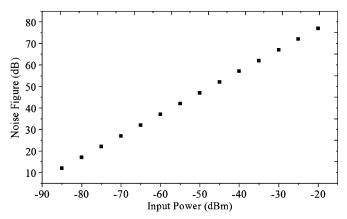

Fig. 1. Tolerable NF versus received input power for the IEEE 802.15.4 standard.

the loop dynamics of the frequency synthesizer. Lastly, IRR is determined by the matching between the I and Q paths and is not directly related to RX power consumption.

NF on the other hand is directly related to the RX power consumption. The input-referred noise of a MOSFET is approximately given as follows (only channel noise is considered):

$$V_{n,\text{in}}^2 \approx \frac{4kT\gamma\Delta f}{\alpha g_m}$$

(1)

where k is Boltzmann's constant, T is the temperature in Kelvin,  $\gamma$  is a parameter approximately equal to 2/3 in saturation for long-channel devices,  $\alpha$  is the ratio of  $g_m$  to the transconductance when the drain–source voltage is zero, and  $g_m$  is the device transconductance [10]. Since  $g_m$  improves with current consumption

$$g_m = \sqrt{2\mu_0 C_{\rm ox} \frac{W}{L} I_{\rm DS}} \tag{2}$$

where  $\mu_0 C_{\rm ox}$  is process dependent, W/L is the aspect ratio, and  $I_{\rm DS}$  is the drain–source current; current consumption can be directly linked to NF. NF is also indirectly related to current consumption through the gain of a cascaded system. The cascaded NF can be calculated as follows:

$$F_{\text{total}} = F_1 + \frac{F_2 - 1}{G_1} \tag{3}$$

where  $F_{\rm total}$  is the noise factor of the system,  $F_1$  is the noise factor of the first stage,  $F_2$  is the combined noise factor of all subsequent stages, and  $G_1$  is the power gain (which is proportional to the square of the voltage gain) of the first stage. When  $F_1$  is small compared to  $F_{\rm total}$ ,  $F_{\rm total}$  is inversely proportional to the first stage's squared gain. Assuming that we have a common-source LNA representing  $G_1$ , its voltage gain is proportional to the square root of the current consumption, and therefore,  $F_{\rm total}$  is inversely proportional to the current consumption.

The tolerable system NF of an IEEE 802.15.4 RX is shown versus the received signal strength in Fig. 1 and is based on system simulations in [11], which include the effects of a multipath environment. The BER of the system is directly related to the received SNR and, hence, the system NF. In practice, we can also expect the curve to slightly deviate due to the finite output SNR of the transmitter.

Our discussion suggests that, while an ideal energy-aware RX would be able to independently control its noise and interference performance, a suboptimal design should be able to control its noise performance without degrading its interference performance.

## B. Alternate Energy-Aware Design

An energy-aware method involving control of a transceiver's power consumption based on the required error vector magnitude (EVM) was proposed in [12]. The principle behind the choice of EVM as a performance measure is its strong correlation to BER. The authors proposed to control the EVM by controlling the biasing and power supply of the RF front end. However, in [12], no attempt to independently treat noise and interference was made. This method would therefore be suboptimal in situations where noise performance is good but interference performance is poor (or vice versa) since the EVM would reflect the poorer of the two kinds of performance. As discussed in the previous section, we advocate a 2-D approach to energy-aware design. However, in this paper, we concentrate solely on adjusting the RX noise performance.

## C. Variable-Data-Rate Standards

Certain standards such as the mobile WiMax [13] standard support multiple data rates. When channel conditions are good, the receiver can switch to a higher data rate modulation scheme, and therefore, for the same amount of data, the transceiver is on for a shorter duration. Unfortunately, the channel conditions must be simultaneously good in terms of both noise and interference in order for the transceiver to communicate at higher data rates. The proposed energy-aware method does not suffer such limitations.

#### D. Other Energy-Saving Schemes

Two other interesting methods for saving power in RX design are the wake-up RX (WuRX) [14], [15] and energy harvesting [16]. Because an RX generally does not know when it will receive a signal, it is normally on. If the device only receives information for a small period of the time that it is on, then a lot of power is wasted. One method to get around this problem is to use a WuRX. The WuRX has been studied in [14] and [15] for use in wireless sensor nodes where the role of the WuRX is implied in its name. Another possible energy-saving scheme is to use energy harvesting. An obvious energy-harvesting scheme is to use solar cells to power the RX. However, it is potentially cost saving to harvest electromagnetic energy if an external battery can be avoided. This was used in [16] to power a demodulating circuit for wireless sensor nodes. Intuitively, both of these energy-saving schemes can be used in conjunction with the energy-aware design.

It is well known that the gain requirement scales with input power, and this fact was exploited in [17] to scale the power consumption of the receiver with the gain requirement. However, the additional link between NF and input power proposed here was not made. The authors in [17] also proposed an ultralow start-up time in order to minimize the total energy used by a receiver.

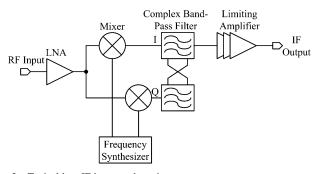

Fig. 2. Typical low-IF integrated receiver.

#### III. PRACTICAL ENERGY-AWARE LIMITATIONS

A typical low-IF integrated receiver is shown in Fig. 2. Energy-aware receiver design relies on a receiver's ability to regulate its power consumption based on the *in situ* required specifications. However, any practical receiver design has overhead power requirements that can be considered fixed. For example, the power consumption of the frequency synthesizer has little correlation with the overall NF of the receiver. Although we can conceivably adjust the frequency synthesizer's output power based on the required NF, there is still a minimum power consumption required by such circuit blocks as the frequency dividers and phase-frequency detector. The goal of the receiver designer should therefore be to minimize the overhead power consumption and try to compensate for the degraded noise performance using blocks whose noise performance heavily depends on power consumption.

This leads to our proposed design methodology. By pushing the requirements of the receiver to the front-end LNA, we can increase the amount of controllable power consumption in the receiver. This obviously leads to a more energy-aware design. In order to push the requirements to the LNA, the LNA must be able to provide a high voltage gain. Furthermore, in order to compensate for the high LNA gain, all subsequent blocks up to and including the channel-select filter must exhibit high linearity. High linearity can be achieved in the downconversion and channel filtering stages by using passive mixers and active-RC filtering [1].

The biggest limitation on the controllability of the receiver power consumption is in the power consumption required by the frequency synthesizer. In [1] and [18], the frequency synthesizer required 9.72 and 12 mW, respectively, while in [19], it required just 2.4 mW. All frequency synthesizers were designed using CMOS for the IEEE 802.15.4 standard, but [1] and [18] used 0.18- $\mu$ m technology, and [19] used 0.13- $\mu$ m technology. Improving technology and frequency synthesizer architectures can therefore lead to very low power overhead for the frequency synthesizer.

Another required power overhead is due to the bandwidth requirements of the op-amps used in the channel filter. In order to prevent intermodulation of high-frequency interferers, the channel filter must be linear over the entire system bandwidth, which is 83.5 MHz in the case of the IEEE 802.15.4 standard [20]. This system bandwidth directly reflects on the bandwidth requirements of the op-amps.

Last, there is some power overhead required by support blocks such as bandgap references and calibration circuitry.

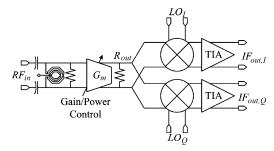

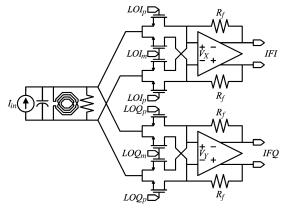

Fig. 3. Model of the proposed RF front end. The LO is supplied by an external signal generator.

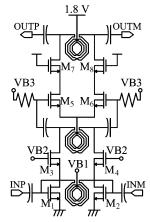

Fig. 4. Proposed energy-aware LNA with biasing shown. The biasing voltages are fed from current mirrors.

# IV. FRONT-END DESIGN AND ANALYSIS

A model of the proposed energy-aware front end is shown in Fig. 3. The LNA consists of a step-up impedance transformer followed by a variable-gain/power transconductor. The transconductor is loaded by the output impedance of the LNA and the input impedance of the quadrature passive mixers. The quadrature passive mixers provide current-mode outputs to a pair of op-amp-based transimpedance amplifiers (TIAs).

The local oscillator (LO) signal is split into I and Q phases using a two-stage polyphase filter, which is not shown. The phase splitter reduces the signal swing of the LO, which degrades the noise and conversion gain (CG) performance of the downconversion mixer. Rather than buffer the LO, we chose to compensate for the reduced downconversion mixer performance with a higher gain LNA. This leaves more room for gain control of the LNA.

## A. LNA Design

As the performance requirements of the receiver were pushed back to the LNA, the LNA is by far the most critical block in this design. The LNA must achieve high gain and low power consumption while allowing variable power control. At the same time, the LNA should be matched to  $50~\Omega$ , and the input impedance should be independent of the gain state.

We chose a two-stage design (Fig. 4) with current reuse in order to maximize the gain per power dissipation. Deep n-well transistors were used in order to tie the transistor bulk terminals to their respective sources. This was necessary to prevent an increase in the threshold voltage of the cascade transistors due to the body effect [21]. By keeping a low threshold voltage, the transit frequency  $(f_T)$  of the devices is maintained at a

\_

high value. All three inductors are  $16.9 \, \mathrm{nH}$  with a quality factor (Q) of 8.2 at the operating frequency. Additional resistors were added in parallel to the inductors (not shown in Fig. 4) in order to broaden the matching bandwidth for the matching inductor and the gain bandwidth for the load inductors.

1) Input Matching: The input of the LNA was matched to a 50- $\Omega$  source using a high-pass LC matching network. Compared to a low-pass matching network [22], a high-pass matching network requires only a single inductor (versus two), which can make use of mutual coupling between the coils to boost the effective inductance, resulting in considerably smaller die area usage. A low-pass LC matching requires differential inductors in order to achieve the same effect (not included in our process design kit). An additional 1-k $\Omega$  resistor (not shown in Fig. 4) was added in parallel with the input inductor in order to broaden the matching bandwidth. The overall Q of the matching network is therefore approximately 2.6. Note that we can consider the input impedance of  $M_1/M_2$  as a capacitor with a quality factor of

$$Q_{Cgs} \approx \frac{5g_{d0}}{\omega_0 C_{gs}} \approx \frac{5\omega_T}{\alpha\omega_0}$$

(4)

where  $g_{d0}$  is the zero- $V_{\rm DS}$  drain-source conductance,  $\omega_0$  is the operating frequency in radians per second,  $C_{\rm gs}$  is the gate-source capacitance of  $M_1/M_2$ , and  $\alpha$  is a constant that is approximately equal to one. If, for example,  $\omega_T/\omega_0$  is equal to ten times, we can expect a quality factor of around 50, which is significantly higher than the quality factor of the matching inductor. Therefore, to first order, we can ignore the contributions of the series gate resistance to the input impedance.

The impedance transformation results in a voltage gain of

$$G_1 = \sqrt{\frac{\omega_0 L Q_{L1}}{R_s}} \tag{5}$$

which is equal to 11.3 dB for this design. L is the inductance,  $Q_{L1}$  is the quality factor of the inductor including the additional parallel resistor, and  $R_s$  is the source resistance. From (4), we can see that, in order to get a wide matching bandwidth and high gain, we need a large inductor; however, this is only true for the first-order matching network used. Higher order networks can offer high gain over a broader bandwidth, while maintaining matched input impedance [23], [24].

As the power consumption of the LNA is changed with the gain state, the device capacitances of all transistors and, most importantly,  $M_1$  and  $M_2$  are also changed. These changing device capacitances could potentially alter the frequency at which the LNA is matched to the 50- $\Omega$  source. We can reduce this effect by ensuring that the resonant frequency between the matching inductor and the device capacitances is significantly higher than the operating frequency (2.4 GHz). The same holds true for the two load inductors. Obviously, this puts a restraint on the minimum  $f_T$  of the devices.

2) Voltage Gain: The LNA actually consists of three isolated gain stages with the last stage being a transconductance stage loaded by a finite Q inductor and the passive mixer. The first stage is due to the matching network described above. The second gain stage consists of a V-I conversion by  $M_1$  and  $M_2$

and an I-V conversion by the first load inductor. The output impedance of the cascode V-I converter consisting of  $M_1-M_4$  is significantly higher than the parallel parasitic resistance of the first load inductor. As a result, the gain of the second stage can be closely approximated as

$$G_2 = g_m \omega_0 L Q_{L2} \tag{6}$$

where  $g_m$  is the transconductance of  $M_1$  and  $M_2$ , and  $Q_{L2}$  is the quality factor of the load inductor. The final stage of the LNA is loaded by the quadrature passive mixer and an inductor of the same inductance and Q as the previous stage. The biasing and device sizes are the same as those in the second stage, resulting in the same  $g_m$ . Therefore, with  $G_{\rm mix}$  as the input conductance of the passive mixer, the overall voltage gain is

$$G_{\text{total,LNA}} = \frac{(g_m \omega_0 L Q_{L2})^2}{\omega_0 L Q_{L2} G_{\text{mix}} + 1} \sqrt{\frac{\omega_0 L Q_{L1}}{R_s}}.$$

(7)

In order to achieve sufficient gain bandwidth,  $Q_{L2}$  was reduced from 8.2 to approximately 3.4 using additional resistors parallel to the load inductors. Our expression (7) shows that the LNA gain is proportional to  $g_m^2$ .

- 3) Noise Performance: Under matched conditions, the NF of an LC matching network is 3 dB. This sets the minimum NF of the LNA. However, with sufficient voltage gain in the matching network, the noise contributions of the rest of the circuit can be made small. Inductive degeneration [25] can be considered as an alternative to simple LC matching in order to optimize the noise performance; however, there are tradeoffs. First, with inductive degeneration, the matching gain is still determined by the inductance. With the same total inductance (16.9 nH for the same gain) and Q (8.2) factor, the series resistance of the inductance is 31.7  $\Omega$ . This is enough to achieve -13-dB return loss, making the addition of a degeneration inductor pointless. In order to enjoy the low-noise benefits of inductive degeneration, the largest inductor would need to be implemented off chip (bondwire perhaps). Second, inductive degeneration requires at least one additional inductor. Last and perhaps most importantly, the input resistance offered by inductive degeneration is proportional to the transit frequency of the device [25]. As previously pointed out, an energy-aware LNA requires a changeable dc operating point. Changing the dc operating point affects the transit frequency of the devices and therefore indirectly changes the input resistance.

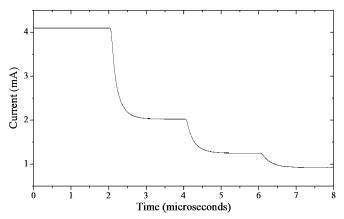

- 4) Switching Time: As changing the gain state of the receiver involves a change in the dc operating point, the receiver must be able to change state fast enough to meet requirements. The IEEE 802.15.4 standard specifies a 128- $\mu$ s preamble [20] at the head of each data packet, which can be used for the phase-locked loop (PLL) and automatic gain control (AGC) to lock. An advantage of designing the gain control in the RF section is that RF circuitry is designed with short time constants. Therefore, the circuits can quickly reach a steady state. Fig. 5 illustrates the settling time of the receiver power consumption as the receiver goes from the highest gain state to the lowest gain state. The receiver requires approximately 1  $\mu$ s for the current consumption to be within 1% of the steady-state value, leaving ample time for the PLL to lock.

Fig. 5. Simulation of the settling time of the receiver. The receiver settles to the desired state within approximately 1  $\mu$ s.

Fig. 6. Model of the LNA–mixer–TIA interface. A Norton equivalent circuit of the LNA is used with an  $R\!-\!L$  output impedance.

# B. Passive Mixer

Passive downconversion was chosen over active downconversion for better flicker noise performance, linearity, and power consumption. The tradeoff is lower input impedance and CG and poorer thermal noise performance. A double-balanced passive mixer is shown in Fig. 6. The passive mixer provides a current-mode output to an IF TIA. In a full RX design, the TIA can be replaced by an active-RC filter [1] using a similar op-amp.

Ignoring the frequency translation, to first order, the currentoutput passive mixer can be analyzed as a simple op-amp in

shunt—shunt feedback. Although the performance will be somewhat different, we can use this simplification to make a few general statements about the features of the topology. Increasing the

conductance of the switches lowers the input impedance, improves the CG, and improves the noise performance. However,

this also reduces the dc loop gain and increases the loading to

the voltage-controlled oscillator. At frequencies below the dominant pole frequency of the loop gain, this degrades linearity

(IIP<sub>3</sub> for example). Above the dominant pole frequency, the loop

gain is almost independent of the switch conductance. This is

an important difference between direct-conversion and low-IF

(megahertz-range IF) receivers.

As previously pointed out, the frequency translation introduces an additional dimension to the analysis, which reduces the accuracy of the simple feedback op-amp model. The next few sections will discuss the differences in the context of CG by looking at three main parts: the LNA-mixer interface, the mixer

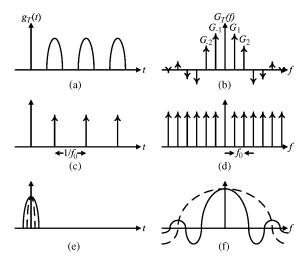

Fig. 7. Decomposition of  $g_T(t)$  in the time and frequency domain. (a)  $g_T(t)$ . (b)  $G_T(f)$ . (c) Pulse train in time. (d) Pulse train in frequency. (e) Sampling function in time. (f) Sampling function in frequency. (e) and (f) Sampling function for two different sampling function widths.

core, and the mixer–TIA interface. For the LNA–mixer interface, we are mainly concerned with the passive mixer's input impedance since (7) shows that it will affect the LNA voltage gain. For the passive mixer core, we will concentrate on the CG from the switching transistors to the IF. For the mixer–TIA interface, we are mainly concerned with the output impedance, which, as mentioned, affects loop stability and linearity. We will set up our analyses by briefly discussing convolution matrices [26].

1) Convolution Matrices: A simple model for the time-varying conductance of a single switch (Fig. 6) in the ON state is

$$g_{T1}(t) = K \left( V_{\text{LO}} \cos(\omega_{\text{LO}} t) + V_{\text{dc}} - V_T \right) \tag{8}$$

where K is a constant that depends on the switch sizes and the technology,  $V_{LO}$  is the LO signal swing,  $V_{dc}$  is the bias voltage across the gate and source of the switches, and  $V_T$  is the threshold voltage of the switches. In the OFF state,  $g_{T1}(t) =$ 0. As the LO is available in quadrature phases, we can define  $LOI_p$  by (8). For the switches driven by  $LOI_m$ ,  $LOQ_p$ , and  $LOQ_m$ , the cosine in (8) is replaced by negative cosine, positive sine, and negative sine, respectively. The conductance of these switches are  $g_{T2}(t)$ ,  $g_{T3}(t)$ , and  $g_{T4}(t)$ . It should be noted that (8) assumes that the LO signal appearing at the sources of the switching transistors is negligible, which is true for typical biasing conditions. In practice, LO leakage to the mixer input is dependent on the output impedance of the LNA, and it can, in turn, change the conductance of the switching transistors. However, since we have assumed no leakage, the mixers' operation is independent of the LNA output impedance.

From Fig. 7, we can see how  $g_{T1}(t)$  to  $g_{T4}(t)$  can be mapped into the frequency domain.  $g_{T1}(t)$  is a convolution between an impulse train and a sampling function, which, in the frequency domain, is represented by a multiplication between a frequency-domain impulse train and a frequency-domain sampling function. A mixer multiplies in the time domain, and hence, the output in the frequency domain is a convolution of the input and  $G_{T1}(f)$ .  $G_{T1}(f)$  only has values at discrete frequencies

6

because we assumed that the LO is periodic. We can therefore write convolution matrices for  $G_{T1}(f)$  to  $G_{T4}(f)$  [26]. If only the first two harmonics are considered, then the result is

$$\mathbf{G_{T1}(f)} = \begin{bmatrix} G_0 & G_{-1} & G_{-2} \\ G_1 & G_0 & G_{-1} \\ G_2 & G_1 & G_0 \end{bmatrix}$$

(9)

$$\mathbf{G_{T2}(f)} = \begin{bmatrix} G_0 & -G_{-1} & G_{-2} \\ -G_1 & G_0 & -G_{-1} \\ G_2 & -G_1 & G_0 \end{bmatrix}$$

(10)

$$\mathbf{G_{T1}(f)} = \begin{bmatrix} G_0 & G_{-1} & G_{-2} \\ G_1 & G_0 & G_{-1} \\ G_2 & G_1 & G_0 \end{bmatrix}$$

(9)

$$\mathbf{G_{T2}(f)} = \begin{bmatrix} G_0 & -G_{-1} & G_{-2} \\ -G_1 & G_0 & -G_{-1} \\ G_2 & -G_1 & G_0 \end{bmatrix}$$

(10)

$$\mathbf{G_{T3}(f)} = \begin{bmatrix} G_0 & -jG_{-1} & -G_{-2} \\ jG_1 & G_0 & -jG_{-1} \\ -G_2 & jG_1 & G_0 \end{bmatrix}$$

(11)

$$\mathbf{G_{T4}(f)} = \begin{bmatrix} G_0 & jG_{-1} & -G_{-2} \\ -jG_1 & G_0 & jG_{-1} \\ -G_2 & -jG_1 & G_0 \end{bmatrix}$$

(12)

$$\mathbf{G_{T4}(f)} = \begin{bmatrix} G_0 & jG_{-1} & -G_{-2} \\ -jG_1 & G_0 & jG_{-1} \\ -G_2 & -jG_1 & G_0 \end{bmatrix}$$

(12)

where we have limited  $G_{TN}(f)$  to a 3 × 3 matrix for simplicity. Note how the  $G_{-1}$  in (9) and (10) is in phase, while it is out of phase in (11) and (12). This is a simplification since, in a real MOSFET, the internal capacitances of the device result in both in-phase and out-of-phase components for each term in (9)–(12). The subscripts n for each entry correspond to  $f_{\rm RF} + n f_{\rm LO}$ . The convolution matrix components for  $G_{\rm T2}({\bf f})$ to  $G_{T4}(f)$  are given in terms of those calculated for  $G_{T1}(f)$ . As an example of how to use the convolution matrices, assume that we apply a small voltage  $V_A$ , which has a spectral component at  $f_{RF}$ , across a switch governed by (9). We can calculate the output components at the zero, positive, and negative sidebands as

$$\begin{bmatrix} I_{A,f_{RF}-f_{LO}} \\ I_{A,f_{RF}} \\ I_{A,f_{RF}+f_{LO}} \end{bmatrix} = \begin{bmatrix} G_0 & G_1 & G_2 \\ G_1 & G_0 & G_1 \\ G_2 & G_1 & G_0 \end{bmatrix} \begin{bmatrix} 0 \\ V_A \\ 0 \end{bmatrix}.$$

(13)

This is obviously just a simple extension of Ohm's law. We can then use Kirchhoff's laws to analyze the entire mixer. The TIA's op-amp is assumed to be ideal at IFs, and hence, the IF bandwidth is not apparent from our derivations. Let  $Y_{TIA}$  be the TIA input admittance and  $V_{\rm RF}$  be the voltage across the mixer input terminals. Therefore, we can write

$$V_{X} = (G_{T1} + G_{T2} + Y_{TIA})^{-1}(G_{T1} - G_{T2})V_{RF}$$

(14)

$$V_{Y} = (G_{T3} + G_{T4} + Y_{TIA})^{-1}(G_{T3} - G_{T4})V_{RF}$$

(15)

where  $V_X$  and  $V_Y$  are defined in Fig. 6. At high frequencies, the op-amp gain tends to zero, and we can approximate the TIA input admittance as  $R_f$  in parallel with some node capacitance

2) LNA-Mixer Interface: Based on the above discussion, we can derive the passive mixer's differential input conductance as

$$G_{\text{mix}} \approx 2G_0 - \frac{4G_{-1}G_1R_f}{1 + R_f(s_1C_X + 2G_0)}$$

(16)

where  $s_1$  is equal to  $2\pi(f_{RF} + f_{LO})$ . The first term  $2G_0$  can be seen by inspection. However, an additional term arises following our assumption that the TIA input impedance tends toward  $R_f || C_X$  at high frequencies. From Fig. 6, the input signal is upconverted due to  $G_{T1}$  and forms a voltage at  $V_X$ . This high-frequency signal then gets downconverted through  $G_{T2}$ ,

which is out of phase with  $G_{T1}$ , resulting in an overall negative input admittance term. Similar paths exist through  $G_{T3}$  and  $G_{T4}$ . If the op-amp bandwidth were infinite, this additional term would not arise.

The additional term in (16) is beneficial in that it increases the input impedance of the passive mixer, and it would seem that if  $R_f$  is large and  $s_1C_X$  is minimized,  $G_1$  can be made equal to  $G_0$ , and the input impedance would be infinite. The ratio  $G_1/G_0$  is dependent on the peak-to-average conductance of the switches and tends toward a value of one as the duty cycle of the switches is reduced [27]. The ratio of  $2G_0$  to  $s_1C_X$  will depend on the technology used and the frequency of operation. Clearly, for  $s_1C_X$  to be considered negligible, the technology's  $f_T$  would have to be at least an order of magnitude higher than the operation frequency. Taking into account the op-amp's input capacitance,  $s_1C_X$  was found to be significantly greater than  $2G_0$  in our design.

3) The Mixer Core: As with our analysis of the input admittance, we can calculate the CG of the passive mixer as

$$\frac{V_{\text{IFI}}}{V_{\text{RF}}} \approx -2G_1 R_f + \frac{4G_{-2}G_1 R_f^2}{1 + R_f (s_1 C_X + 2G_0)}$$

(17)

$$\frac{V_{\rm IFQ}}{V_{\rm RF}} \approx 2jG_1R_f - \frac{4jG_{-2}G_1R_f^2}{1 + R_f(s_1C_X + 2G_0)}.$$

(18)

The term  $-2G_1R_f$  can be seen on inspection due to the shunt-shunt feedback configuration. Needless to say, solving the problem using higher order matrices will lead to more complex solutions. Once again we note that  $s_1C_X$  is large, and it therefore limits the influence of the term involving  $G_2$ .

4) Mixer-TIA Interface: The op-amp is conveniently designed as a two-stage amplifier where the first stage provides dc gain and the second stage is used to drive the output impedance. Assuming that the second stage is a transconductance  $G_{m2}$  and the first stage provides dc gain  $A_1$ , it is easy to see that the dc loop gain of the TIA is  $A_1G_{m2}/G_{out}$ , where  $G_{out}$  is the output conductance of the passive mixer. Reducing  $G_{\text{out}}$  improves the loop gain, thereby improving the linearity of the TIA while also degrading its phase margin. The resonator at the output of the LNA can be approximated as having conductance  $G_{

m LNA}$  (equal to  $(\omega_0 L Q_{L2})^{-1})$  at  $f_{\rm RF}$  and infinity at other frequencies. We can then calculate  $G_{\mathrm{out}}$  as

$$G_{\text{out}} \approx G_0 - \frac{G_1 G_{-1}}{G_0 + G_{\text{LNA}} + \frac{G_{\text{mix}}}{2}}.$$

(19)

We can see from (19) that the output impedance of the passive mixer depends on not only the conductance of the switches but also the output impedance of the LNA. Note that  $C_X$  was assumed to be part of the TIA. The second term in (19) results from mixing up and then back down in frequency. The output impedance was calculated using  $3 \times 3$  matrices rather than  $5 \times 3$ 5 due to the computational difficulty.

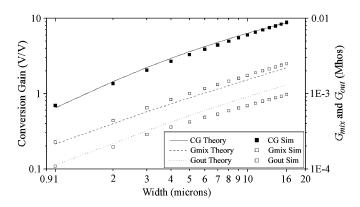

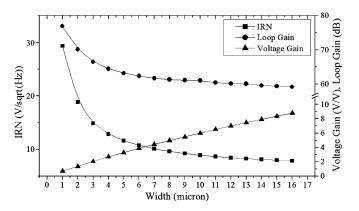

5) Accuracy of the Analysis: In Fig. 8, (16), (17), and (19) and their simulated counterparts are plotted versus the switch width in micrometers ( $G_n$  were extracted from the simulation of a single MOSFET). They are plotted on a log scale to illustrate how the theoretical results can be fitted to the simulated data by adding a multiplicative factor. Ignoring the accuracy,

Fig. 8. Comparison between theoretically calculated and simulated conversion gain (in volts per volt), input conductance ( $G_{\rm mix}$ ), and output conductance ( $G_{\rm out}$ ). In simulation, the LO was 2.45 GHz and 250 mV<sub>pk</sub> per phase.

Fig. 9. Switch width optimization including input-referred noise (IRN), op-amp loop gain, and voltage gain. The LO was 2.45 GHz and 250 mV  $_{\rm pk}$  per phase.

the trend derived in the equations holds true in simulation. As mentioned earlier, a real MOSFET includes a distribution of capacitances and resistances that were not modeled by our simple model, and this is the biggest factor contributing to the equations' inaccuracy.

6) Overall Implementation: Based on the preceding analyses, we can optimize the switch size, LO strength, and  $R_f$ . Increasing the LO voltage improves the conductance of the switches without greatly affecting the switches' capacitance. Therefore, for minimum capacitive loading to the frequency synthesizer and LNA, we should maximize the LO voltage. We chose a 250-mV peak per LO phase as this value does not require excessive driving capability of the LO. For  $R_f$ , we note from the section above that  $R_f$ , to first order, does not affect the op-amp loop gain. However, if the nondominant pole is at the output of the op-amp, then a smaller  $R_f$  leads to a higher op-amp unity-gain bandwidth. As a compromise between the overall voltage gain [(17) and (18)] and bandwidth, we selected  $R_f$  to be 4 k $\Omega$ . The simulation data in Fig. 8 illustrate the optimization of the switch width. When using Fig. 8, we must take into account the increasing  $G_{\rm mix}$  (Fig. 9) loads down the LNA, thereby reducing the LNA voltage gain [this is evident from (7)]. Therefore, there is an optimum width for the minimum overall NF. For the LNA output impedance of 880  $\Omega$ , this was found to be 4  $\mu$ m, but because a larger switch size is

Fig. 10. Op-amp for the transimpedance amplifier.

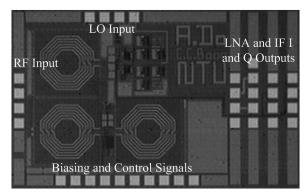

Fig. 11. Micrograph of the fabricated design

Fig. 12. NF of the LNA in all four gain modes.

more forgiving in terms of process variation, we chose a switch width of 5  $\mu$ m.

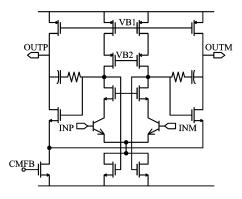

#### C. TIA

The fully differential op-amp is shown in Fig. 10. The input differential pair uses parasitic NPN transistors that provide better matching, dc-offset and flicker noise performance than MOS devices [28]. In a CMOS process, n-p-n bipolar junction transistors are formed using the deep n-well, p-well, and n-well layers. The current consumption of the op-amp is defined by PMOS current sources, and common-mode feedback is used in the output stage to set the input and output common-mode voltages to 1 V. This common-mode voltage propagates back to the input of the passive mixer. Miller compensation was used to set the phase margin to  $60^{\circ}$ . The TIAs were designed to consume  $100 \ \mu A$  each from the 1.8-V supply.

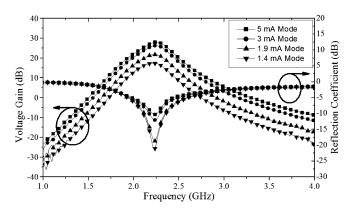

Fig. 13. Voltage gain and input reflection coefficient of the LNA in all four gain modes.

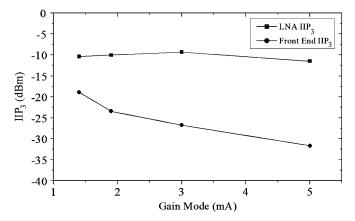

Fig. 14. Measured  $IIP_3$  (in decibels of the measured power referenced to 1 mW) versus gain mode (in milliamperes) for the LNA only and the full front end.

#### V. IMPLEMENTATION AND MEASUREMENT

The system described in Fig. 3 was implemented in a low-cost 6-metal-1-poly 0.18- $\mu$ m RF CMOS process with a 2.5- $\mu$ m top metal. Fig. 11 shows a micrograph of the fabricated design. The LO polyphase splitter was implemented on chip as a two-stage RC polyphase splitter. This was done in order to reduce the pad count. Due to the limitation on the number of RF probes that could be used, the biasing circuitry was implemented using on-chip resistors. The drawback is that the current consumption of the chip can significantly deviate from the designed value. We used a constant- $g_m$  biasing circuit [21] for the LNA with a resistor that could be varied in three steps. This is an extremely simplistic method for gain tuning, and in retrospect, a more robust method involving power detection should have been used. Such circuits are readily found for gain control in AGC loops [1] and often involve decision making by the digital signal processor.

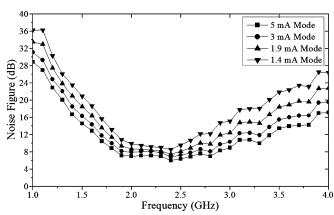

### A. Measured LNA Performance

The LNA was characterized for matching, noise, gain, and linearity performance. The NF in all four gain modes is shown in Fig. 12. The LNA achieves a 6-dB NF in the 5-mA mode. The input reflection coefficient and gain are shown in Fig. 13. From Fig. 13, the LNA matching frequency shifted down to 2.25 GHz. However, the two other resonating nodes in the LNA did not experience the same frequency shift. As a result, the voltage

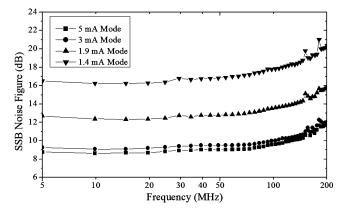

Fig. 15. SSB NF of the front end in all four gain modes. LO was fixed at 2.31 GHz and 0 dBm.

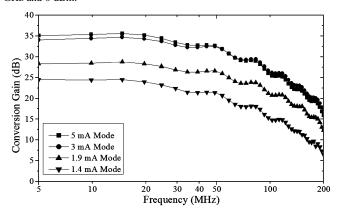

Fig. 16. Conversion gain of the front end in all four gain modes. LO was fixed at 2.31 GHz and 0 dBm.

gain frequency response is somewhat distorted. The result was a decreased center frequency gain and a corresponding increase in the minimum NF. The IIP $_3$  was measured to be -11.5 dBm in the highest gain mode and showed a slight improvement (1 dB) in lower gain modes. This is shown in Fig. 14. Although the gain drops in lower gain modes, the bias point changes, somewhat offsetting the improvement in IIP $_3$ .

The LNA was designed for a gain step of 6 dB. However, as previously mentioned, the biasing network was designed using on-chip resistors due to a limitation on the number of probes. Unfortunately, the measured bias current significantly deviated (around 25% in 5-mA mode) from the nominal value, resulting in a change in the gain step. Future iterations of this work will use a more accurate gain step.

# B. Measured Front-End Performance

The front end was characterized for noise, gain, linearity, and power consumption performance. The NF and CG of the front end were measured using the Agilent E4407B spectrum analyzer, which has a built-in NF personality. Unfortunately, neither the spectrum analyzer nor our noise source was designed to be used below 10 MHz. The current consumption in the highest to lowest power modes are 5.01, 2.97, 1.88, and 1.39 mA, respectively, with a 1.8-V supply. From Fig. 15, the front-end single-sideband (SSB) NF is around 9 dB [approximately 6 dB for the double-sideband (DSB) NF] in the highest gain mode and increases with the reduced LNA gain. The front-end gain, as seen in Fig. 16, agrees with the LNA gain. The IIP<sub>3</sub> for the front

TABLE I COMPARISON TO PRIOR PUBLISHED WORK

| Reference         | This Work          |                    |                     |            | [1]              | [22] | [29] |

|-------------------|--------------------|--------------------|---------------------|------------|------------------|------|------|

| Frequency (GHz)   | 2.3                |                    |                     |            | 2.4              | 2.5  | 2.4  |

| Current (mA)      | 5                  | 3                  | 1.9                 | 1.4        | 5.6 <sup>A</sup> | 1.16 | 2.39 |

| Noise Figure (dB) | $8.8^{\mathrm{B}}$ | $9.3^{\mathrm{B}}$ | $12.7^{\mathrm{B}}$ | $16.5^{B}$ | 5.7              | 5    | 12   |

| $IIP_3$ (dBm)     | -31                | -27                | -23                 | -19        | -16              | -37  | -    |

| Voltage Gain (dB) | 35.6               | 34.7               | 28.7                | 24.5       | $33^{\rm C}$     | 43   | -    |

| Technology (µm)   | 0.18               |                    |                     |            | 0.18             | 0.18 | 0.18 |

- A Entire analog front-end included

- <sup>B</sup> SSB NF which is approximately 3 dB higher than DSB NF

- $^{\rm C}$  Only LNA gain included

end is -31 dBm in the highest gain mode and improves with a lower LNA gain. This is shown in Fig. 14. This was sufficient for our application but can be improved by increasing the loop gain of the op-amps. The front-end gain of 35 dB in the highest gain mode is sufficient such that the noise performance of the subsequent blocks can be made insignificant without requiring high power consumption. Table I shows a comparison between the proposed design and the current literature. The NF quoted in this paper is SSB NF, while that in [22] is DSB NF. References [1] and [29] use image-reject mixers, which are able to suppress the noise in the image band; however, the work in [29] uses two IFs, and it is not clear how well the first image noise is suppressed. Perumana et al. [22] used high-Q input matching and active mixing to achieve excellent NF for its current consumption. This came at the cost of a low IIP<sub>3</sub> and a possibly high flicker noise corner frequency. It should be noted that the key point in [29] was the innovative use of a digital demodulator, which allowed the authors to achieve a low overall power consumption and good performance.

#### VI. CONCLUSION

Communication between a mobile device and a fixed hub allows for energy-aware design of the mobile RX and TX where the mobile TX's output power is optimized and the mobile RX's sensitivity is optimized. This paper has discussed the design and implementation of an energy-aware RX involving optimization based on several different input conditions rather than the minimum sensitivity. A design methodology that simplifies the RX design has been presented, which involves pushing NF requirements to the front end while only maintaining sufficient bandwidth for proper filtering in the IF section. This allows greater control of the front-end power consumption. Following circuit analysis of the front-end blocks, measurement results of the proposed front end have been presented. The front-end power consumption exhibited up to 72% reduction in power consumption with high input power.

#### **APPENDIX**

For a sinusoidal LO,  $G_0$  and  $G_1$  were calculated to be equal to

$$G_1 = \frac{V_{\rm LO}}{2\pi} \cos^{-1} \left( \frac{V_T - V_{\rm dc}}{V_{\rm LO}} \right) + \frac{(V_{\rm dc} - V_T)}{\pi} \cdot \sin \cos^{-1}$$

$$\times \left(\frac{V_T - V_{dc}}{V_{LO}}\right) + \frac{V_{LO}}{4\pi} \sin 2 \cos^{-1} \left(\frac{V_T - V_{dc}}{V_{LO}}\right) \tag{20}$$

$$G_0 = \frac{V_{dc} - V_T}{\pi} \cos^{-1} \left(\frac{V_T - V_{dc}}{V_{LO}}\right) + \frac{V_{LO}}{\pi} \sin \cos^{-1} \left(\frac{V_T - V_{dc}}{V_{LO}}\right). \tag{21}$$

From (20) and (21), if we were to bias the voltage-output passive mixer at the threshold voltage of the transistor (i.e.,  $V_{\rm dc} = V_T$ ), the ratio  $G_1/G_0$  would be equal to  $\pi/4$ , which is -2.1 dB. This agrees with the analysis in [27].

#### ACKNOWLEDGMENT

The authors would like to thank W. M. Lim, and T. S. Wong of the Nanyang Technological University, Singapore, for their help in the on-wafer measurement and the members of the Designer's Guide Community for the many useful discussions.

## REFERENCES

- [1] W. Kluge, F. Poegel, H. Roller, M. Lange, T. Ferchland, L. Dathe, and D. Eggert, "A fully integrated 2.4-GHz IEEE 802.15.4-compliant transceiver for ZigBee applications," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2767–2775, Dec. 2006.

- [2] I. Nam, K. Choi, J. Lee, H.-K. Cha, B.-I. Seo, K. Kwon, and K. Lee, "A 2.4-GHz low-power low-IF receiver and direct-conversion transmitter in 0.18- μm CMOS for IEEE 802.15.4 WPAN applications," IEEE Trans. Microw. Theory Tech., vol. 55, no. 4, pp. 682–689, Apr. 2007

- [3] T.-K. Nguyen, N.-J. Oh, V.-H. Hoang, and S.-G. Lee, "A low-power CMOS direct conversion receiver with 3-dB NF and 30-kHz flicker noise corner for 915-MHz band IEEE 802.15.4 ZigBee standard," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 2, pp. 735–741, Feb. 2006.

- [4] T.-K. Nguyen, V. Krizhanovskii, J. Lee, S.-K. Han, S.-G. Lee, N.-S. Kim, and C.-S. Pyo, "A low-power RF direct-conversion receiver/transmitter for 2.4-GHz-band IEEE 802.15.4 standard in 0.18-μm CMOS technology," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 12, pp. 4062–4071, Dec. 2006.

- [5] M. Camus, B. Butaye, L. Garcia, M. Sié, B. Pellat, and T. Parra, "A 5.4 mW/0.07 mm 2 2.4 GHz front end receiver in 90 nm CMOS for IEEE 802.15.4 WPAN standard," *IEEE J. Solid-State Circuits*, vol. 43, no. 6, pp. 1372–1383, Jun. 2008.

- [6] A. V. Do, C. C. Boon, M. A. Do, K. S. Yeo, and A. Cabuk, "An energy aware CMOS front end for 2.4-GHz ISM band low power applications," in *Proc. IFIP/IEEE Int. Conf. Very Large Scale Integr.*, Oct. 2008, pp. 148–151.

- [7] T. S. Rappaport, "Mobile radio propagation: Large-scale path loss," in Wireless Communications Principles and Practice, 2nd ed. Upper Saddle River, NJ: Prentice-Hall, 2002, ch. 4, pp. 105–176.

- [8] W. Sansen, "Distortion in elementary transistor circuits," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 46, no. 3, pp. 315–325, Mar. 1999.

- [9] B. Razavi, "Basic concepts in RF design," in RF Microelectronics. Upper Saddle River, NJ: Prentice-Hall, 1998, ch. 2, sec. 2.1.1, p. 22.

- [10] T. H. Lee, "Noise," in *The Design of CMOS Radio-Frequency Integrated Circuits*, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, 2004, ch. 11, p. 339.

- [11] P. Gorday, 802.15.4 Multipath [Online]. Available: https://mentor.ieee.org/802.15/file/04/15-04-0337-00-004b-802-15-4-multipath.ppt Jul. 2004, Internet [Oct. 2009]

- [12] R. Senguttuvan, S. Sen, and A. Chatterjee, "Multidimensional adaptive power management for low-power operation of wireless devices," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 9, pp. 867–871, Sep. 2008.

- [13] S. Lloyd, "Challenges of mobile WiMAX RF transceivers," in Proc. Int. Conf. Solid-State Integr. Circuit Technol., Oct. 2006, pp. 1821–1824.

- [14] N. Pletcher, S. Gambini, and J. Rabaey, "A 65 uW, 1.9 GHz RF to digital baseband wakeup receiver for wireless sensor nodes," in *Proc. CICC*, San Jose, CA, Sep. 16–19, 2007.

- [15] N. Pletcher, S. Gambini, and J. Rabaey, "A 2 GHz 52 pW wake-up receiver with -72 dBm sensitivity using uncertain-IF architecture," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2008, pp. 523-525.

- [16] T. S. Salter, B. Yang, and N. Goldsman, "Low power receiver design utilizing weak inversion and RF energy harvesting for demodulation," in *Proc. Int. Semicond. Device Res. Symp.*, Dec. 2007, pp. 1–2.

- [17] D. Daly and A. P. Chandrakasan, "An energy-efficient OOK transceiver for wireless sensor networks," *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 1003–1011, May 2007.

- [18] P. Choi, H. C. Park, S. Kim, S. Park, I. Nam, T. W. Kim, S. Park, S. Shin, M. S. Kim, K. Kang, Y. Ku, H. Choi, S. M. Park, and K. Lee, "An experimental coin-sized radio for extremely low-power WPAN (IEEE 802.15.4) application at 2.4 GHz," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2258–2268, Dec. 2003.

- [19] C. Bernier, F. Hameau, G. Billiot, E. de Foucauld, S. Robinet, J. Durupt, F. Dehmas, E. Mercier, P. Vincent, L. Ouvry, D. Lattard, M. Gary, C. Bour, J. Prouvee, and S. Dumas, "An ultra low power 130 nm CMOS direct conversion transceiver for IEEE802.15.4," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Apr./Jun. 2008, pp. 273–276.

- [20] Standard For Local and Metropolitan Area Networks, IEEE 802.15.4, 2003.

- [21] B. Razavi, "Basic MOS device physics", 'bandgap references'," in *Design of Analog CMOS Integrated Circuits*, International Edition ed., Singapore: McGraw-Hill, 2001, ch. 2 and 11, sec. 2.3 and 11.2, pp. 23–24, 379.

- [22] B. G. Perumana, R. Mukhopadhyay, S. Chakraborty, C.-H. Lee, and J. Laskar, "A low-power fully monolithic subthreshold CMOS receiver with integrated LO generation for 2.4 GHz wireless PAN applications," *IEEE J. Solid-State Circuits*, vol. 43, no. 10, pp. 2229–2238, Oct. 2008.

- [23] C. Bowick, "Impedance matching," in *RF Circuit Design*, 1st ed. Indianapolis, IN: Sams, 1982, ch. 4, pp. 72–75.

- [24] A. Ismail and A. A. Abidi, "A 3-10 GHz low-noise amplifier with wideband LC-ladder matching network," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2269–2277, Dec. 2004.

- [25] D. K. Shaeffer and T. H. Lee, "A 1.5-V, 1.5-GHz CMOS low-noise amplifier," *IEEE J. Solid-State Circuits*, vol. 32, no. 5, pp. 745–759, May 1997.

- [26] S. A. Mass, "Harmonic balance analysis and related methods," in *Non-linear Microwave and RF Circuits*, 2nd ed. Norwood, MA: Artech House, 2003, ch. 3, pp. 164–197.

- [27] A. R. Shahani, D. K. Shaeffer, and T. H. Lee, "A 12-mW wide dynamic range CMOS front end for a portable GPS receiver," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 2061–2070, Dec. 1997.

- [28] I. Nam and K. Lee, "High performance RF mixer and operational amplifier BiCMOS circuits using parasitic vertical bipolar transistors in CMOS technology," *IEEE J. Solid-State Circuits*, vol. 40, no. 2, pp. 392–402, Feb. 2005.

- [29] C.-P. Chen, M.-J. Yang, H.-H. Huang, T.-Y. Chiang, J.-L. Chen, M.-C. Chen, and K.-A. Wen, "A low-power 2.4-GHz CMOS GFSK transceiver with a digital demodulator using time-to-digital conversion," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 12, pp. 2738–2748, Dec. 2009.

Chirn Chye Boon (M'09) received the B.E.(Hons.) degree in electronics and the Ph.D. degree in electrical engineering from Nanyang Technological University (NTU), Singapore, in 2000 and 2004, respectively.

In 2005, he joined NTU as a Research Fellow and became an Assistant Professor in the same year. Before that, he was with Advanced RFIC, where he worked as a Senior Engineer. He specializes in direct-conversion RF transceiver front-end design, phase-locked-loop frequency synthesizers, clock and

data recovery circuits, and frequency dividers.

Prof. Boon is a Reviewer for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I, IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, and IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

Manh Anh Do (M'04–SM'05) received the B.Sc. degree in physics from the University of Saigon, Ho Chi Minh, Vietnam, in 1969 and the B.E.(Hons.) degree electronics and the Ph.D. degree in electrical engineering from the University of Canterbury, Canterbury, New Zealand, in 1973 and 1977, respectively.

Between 1977 and 1989, he held various positions, including as a Design Engineer, Production Manager, and Research Scientist in New Zealand and a Senior Lecturer with the National University of Singapore, Singapore. He joined the School of

Electrical and Electronic Engineering, Nanyang Technological University (NTU), Singapore, as a Senior Lecturer in 1989 and obtained the Associate Professorship in 1996 and Professorship in 2001. Between 1995 and 2005, he was Head of Division of Circuits and Systems, NTU. He is currently the Director of Center for Integrated Circuits and Systems, NTU. He has been a consultant for many projects in the electronics industry and was a key consultant for the implementation of the 200-million-dollar Electronic Road Pricing project in Singapore from 1990 to 2001. He is the author or a coauthor of 105 papers in leading journals and 140 papers in international conference proceedings. His current research interests include mobile communications, RFIC design, mixed-signal circuits, and intelligent transport systems.

Prof. Do is a Chartered Engineer. He is a Fellow of the Institution of Engineering Technology (IET). He was a Council Member of IET, U.K., from 2001 to 2004 and an Associate Editor for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES in 2005 and 2006.

**Kiat Seng Yeo** (M'04) received the B.E.(Hons.) degree in electronics and the Ph.D. degree in electrical engineering from Nanyang Technological University (NTU), Singapore, in 1993 and 1996, respectively.

He is currently the Head of the Division of Circuits and Systems and a Professor of electrical and electronic engineering with NTU. He is a recognized expert in CMOS technology and low-power CMOS IC design. He gives consulting to multinational corporations. He is the holder of 15 patents. He has published four books (International editions) and more

than 250 papers in his areas of expertise. His research interests include device modeling, low-power circuit design, and RFIC design.

Dr. Yeo serves in the organizing and program committee of several international conferences as the General Chair, a Cochair, the Technical Chair, etc.

Aaron V. Do (S'05–M'06) was born in Wellington, New Zealand, in 1982. He received the B.Sc. degree in electrical engineering in 2004 from the University of Texas at Austin and the M.Eng. degree in electrical and electronic engineering (specializing in LNA and passive mixer design for direct-conversion receivers) in 2006 from Nanyang Technological University, Singapore, where he is currently working toward the Ph.D. degree.

He is currently a Research Associate with Nanyang Technological University. His research focuses on ul-

tralow-power RF front-end circuit and system design.

Alper Cabuk (M'07) received the B.Sc. degree in electrical engineering from the Middle East Technical University, Ankara, Turkey, in 1999 and the M.Eng. and Ph.D. degrees in electrical and electronic engineering from Nanyang Technological University (NTU), Singapore, in 2002 and 2006.

He was with the Information Technologies Institute (Bilten), Ankara, Turkey, from 1998 to 1999. He is currently a Research Fellow with NTU, Singapore. His research interests include CMOS RFIC design, low-voltage low-power analog/baseband circuit de-

sign, and clock and data recovery circuits for SONET systems.