# This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

Design of an electronic synapse with spike time dependent plasticity based on resistive memory device

Hu, S. G.; Wu, H. T.; Liu, Y.; Liu, Z.; Yu, Q.; Yin, Y.; Chen, Tupei; Hosaka, Sumio

2013

Hu, S. G., Wu, H. T., Liu, Y., Chen, T., Liu, Z., Yu, Q., Yin, Y., & Hosaka, S. (2013). Design of an electronic synapse with spike time dependent plasticity based on resistive memory device. Journal of Applied Physics, 113(11), 114502.

https://hdl.handle.net/10356/98141

https://doi.org/10.1063/1.4795280

© 2013 American Institute of Physics. This paper was published in Journal of Applied Physics and is made available as an electronic reprint (preprint) with permission of American Institute of Physics. The paper can be found at the following official DOI: [http://dx.doi.org/10.1063/1.4795280]. One print or electronic copy may be made for personal use only. Systematic or multiple reproduction, distribution to multiple locations via electronic or other means, duplication of any material in this paper for a fee or for commercial purposes, or modification of the content of the paper is prohibited and is subject to penalties under law.

Downloaded on 20 Mar 2024 17:55:46 SGT

# Design of an electronic synapse with spike time dependent plasticity based on resistive memory device

S. G. Hu, H. T. Wu, Y. Liu, T. P. Chen, Z. Liu et al.

Citation: J. Appl. Phys. 113, 114502 (2013); doi: 10.1063/1.4795280

View online: http://dx.doi.org/10.1063/1.4795280

View Table of Contents: http://jap.aip.org/resource/1/JAPIAU/v113/i11

Published by the AIP Publishing LLC.

## Additional information on J. Appl. Phys.

Journal Homepage: http://jap.aip.org/

Journal Information: http://jap.aip.org/about/about\_the\_journal Top downloads: http://jap.aip.org/features/most\_downloaded

Information for Authors: http://jap.aip.org/authors

## ADVERTISEMENT

Explore AIP's open access journal:

- Article-level metrics

- Post-publication rating and commenting

# Design of an electronic synapse with spike time dependent plasticity based on resistive memory device

S. G. Hu, <sup>1</sup> H. T. Wu, <sup>1</sup> Y. Liu, <sup>1,a)</sup> T. P. Chen, <sup>2,b)</sup> Z. Liu, <sup>2</sup> Q. Yu, <sup>1</sup> Y. Yin, <sup>3</sup> and Sumio Hosaka<sup>3</sup> <sup>1</sup>State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, People's Republic of China <sup>2</sup>School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 Graduate School of Engineering, Gunma University, 1-5-1 Tenjin, Kiryu, Gunma 376-8515, Japan

(Received 7 December 2012; accepted 28 February 2013; published online 15 March 2013)

This paper presents a design of electronic synapse with Spike Time Dependent Plasticity (STDP) based on resistive memory device. With the resistive memory device whose resistance can be purposely changed, the weight of the synaptic connection between two neurons can be modified. The synapse can work according to the STDP rule, ensuring that the timing between pre and post-spikes leads to either the long term potentiation or long term depression. By using the synapse, a neural network with three neurons has been constructed to realize the STDP learning. © 2013 American *Institute of Physics.* [http://dx.doi.org/10.1063/1.4795280]

#### I. INTRODUCTION

In the past three decades, neural network<sup>1,2</sup> has received much attention, due to its remarkable ability in fuzzy pattern recognition, associative memory, and self-learning, etc., while those are difficult or time-consuming for realization by solid state devices and software. Neural network, generally, consists of neurons and synapses between neurons. Synapses are crucial elements for computation and information storage in both human brain and artificial neural systems. Each synapse represents a particular strength (i.e., the synaptic weight) of the connection between adjacent neurons, and thus, the information is stored in synapses by different synaptic strength. On the other hand, the spiking activity of neurons can modify the strength of the synapses connecting the neurons, <sup>3,4</sup> by which a neural network possesses self-learning ability. Presynaptic and post-synaptic actions and their timing are critical to synaptic weight modification. The sequence mechanisms are known as Long Term Potentiation (LTP) and Long Term Depression (LTD), respectively. If the pre-synaptic spike precedes the post-synaptic spike, the synapse undergoes a LTP, while if the post-synaptic spike precedes the pre-synaptic spike, LTD signal is generated. The time interval between the pre-synaptic spike and post-synaptic spike determines the variation of synaptic strength. The combination of the sequence and timing mechanisms is called Spike Time Dependent Plasticity (STDP).5

Several techniques have been used to implement synapse, including resistors, dynamic capacitive storage, EEPROM (electrically erasable/programable read-only memory)/floating gate memory,<sup>7,8</sup> etc.; such techniques are either not reprogrammable or very complicated. Resistive memory device is emerging as a promising candidate.<sup>9–14</sup> A resistive memory is reprogrammable, i.e., the resistance of the device can be modified by applying a voltage or current with different amplitudes, different polarities, or different durations between its two terminals, and the resistance state can be maintained for a certain

<sup>a)</sup>Email: yliu2008@e.ntu.edu.sg b)Email: echentp@ntu.edu.sg

period. It has attracted a lot of interests due to its simple structure, high density, high speed, low power consumption, and great compatibility with the standard CMOS process.

In this paper, we propose a design of synapse based on resistive memory device. The proposed synapse includes a resistive switching device, a LTP block, a LTD block, and a peripheral circuit. The synapse can modify its weight (i.e., resistance of the resistive memory device) according to a STDP learning rule. The artificial neural network constructed with the designed synapses can learn like a neural system.

#### **II. DESIGN CONSIDERATION**

The synapse was designed and simulated with HSPICE by using a standard  $0.13 \,\mu m$  CMOS process. The resistive memory device model was built with Verilog-AMS, and its device parameters are extracted from Ref. 13. The resistance modification of the resistive memory device is assumed proportional to both pulse amplitude and width. And the device is a bipolar resistive memory, i.e., a positive pulse leads to an increase in its conductance while a negative pulse causes a decrease in the conductance. It is worthy to mention that the design presented in this work can also be implemented with a unipolar resistive memory device by modifying some block parameters.

According to the STDP learning rule, the weight modification of a synapse relies on the timing relationship between pre- and post-synaptic spikes. If the pre-synaptic spike precedes the post-synaptic spike, the strength of the synapse undergoes a LTP. The conductance of the synapse increases, leading to strengthening of the connection between the adjacent neurons. However, if the post-synaptic spike precedes the pre-synaptic spike, a LTD occurs. The conductance of the synapse decreases, leading to reduction of the connection between the adjacent neurons. Furthermore, a shorter time interval between pre-synaptic spike and post-synaptic spike leads to a larger change of the conductance. If the time interval between pre- and post-synaptic spikes is larger than a certain value (i.e., the STDP time window<sup>3,15</sup>), there will be no modifications in synaptic strength.

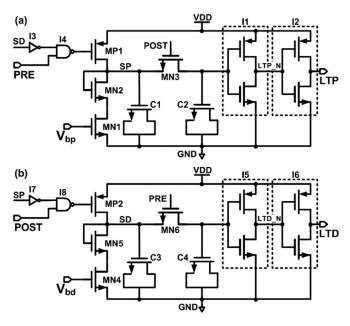

The proposed synapse consists of a LTP block, a LTD block, a resistive memory device, and a peripheral circuit. The LTP block and LTD block are shown in Figs. 1(a) and 1(b), respectively. The topology of the two blocks is actually the same, except that the signals are complementary. Firing of the pre- and post-neurons induces a LTP signal and LTD signal, respectively, following the STDP rule.

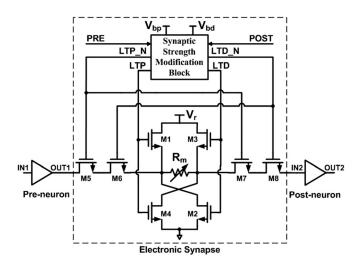

In Fig. 1(a), nodes PRE and POST are connected to the pre-neuron and post-neuron, respectively. At the initial state, nodes SP and SD are both set to low and I4 acts as an inverter. Once the pre-neuron fires, the transistor MP1 is switched on. The capacitor C1 is charged to VDD (supply voltage), and thus the LTP state node SP rises to high, which inhibits NAND I8 in Fig. 1(b) and thus the LTD block from working. As a result, the LTD block is forbidden while the LTP block is working. Afterwards, the capacitor is discharged through transistors MN1 and MN2, and the discharge current is controlled by V<sub>bp</sub>. There is a maximum time for the capacitor discharging called LTP time window. If the post-neuron fires within this window, the charges rearranged to capacitor C2 will turn on the inverter I1, forcing LTP output high. The earlier the post-neuron fires, the longer duration the LTP output keeps at high. If the interval between pre- and post-neuron fires larger than the LTP time window, there is no LTP output. The duration that LTP output keeps at high is approximately inversely proportional to the interval between pre- and postneuron firings. To avoid a sudden voltage reduction on C1 after charge rearrangement, C2 should be at least 10 times smaller than C1. In the case that post-neuron fires first, a similar process occurs in the LTD block, but the LTP block is forbidden while the LTP block is working. A pre-neuron firing within the LTD time window produces a LTD output. The synaptic strength modification block composed of the LTP and LTD blocks is used in the proposed electronic synapse, as illustrated in Fig. 2. The LTP and LTD signals produced by the above two blocks are applied to the resistive memory device, R<sub>m</sub>, as shown in Fig. 2. The resistance of the resistive

FIG. 1. (a) LTP block and (b) LTD block

FIG. 2. Schematic illustration of the designed electronic synapse.

memory device changes with the applied signals and the change depends on the amplitude, width, and polarity of the signals.<sup>13</sup>

During the quiescent state, the LTP and LTD signals are low, while their inverted signals LTP\_N and LTD\_N are high. All the transistors in the path between pre-neuron and post-neuron (M5-M8) remain on, and the spikes produced by pre-neuron can transmit to post-neuron via R<sub>m</sub>. Once the LTP occurs, transistors M1 and M4 are turned on by the LTP signal, and the strength modification voltage V<sub>r</sub> is applied to R<sub>m</sub>. The R<sub>m</sub> resistance is then decreased. When the LTD signal occurs, transistors M3 and M2 are turned on by the LTD signal, a negative V<sub>r</sub> is then applied to R<sub>m</sub>. The R<sub>m</sub> resistance is increased. Whenever LTP or LTD occurs, two transistors among M5-M8 would turn off; therefore, the path between pre-neuron and post-neuron is blocked. It should be noted that the above implementation is applicable to a bipolar resistive memory device. To realize a synapse with unipolar resistive memory device, V<sub>r</sub> should be replaced by two different voltages  $V_{\text{set}}$  and  $V_{\text{reset}}$ on the drains of M1 and M3, respectively.

#### III. SIMULATION RESULTS

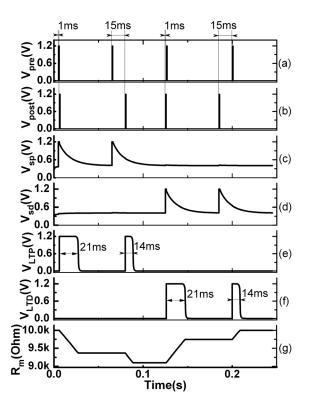

Fig. 3 shows a typical transient response for different spike timing of the pre- and post-neurons. At 5 ms from the beginning, a pre-synaptic spike precedes a post-synaptic spike for 1 ms as shown in Fig. 3(a). A LTP pulse with a width of 21 ms is generated while the LTD channel is prohibited. The resistance of  $R_m$  is reduced from  $10\,k\Omega$  to  $9.3\,k\Omega$  as shown in Fig. 3(g). At 65 ms, another pre-synaptic spike precedes a post-synaptic spike for 15 ms, while the width of the generated LTP pulse is 14 ms. The resistance of R<sub>m</sub> is reduced from  $9.3 \,\mathrm{k}\Omega$  to  $9.1 \,\mathrm{k}\Omega$ . It should be noted that a shorter LTP pulse will be generated with a longer interval between pre-neuron and post-neuron spikes according to STDP. At 125 ms, a post-neuron spike precedes a pre-neuron spike for 1 ms, and a LTD pulse with the width of 21 ms is generated. The resistance of R<sub>m</sub> is increased due to the negative V<sub>r</sub>. At 185 ms, a post-neuron spike precedes a preneuron spike for 15 ms. A LTD pulse of 14 ms is applied on R<sub>m</sub>, leading to increase of R<sub>m</sub> resistance. A longer interval

FIG. 3. (a)  $V_{pre}$ , (b)  $V_{post}$ , (c)  $V_{sp}$ , (d)  $V_{sd}$ , (e)  $V_{LTP}$ , (f)  $V_{LTD}$ , and (g)  $R_m$  in time domain. LTP and LTD are realized with the designed synapse.

between the post- and pre-spikes results in a shorter LTD pulse according to STDP. In Fig. 3(g), the change of the R<sub>m</sub> resistance is proportional to the pulse width of LTP or LTD.

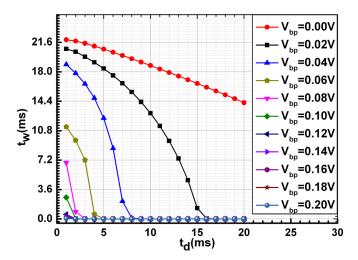

The widths of the LTP and LTD time windows can be adjusted by varying  $V_{bp}$  and  $V_{bd}$ , respectively. Fig. 4 shows the width of LTP pulse  $(t_w)$  as a function of the time interval between pre-neuron spike and post-neuron spike  $(t_d)$  at various  $V_{bp}$ . The width of the LTP time window is the sum of  $t_w$  and  $t_d$ , and it is determined by  $V_{bp}$ . For a fixed  $V_{bp}$ , with the time interval increasing, the LTP pulse width is reduced. When the time interval exceeds the LTP time window, there will be no LTP pulse generated. Similarly, the width of LTD can also be adjusted by the interval between post-neuron and pre-neuron spikes.

FIG. 4. Width of LTP pulse  $(t_w)$  as a function of the interval between preand post-spikes  $(t_d)$  at various  $V_{bp}$ .

FIG. 5. (a) A three-neuron network constructed with the designed synapse; and (b) associative learning realized with the three-neuron network.

In Fig. 5(a), a three-neuron network was constructed to demonstrate the associative learning in a classical conditioning experiment. 16,17 Excitations on IN1 and IN2 represent the unconditioned stimulus (sight of food) and the conditioned stimulus (ringing of bell), respectively. OUT3 represents the response (salivation). Initially, we assume that the connection between neuron 1 and neuron 3 is strong. That means the weight of synapse A is high (i.e., the resistance of  $R_{mA}$  is low). As can be seen in session 1 in Fig. 5(b), the input of unconditioned stimulus (sight of food) leads to the response (salivation). In session 2, there is no response for the input of the conditioned stimulus (ringing of bell) as the weight of the synapse B is low (i.e., the resistance of R<sub>mB</sub> is high). In session 3, OUT3 has an output due to the input of neuron 1. At the same time, there is also input of the conditioned stimulus (ringing of bell) from IN2. Now the conditioned stimulus (ringing of bell) precedes the response (salivation) of synapse B. According to the STDP learning rule, the weight of synapse B increases. As a result, in session 4 the input of the conditioned stimulus (ringing of bell) alone can cause the response (salivation) due to the increase of the weight of synapse B. It is clear from above discussion that the neuron network constructed with the designed synapses can realize the STDP learning. The transistor area of the electronic synapse in the present design is  $4142 \text{ F}^2$  (not including the capacitors) where F is the feature size of the transistors, which is only about 7.6% of that of the design based on the conventional CMOS circuits.<sup>18</sup> If the present design is realized with 90 nm technology, the transistor area is  $\sim 3.4 \times 10^{-7}$  cm<sup>2</sup>, which is acceptable to large-scale integration.

### IV. CONCLUSIONS

A design of electronic synapse based on resistive memory device has been presented in this work. The proposed synapse well imitates the LTP, LTD, and STDP operations. The learning procedure is realized with a three-neuron network based on the designed synapse. The simplicity of the electronic synapse makes it suitable for applications in large scale neural networks.

#### **ACKNOWLEDGMENTS**

This work has been supported by NSFC under Project No. 61274086, the Young Scholar Fund of Sichuan under Project No. 2011JQ0002, and the Fundamental Funds for the Central Universities and NTU Si COE Program.

- <sup>6</sup>A. Hamilton, A. F. Murray, D. J. Baxter, S. Churcher, H. M. Reekie, and L. Tarassenko, IEEE Trans. Neural Networks **3**, 385 (1992).

- <sup>7</sup>M. Holler, S. Tam, H. Castro, and R. Benson, in *International Joint Conference on Neural Networks* (Academic, Washington, DC, USA, 1989), Vol. 2, p. 191.

- <sup>8</sup>S. Ramakrishnan, P. E. Hasler, and C. Gordon, IEEE Trans. Biomedical Circuits Systems **5**, 244 (2011).

- <sup>9</sup>G. S. Snider, in *IEEE/ACM International Symposium on Nanoscale Architectures* (Academic, Anaheim, CA, 2008), p. 85.

- <sup>10</sup>S. Yu, Y. Wu, R. Jeyasingh, D. Kuzum, and H. P. Wong, IEEE Trans. Electron Devices 58, 2729 (2011).

- <sup>11</sup>L. O. Chua, IEEE Trans. Circuit Theory **18**, 507 (1971).

- $^{12}\mathrm{L}.$  O. Chua, Proceedings of the IEEE 91, 1830 (2003).

- <sup>13</sup>D. Strukov, G. Snider, D. Stewart, and R. S. Williams, Nature 453, 80 (2008).

- <sup>14</sup>R. Waser and M. Aono, Nature Mater. **6**, 833 (2007).

- <sup>15</sup>S. Davies, A. Rast, F. Galluppi, and S. Furber, in *The 2011 International Joint Conference on Neural Networks* (Academic, San Jose, CA, USA, 2011), p. 1810.

- <sup>16</sup>E. R. Kandel, J. H. Schwartz, and T. M. Jessell, *Principles of Neural Science*, 4th ed. (McGraw-Hill, New York, 2000).

- <sup>17</sup>K. D. Cantley, A. Subramaniam, H. J. Stiegler, R. A. Chapman, and E. M. Vogel, IEEE Trans. Neural Networks Learn. Syst. 23, 565 (2012).

- <sup>18</sup>J. M. Cruz-Albrecht, M. W. Yung, and N. Srinivasa, IEEE Trans. Medical Circuits Syst. 6, 246 (2012).

<sup>&</sup>lt;sup>1</sup>H. P. Graf, L. D. Jackel, and W. E. Hubbard, Computer **21**, 41 (1988).

<sup>&</sup>lt;sup>2</sup>M. Verleysen, B. Sirletti, A. Vandemeulebroecke, and P. G. A. Jespers, IEEE Trans. Circuits Syst. **36**, 762 (1989).

<sup>&</sup>lt;sup>3</sup>G. Q. Bi and M. M. Poo, J. Neurosci. **18**, 10464 (1998).

<sup>&</sup>lt;sup>4</sup>H. Markram, J. Lubke, M. Frotscher, and B. Sakmann, Science **275**, 213 (1997).

<sup>&</sup>lt;sup>5</sup>G. Q. Bi and M. M. Poo, Annu. Rev. Neurosci. **24**, 139 (2001).