### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

### Self-heating and trapping effect in AlGaN/GaN high electron mobility transistors on CVD-diamond

Kumud Ranjan

2019

Kumud Ranjan. (2019). Self-heating and trapping effect in AlGaN/GaN high electron mobility transistors on CVD-diamond. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/137690

https://doi.org/10.32657/10356/137690

This work is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License (CC BY-NC 4.0).

Downloaded on 03 Apr 2024 11:26:34 SGT

## SELF-HEATING AND TRAPPING EFFECT IN ALGAN/GAN HIGH ELECTRON MOBILITY TRANSISTORS ON CVD-DIAMOND

Kumud Ranjan G1600672J

SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING

2019

# SELF-HEATING AND TRAPPING EFFECT IN ALGAN/GAN HIGH ELECTRON MOBILITY TRANSISTORS ON CVDDIAMOND

### **KUMUD RANJAN**

School of Electrical & Electronic Engineering

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2019

### **Statement of Originality**

I hereby certify that the work embodied in this thesis is the result of original research, is free of plagiarized materials, and has not been submitted for a higher degree to any other University or Institution.

| 30.12.2019 | Knemed Rassjan |

|------------|----------------|

|            |                |

| Date       | Kumud Ranjan   |

### **Supervisor Declaration Statement**

I have reviewed the content and presentation style of this thesis and declare it is free of plagiarism and of sufficient grammatical clarity to be examined. To the best of my knowledge, the research and writing are those of the candidate except as acknowledged in the Author Attribution Statement. I confirm that the investigations were conducted in accord with the ethics policies and integrity standards of Nanyang Technological University and that the research data are presented honestly and without prejudice.

30-12-2019

Date

Prof. Ng Geok Ing

### **Authorship Attribution Statement**

This thesis contains material from 5 paper(s) published in the following peer-reviewed journals and from papers accepted at conferences in which I am listed as an author.

### Chapter 3 includes 2 publications

- K. Ranjan, S. Arulkumaran, G. I. Ng, Sandupatla. A, "Investigations of self-heating effect in AlGaN/GaN HEMT on CVD diamond," *Electron device society (J-EDS)*, Vol. 7, pp. 1264-1269,2019.

- K. Ranjan, G. I. Ng, S. Arulkumaran, S. Vicknesh, and S. C. Foo, "Enhanced DC and RF performance of AlGaN/GaN HEMTs on CVD-Diamond in high power CW operation". in Electron Devices Technology and Manufacturing (EDTM), Mar. 2019, Singapore

### The contributions of the co-authors are as follows:

- I co-designed this project with Prof. G. I. Ng, and Dr. S. Arulkumaran and performed all laboratory works including design, device fabrication, simulation, measurements, analysis and preparation of manuscript drafts.

- Prof. G. I. Ng provided valuable guidance and funding support for semiconductor wafer and edited the manuscript drafts.

- Dr S. Arulkumaran assisted with epitaxy wafer which was used for device fabrication. He also provided direction of study and research and assisted in edited manuscript drafts.

- S. Vicknesh and S.C Foo helped in the study of epitaxy properties and initial fabrication of devices and edited the manuscript drafts.

- A. Sandupatla assisted in part of characterization of device and helped in editing the manuscript drafts.

### Chapter 4 includes 2 publications

- K. Ranjan, S. Arulkumaran, G. I. Ng, "Investigations of temperature-dependent interface traps in AlGaN/GaN HEMT on CVD-diamond," *Applied Physics Express*, 12,10, 2019.

- K. Ranjan, S. Arulkumaran, G. I. Ng, S. Vicknesh and K.S. Ang, "Self-heating effects in DC and RF performances of 0.25 μm T-Gate AlGaN/GaN HEMTs on Silicon and CVD-Diamond," at 12th Topical Workshop on Heterostructure Microelectronics (TWHM), Aug 2017, Kirishima, Japan

### The contributions of the co-authors are as follows:

- I co-designed this project with Prof. G. I. Ng and performed all laboratory work including measurements, analysis and preparation of manuscript drafts.

- Prof. G. I. Ng provided valuable guidance, assisted in interpretation of results and edited the manuscript drafts.

- Dr S. Arulkumaran provided initial project direction, assisted with the analysis and edited manuscript drafts.

- S. Vicknesh and K.S. Ang helped in the study of epitaxy properties and initial fabrication of devices, and edited the manuscript drafts.

Chapter 5 includes 1 publication

Chapter 5 was accepted as;

**K. Ranjan**, S. Arulkumaran, G. I. Ng and A. Sandupatla "Investigations of interface traps in AlGaN/GaN MIS-HEMTs on CVD-Diamond" in Electron Devices Technology and Manufacturing (EDTM) Conference – 2020, Malaysia.

The contributions of the co-authors are as follows:

- I co-designed this project with Prof. G. I. Ng and Dr. Arul, and performed all laboratory work including measurements, analysis and preparation of manuscript drafts.

- Prof. G. I. Ng provided valuable guidance, assisted in interpretation of results and edited the manuscript drafts.

- Dr S. Arulkumaran provided initial project direction, assisted with the analysis and edited manuscript drafts.

- A. Sandupatla helped in the measurement setup and edited the manuscript drafts.

| 30.12.2019 | Krumud Rassjan |

|------------|----------------|

|            |                |

| Date       | Kumud Ranian   |

### **Acknowledgments**

First, I would like to express my sincere gratitude to my supervisor Prof. Ng Geok Ing for his guidance, all-around support, and encouragement throughout my Ph.D. program. His foresight and experience helped to steer this project. They brought me into the field of III-V semiconductor transistors for high-frequency application, especially in small-signal behavior of transistors. His continuous motivation has been a tremendously positive influence on me to complete this work successfully. I would like to thank my mentor Dr. Subramaniam Arulkumaran for sharing knowledge and guidance through his vast experience and technical expertise. His guidance in organizing and scrutinizing my work helped me in order to make it worthy of publications in international journals and conferences.

My special thanks to Microsystem Technologies Development Centre (MTDC) in Temasek Laboratories at Nanyang Technology University for the support in device fabrication and characterization. Special appreciation goes to MTDC members, S. Vicknesh, Brayan, Siew Chuen, Li Huang, K. S. Ang, Manoj Kumar, Imran, Louis, Darren for their support and help in the fabrication of the devices that form the very basis of my thesis.

In addition, I would like to thank my team members A. Sandupatla, Matthew Whiteside, Dr. Li Yang, Dr. Weichuan, and, most importantly, Dr. Liu Zhihong for their valuable help and advice during this work.

I would also like to thank Shashank Patwal for his throughout support in academic session during Ph.D. course work in NTU, and other friends Dr. Binit Shyamal, Dr. Nandan, Dr. Kushal, Dr. Pawan whose moral support remained unaccountable during the period of this work.

I would also like to express my sincere gratitude to device characterization labs in NTU, Silicon Technologies Center of Excellence (Si-COE), CNRS-International-NTU-Thales Research Alliance (CINTRA) and all lab staff in N2FC CR2, especially Shamsul, Zulkiflee Abdullah, Dr. Gong Yih, Chung Kwok Fai and Irene for their valuable help in providing the uninterrupted maintenance of cleanroom facilities during device fabrication.

Above all, I would like to express my sincere gratitude to my family members, who provided moral support and strength to accomplish my work.

### **Table of Contents**

| St  | atemer     | nt of Originality                                                 | iii   |

|-----|------------|-------------------------------------------------------------------|-------|

| Su  | pervis     | or Declaration Statement                                          | iv    |

| Αι  | ıthorsh    | nip Attribution Statement                                         | V     |

| Αc  | knowl      | edgments                                                          | .viii |

| Та  | ble of     | Contents                                                          | X     |

| Ak  | stract     |                                                                   | xii   |

| Lis | st of Fi   | gures                                                             | .xvi  |

| Lis | st of Ta   | ablesx                                                            | xiv   |

| 1   | Intro      | oduction                                                          | 1     |

|     | 1.1        | GaN HEMT technology: An overview                                  | 1     |

|     | 1.2        | Issues in GaN HEMT for High Power Density Operation               | 6     |

|     | 1.2.1      | Self-heating in GaN HEMTs                                         | 6     |

|     | 1.2.2      | Trapping Effect in GaN HEMTs                                      | 11    |

|     | 1.3        | Motivation and Objective                                          | 14    |

|     | 1.4        | Major contribution of the thesis                                  |       |

|     | 1.5        | Thesis Outline                                                    | 17    |

| 2   | AIG        | aN/GaN HEMTs, Self-heating and trapping mechanism                 | 19    |

|     | 2.1        | Introduction                                                      | 20    |

|     |            | AlGaN/GaN HEMT Principle                                          |       |

|     | 2.3        | The self-heating in AlGaN/GaN HEMTs                               | 33    |

|     | 2.4<br>HEN | Electrical characterization and self-heating of AlGaN/GaN<br>//Ts | 36    |

|     | 2.4.1      | DC measurements of AlGaN/GaN HEMTs                                | 36    |

|     | 2.4.2      | RF characterization                                               | 40    |

|     | 2.5        | Trapping effects in AlGaN/GaN HEMTs                               | 49    |

|     | 2.6        | Trapping characterization techniques                              | 53    |

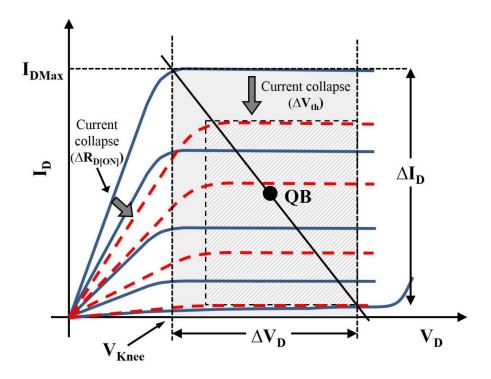

|     | 2.6.1      | Pulsed I <sub>D</sub> -V <sub>D</sub> characterization            | 53    |

|     | 2.6.2      | Conductance frequency technique                                   | 59    |

| 3   | Self       | -heating in GaN HEMTs on Si and CVD diamond                       | 66    |

|     | 3.1        | Introduction                                                      | 66    |

|      | 3.2        | AlGaN/GaN HEMT structure and device fabrication     | 68   |

|------|------------|-----------------------------------------------------|------|

|      | 3.3        | DC characterization and self-heating analysis       | 74   |

|      | 3.4        | TCAD simulation and Junction temperature estimation | 81   |

|      | 3.5        | RF characteristics and Self-heating analysis        | 87   |

|      | 3.6        | Summary                                             | 98   |

| 4    | Hete<br>99 | ero-interface trap in AlGaN/GaN HEMTs -on-CVD diamo | nd   |

|      | 4.1        | Introduction                                        | 99   |

|      | 4.2        | AlGaNGaN HEMTs-on-CVD diamond: Device fabrication   | .100 |

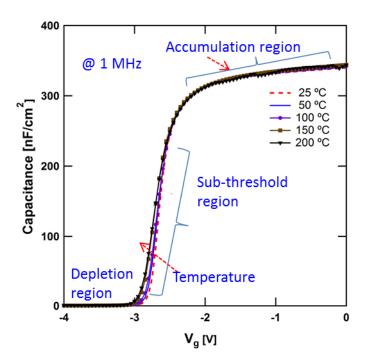

|      | 4.3        | C-V characteristics                                 | .104 |

|      | 4.4        | G-f characteristics and trap density estimation     | .106 |

|      | 4.5        | Pulsed-IV characteristics                           | .115 |

|      | 4.6        | Summary                                             | .119 |

| 5    | Inte       | rface trap in AlGaN/GaN MIS-HEMTs -on-CVD diamond.  | .121 |

|      | 5.1        | Introduction                                        | .121 |

|      | 5.2        | Device fabrication                                  | .123 |

|      | 5.3        | DC characteristics                                  | .127 |

|      | 5.4        | C-V characteristics                                 | .131 |

|      | 5.5        | G-f characteristics and Trap density estimation     | .132 |

|      | 5.6        | Summary                                             | .138 |

| 6    | Con        | clusions and Recommendations for future work        | .139 |

|      | 6.1        | Conclusions                                         | .139 |

|      | 6.2        | Key contributions of this work                      | 142  |

|      | 6.3        | Recommendations for Future Work                     | .144 |

| Auth | or's       | Publication                                         | 146  |

| RIRI | IOG        | RAPHY                                               | 151  |

### **Abstract**

GaN-based high-electron-mobility Transistors (HEMTs) are widely used for high frequency, high voltage and high-power applications. However, there are still many major challenges facing these devices such as thermal management, size reduction and long-term reliable operation, especially when they are operating at very high voltage (e.g., V<sub>D</sub>≥48 V). In such an operating condition, the device suffers substantial self-heating and encounters enhanced phonon scattering, which degrades device current due to the decrease of 2-DEG mobility and electron velocity as a result of the increased junction temperature. These problems are predominant particularly when GaN HEMTs are fabricated on conventional low thermal conductive substrates (e.g., Si (Ksi=130 W/m-K), Sapphire (Ksa=46 W/m-K) and SiC (Ksic= 450 W/m-K)).

The usage of high thermal conductivity substrates such as diamond (1000-2000 W/m-K) is now emerging as a viable technique to extract the heat under high-power operations for GaN-based high-electron-mobility transistors (HEMTs). Typically, for GaN-on-Diamond process development, both the host Si or SiC substrate and the growth-defect-rich stress mitigation transition layers are first removed. The remaining HEMT layers are then bonded onto CVD-diamond, which then acts as the new substrate. Thus, the HEMTs fabricated on transferred GaN-on-Diamond

will have different behaviour of self-heating and trapping than that of conventional HEMTs fabricated on GaN-on-Si.

In this thesis, the main objectives are to investigate the self-heating effect on DC and RF performance, and the trapping behaviour in GaN HEMTs-on-CVD Diamond.

The major contributions of this thesis are summarized below:

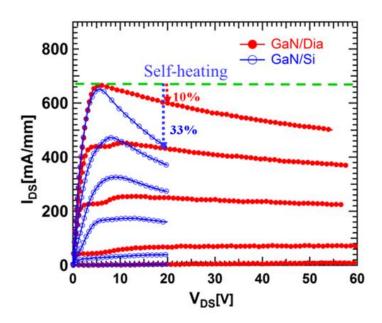

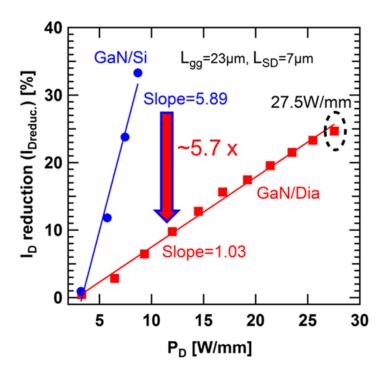

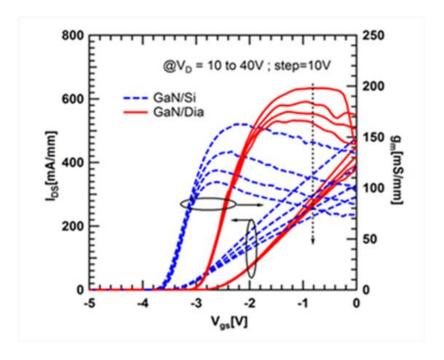

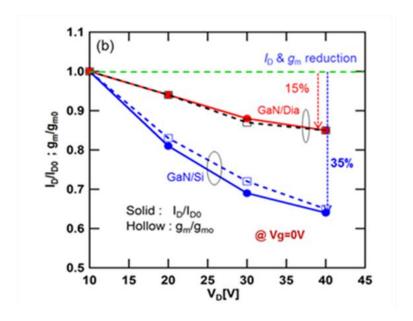

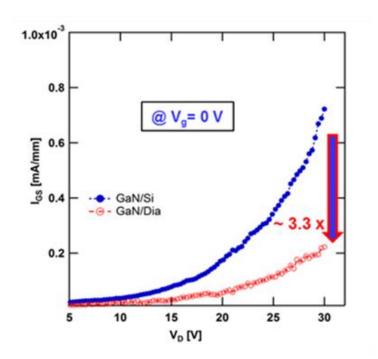

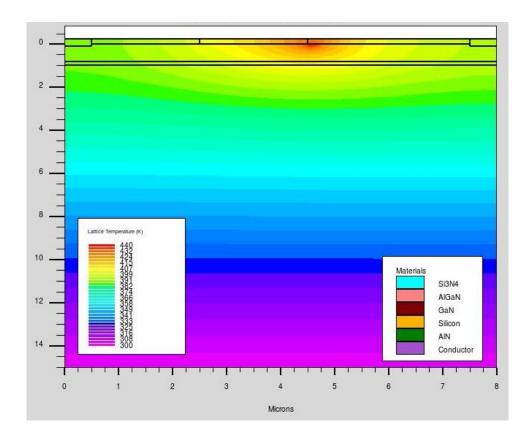

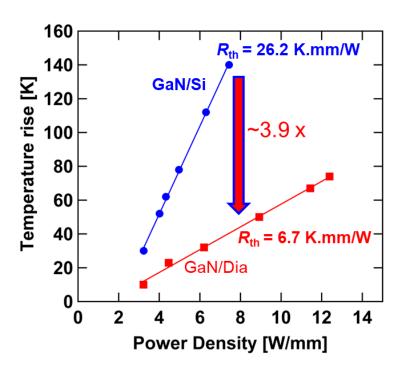

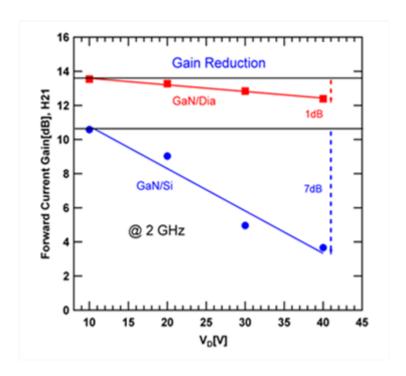

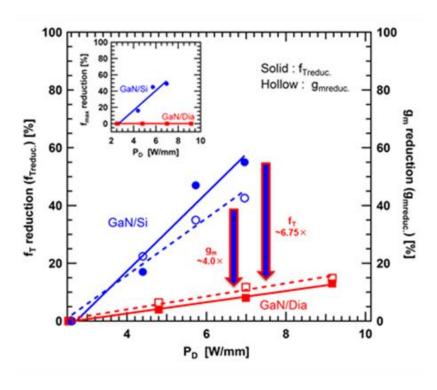

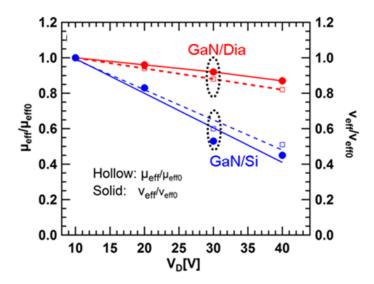

(1) The quantitative investigation of the self-heating effect on DC and RF performances was carried out for AlGaN/GaN HEMTs on CVD-Diamond (GaN/Dia) and Si (GaN/Si) substrates. The GaN/Dia HEMTs were found to exhibit ~5.7-times lower rate of *I*<sub>D</sub> reduction than GaN/Si HEMTs. This behaviour was also confirmed by 2D device simulation. The *f*<sub>T</sub> reduction rate was ~6.75-times lower in the case of GaN/Dia than GaN/Si HEMTs whereas no significant reduction of *f*<sub>max</sub> was observed in GaN/Dia HEMTs. Small signal measurements and equivalent circuit parameter extraction were done to analyze the variation in the performance of the devices. The comparatively lower reduction rate of μ<sub>eff</sub> and ν<sub>eff</sub> in GaN/Dia HEMTs made its performance less degraded (~15%) as compared to (~50%) GaN/Si HEMTs. These results show that GaN/Dia HEMTs can be operated even at higher *V*<sub>D</sub> as well as at higher *P*<sub>D</sub> which are paramount features for developing compact high power SSPAs for CW application.

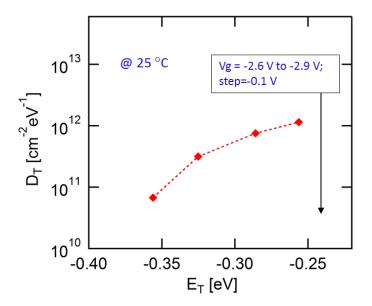

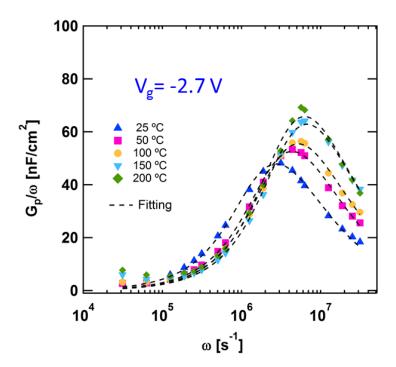

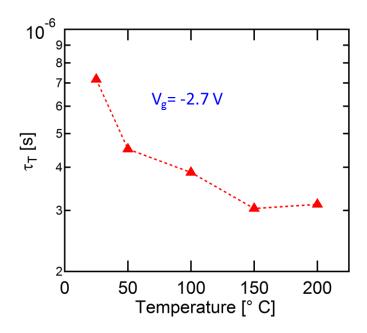

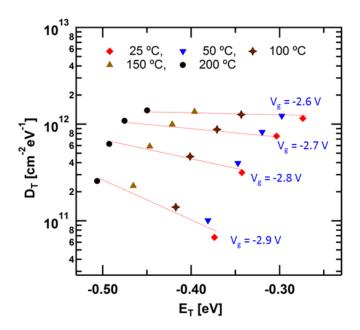

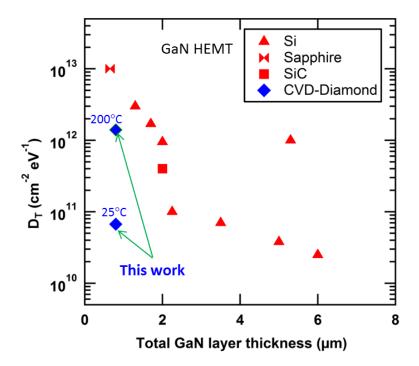

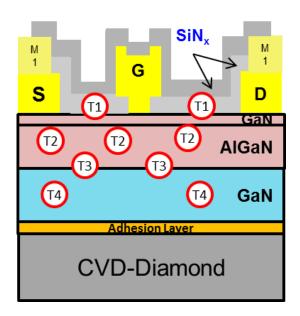

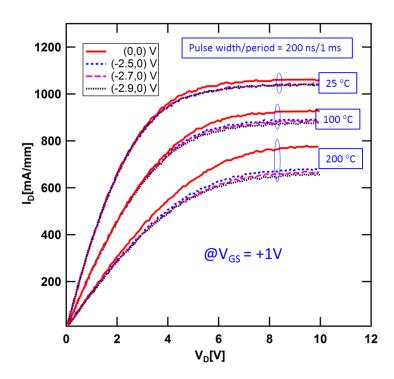

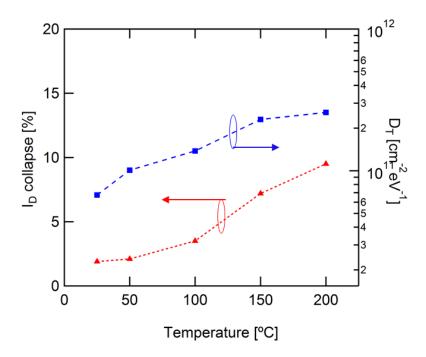

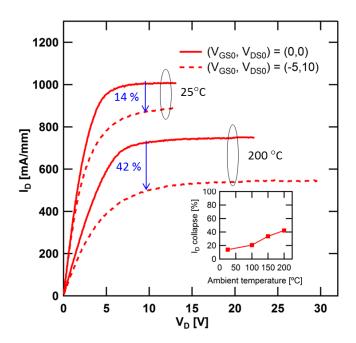

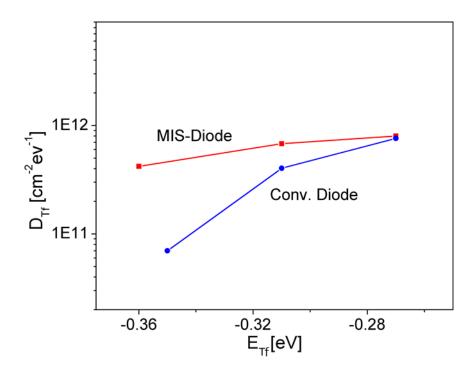

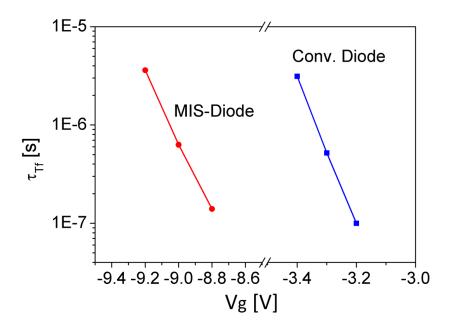

- (2) The hetero-interface trapping characteristics in AlGaN/GaN HEMT on CVD-diamond were investigated at different temperatures (25 °C to 200 °C) using the conductance method. The fast traps (0.16 to 10.01 µs) were identified as the dominating traps in our HEMT structure. The density of fast traps ( $D_{Tf}$ ) increases with temperature from 6.7×10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup> at 25 °C to 1.4×10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup> at 200 °C. For 25 °C to 200 °C, the interface trap state energy ( $E_T$ ) was obtained to be between 0.27 and 0.51 eV below the conduction band. The observation of increased  $D_T$  with temperature could be due to the excitation of additional traps deeper in the bandgap. A lower value of D<sub>Tfmin</sub> for GaN-on-CVD Diamond compared to GaN on Silicon devices is attributed to the removal of the defect-rich GaN transition layer during the substrate transfer process. Finally, temperature-dependent pulsed IDS-VDS measurements revealed good agreement with the behaviour of  $D_T$  with temperature obtained using the conductance method. Further to improve the device performance, GaN-MISHEMTs-on-CVD diamond was fabricated and analyzed the  $g_{\rm m}$  linearity, gate leakage, and interface trap behavior.

- (3) For the first time, the investigation of interface traps in AlGaN/GaN metal-insulator-semiconductor (MIS) HEMTs on CVD-diamond was reported in this work. The critical issue in MIS-HEMTs is the dielectric

interface trap behaviour. The detailed investigation of dielectric interface and hetero-interface is carried out in AlGaN/GaN MISHEMTs on CVD-diamond and compared with the conventional Schottky AlGaN/GaN HEMTs on CVD-diamond. The finding of slow and fast type of traps in MISHEMTs on the contrary to only fast traps in conventional HEMTs indicated the source of traps. Such a study of interface trap behaviour in the device will help to identify and improve the reliability of AlGaN/GaN HEMTs and MISHEMTs-on-CVD diamond.

### **List of Figures**

| Figure 1.1 GaN material merits compared to Si and GaAs3                       |

|-------------------------------------------------------------------------------|

| Figure 1.2 Characteristics and applications areas of GaN HEMT4                |

| Figure 1.3 Some RF application spectrum showing RF power                      |

| requirements as well as power frequency limits of Si, GaAs and GaN-           |

| based power devices5                                                          |

| Figure 1.4 Advantage of GaN technology for power amplifiers (PAs) with        |

| efficient reduced size6                                                       |

| Figure 1.5 Schematic cross-section diagram of conventional AlGaN/GaN          |

| HEMTs showing the heat-spreading path from top and                            |

| bottom7                                                                       |

| Figure 1.6 Schematic cross-sectional diagram of AlGaN/GaN HEMT on             |

| Si, illustrating the possible locations of traps11                            |

| Figure 1.7. Illustration of the shallow and deep trap energy level in the     |

| bandgap12                                                                     |

| Figure 1.8 Schematic cross-section diagram of conventional GaN HEMTs-         |

| on-Si and GaN HEMTs-on-CVD diamond showing the major changes                  |

| during the wafer transfer process13                                           |

| Figure 2.1 Crystal structure and polarization field in (a) Ga-face and (b) N- |

| face GaN19                                                                    |

| Figure 2.2 Spontaneous- and piezoelectric-polarization and the                |

| polarization induced sheet charge in AlGaN/GaN heterostructures with (a)      |

| Ga-face and (b) N-face21                                                      |

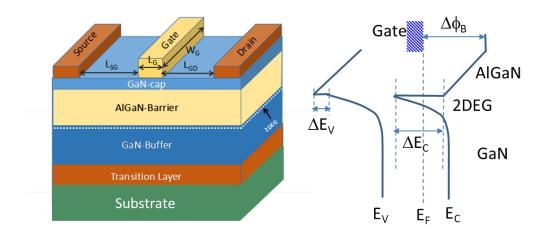

| Figure 2.3 The schematic cross-section and respective energy band             |

| diagram of a typical AlGaN/GaN HEMT22                                         |

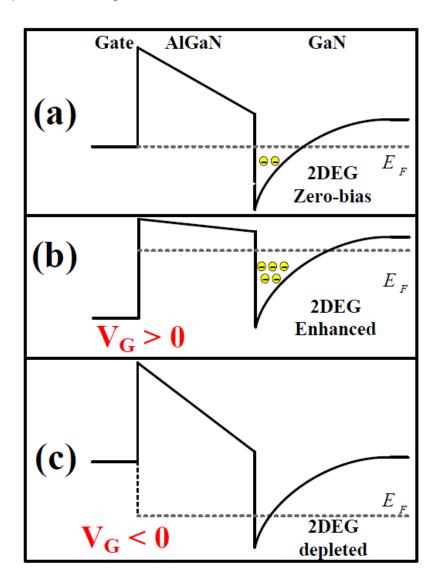

| Figure 2.4 The energy band diagram of AlGaN/GaN HEMTs at (a)                  |

| unbiased gate (b) positive gate bias, and (c) negative gate bias25            |

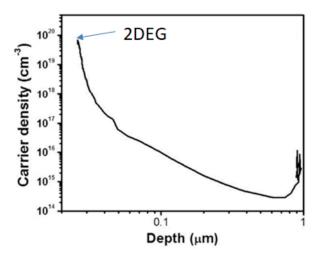

| Figure 2.5 Typical depth versus carrier density profile of AlGaN/GaN          |

| HEMT26                                                                        |

| Figure 2.6.: Temperature dependence sheet carrier density $(n_{\scriptscriptstyle S})$ and |

|--------------------------------------------------------------------------------------------|

| mobility (μ) and R <sub>sh</sub> of AlGaN/GaN HEMT27                                       |

| Figure 2.8 The schematic of AlGaN/GaN HEMTs with a bias terminal for                       |

| DC I-V characteristics                                                                     |

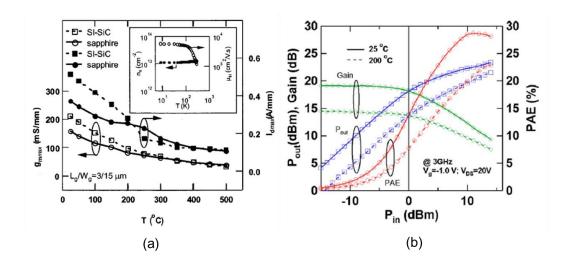

| Figure 2.9 (a) The 2-DEG mobility and (b) RF power performance                             |

| degradation with the increase of temperature in GaN HEMTs-on-Si and                        |

| SiC substrates31                                                                           |

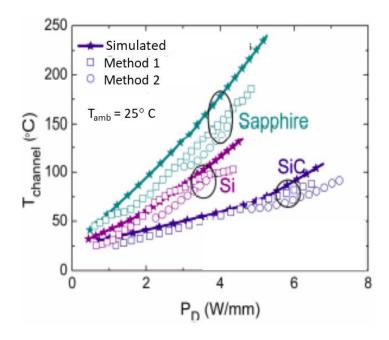

| Figure 2.10 Comparison of the channel temperature versus dissipated                        |

| power density (PD) in GaN HEMTs on Sapphire, Si and SiC substrates                         |

|                                                                                            |

| Figure 2.11 The typical block diagram of DC measurement setup34                            |

| Figure 2.12 Typical DC I₀-V₀ output curve characteristics of AlGaN/GaN                     |

| HEMTs35                                                                                    |

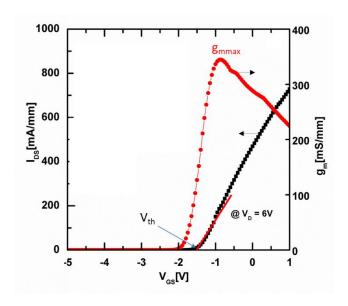

| Figure 2.13 DC $I_D$ - $V_G$ transfer characteristics of AlGaN/GaN HEMTs35                 |

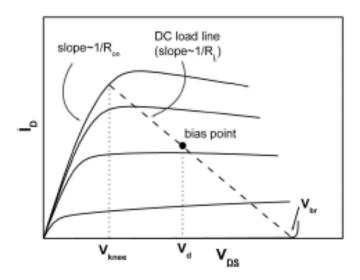

| Figure 2.14 Load line in typical DC output characteristics of a Class A                    |

| power amplifier36                                                                          |

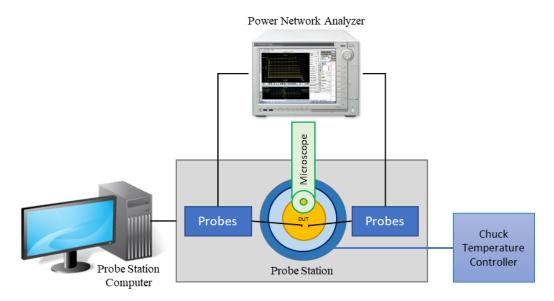

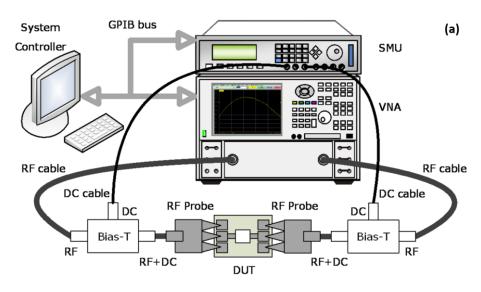

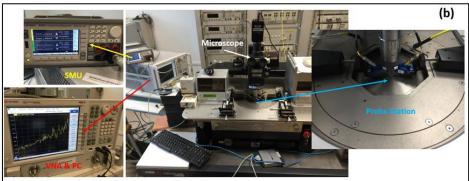

| Figure 2.15 (a) A schematic of measurement setup and (b) actual image                      |

| for on-wafer RF characterization of the device38                                           |

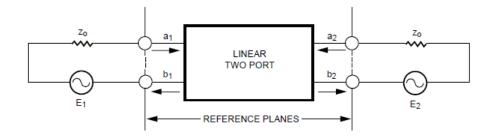

| Figure 2.16 A typical diagram of a two-port network39                                      |

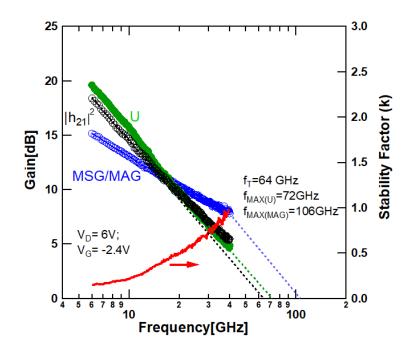

| Figure 2.17 A typical gain versus frequency plots for the determination of                 |

| $f_T$ and $f_{max}$                                                                        |

| Figure 2.18 The schematic of the cross-section and the physical origins of                 |

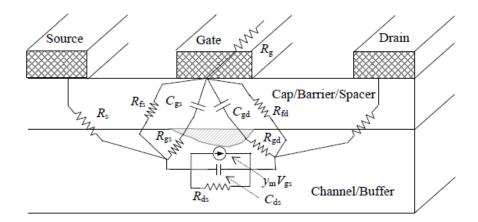

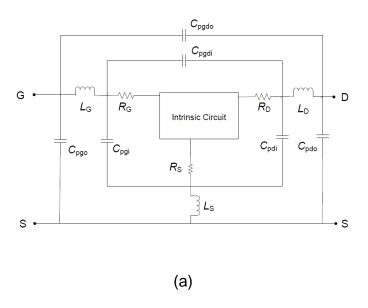

| the small-signal equivalent circuit for a GaN HEMT42                                       |

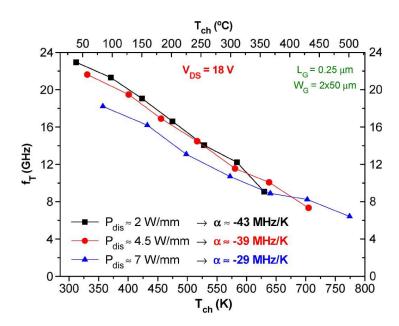

| Figure 2.19 Dependence of $f_T$ with the channel temperature at different                  |

| dissipated powers. The lowering of $f_{\mathcal{T}}$ is related to self-heating and        |

| parasitic effects43                                                                        |

| Figure 2.20 (a) Extrinsic elements and (b) intrinsic elements of a small                   |

| signal equivalent circuit of a GaN HEMTs44                                                 |

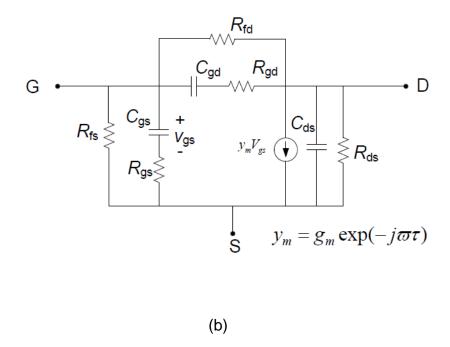

| Figure 2.21 Schematic of the AlGaN/GaN heterostructure showing various                     |

| trapping mechanisms47                                                                      |

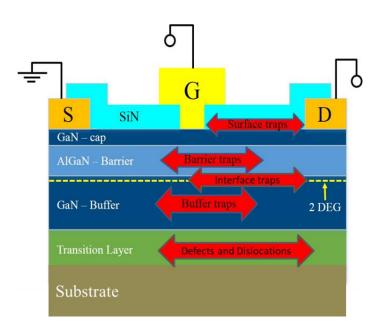

| Figure 2.22 A plot of $I_D$ - $V_D$ characteristics for HEMTs before (solid lines)      |

|-----------------------------------------------------------------------------------------|

| and after (graded lines) current collapse at some stress condition. Shifting            |

| the $V_{\rm knee}$ and reducing the $I_{\rm Dmax}$ will degrade the maximum attainable  |

| device output-power50                                                                   |

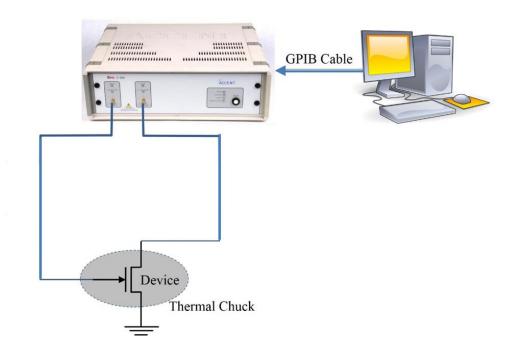

| Figure 2.23 Pulsed $I_{\text{D}}-V_{\text{D}}$ setup for GaN HEMT characterization with |

| Accent Diva D265 analyzer54                                                             |

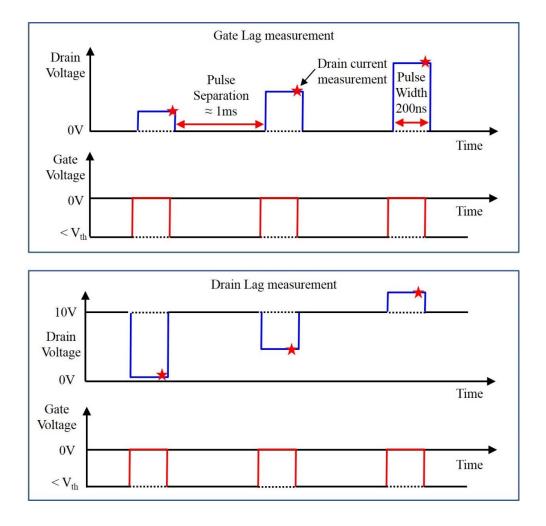

| Figure 2.24 The applied voltage and time plot for pulsed $I_{D}-V_{D}\text{for gate}$   |

| lag condition and drain lag condition55                                                 |

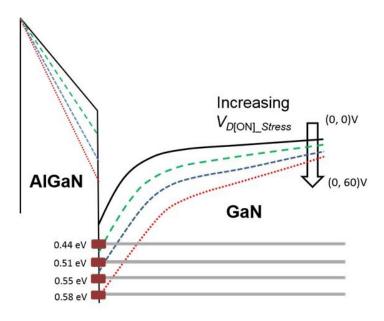

| Figure 2.25 Schematic representation of AlGaN/GaN heterojunction                        |

| energy band bending with different VDS0 stress conditions and the                       |

| distribution of traps in the GaN energy band-gap57                                      |

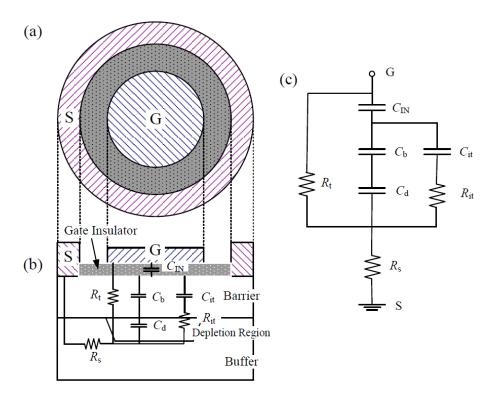

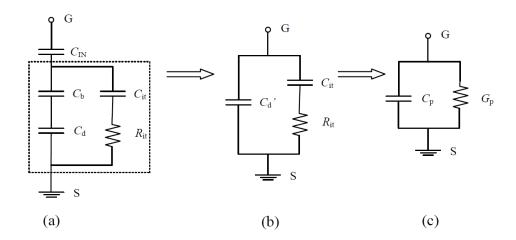

| Figure 2.26 The typical schematic and equivalent circuit of a Metal-                    |

| insulator-Semiconductor (MIS) diode: (a) the top view of the layout for a               |

| typical circular MIS diode; (b) the cross-section and equivalent circuit                |

| element distribution; (c) the equivalent circuit topology57                             |

| Figure 2.26 Simplified equivalent circuit of a diode for interface trap                 |

| density calculation by AC conductance method, where $\emph{G}_{\text{P}}$ is parallel   |

| conductance which is measured at a wide range of frequencies by                         |

| conductance frequency technique62                                                       |

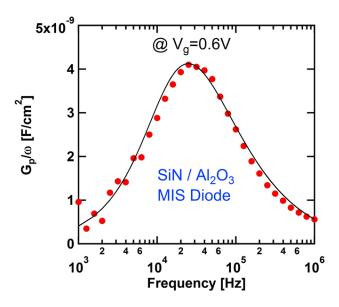

| Figure 2.27 Frequency-dependent conductance as a function of radial                     |

| frequency63                                                                             |

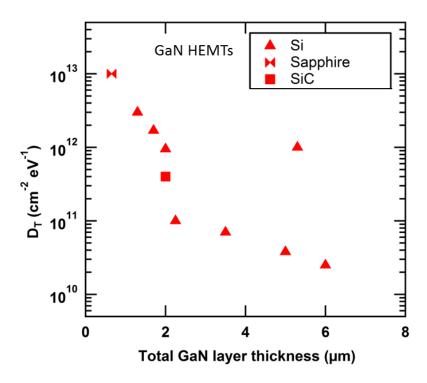

| Figure 2.28 A comparative chart of interface trap density (Dit), estimated              |

| using the conductance method, in conventional AlGaN/GaN HEMT on                         |

| various substrates64                                                                    |

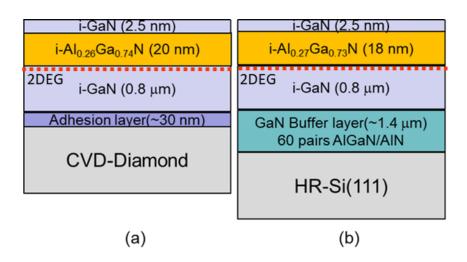

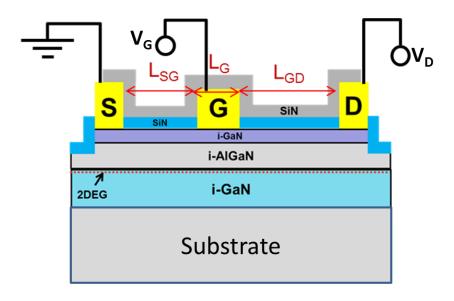

| Figure 3.1: Cross-sectional schematic diagram of AlGaN/GaN HEMT on                      |

| (a) CVD-Diamond substrate (b) Si (111) substrate68                                      |

| Figure 3.2 Process flow used in the device fabrication of 2- $\mu m$ gate               |

| AIGaN/GaN HEMTs-on-Si and CVD substrate70                                               |

| Figure 3.3 Cross-sectional schematic diagram of AlGaN/GaN HEMTs                         |

| device                                                                                  |

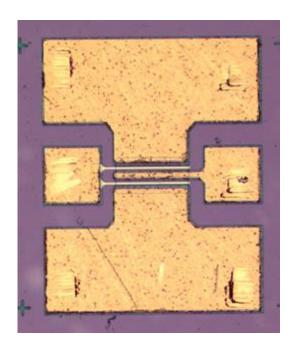

| Figure 3.4 Optical microscope image of fabricated AlGaN/GaN HEMTs-                                            |

|---------------------------------------------------------------------------------------------------------------|

| on-CVD diamond74                                                                                              |

| Figure 3.5: $I_{\rm DS}$ - $V_{\rm DS}$ of GaN/Dia and GaN/Si HEMTs. Device dimensions:                       |

| $L_{sg}/W_g/L_g/L_{gd} = 2/(2\times100)/2/3$ with gate to gate pitch ( $L_{gg}$ ) =23 um75                    |

| Figure 3.6 $I_D$ reduction ( $I_{Dreduc.}$ ) versus DC $P_D$ of GaN/Dia and GaN/Si                            |

| HEMTs. Device dimensions: $L_{\rm sg}/W_{\rm g}/L_{\rm g}/L_{\rm gd}$ =2/(2×100)/2/3 with $L_{\rm gg}$ =23 µm |

| 76                                                                                                            |

| Figure 3.7 Transfer characteristics of GaN/Dia and GaN/Si HEMTs at                                            |

| different $V_D$                                                                                               |

| Figure 3.8 Normalized $I_{dmax}$ and $g_{mmax}$ reduction at different $V_D$ of GaN/Dia                       |

| and GaN/Si HEMTs at different V <sub>D</sub> 78                                                               |

| Figure 3.9 Gate current characteristics of GaN/Dia and GaN/Si HEMTs                                           |

| with $V_D$ at $V_G = 0 \text{ V}$ 80                                                                          |

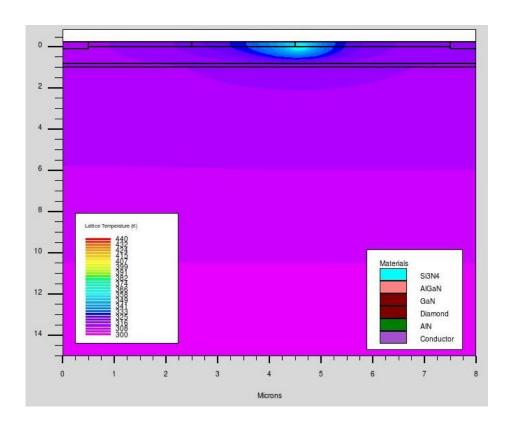

| Figure 3.10 Cross-sectional thermal profile by 2D simulation for GaN/Si                                       |

| HEMT82                                                                                                        |

| Figure 3.11 Cross-sectional thermal profile by 2D simulation for GaN/Dia                                      |

| HEMTs83                                                                                                       |

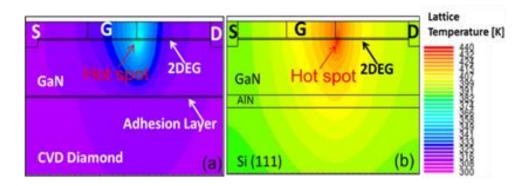

| Figure 3.12 TCAD Simulated cross-sectional thermal profile for (a)                                            |

| GaN/Dia, (b) GaN/Si at $V_D = 20V$ , $V_G = +1V$ 84                                                           |

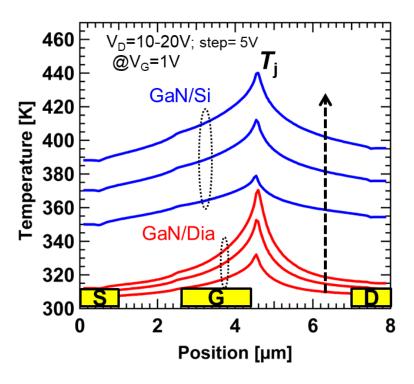

| Figure 3.13 TCAD Simulated device temperature profile across the                                              |

| source-drain region for different $V_D$ =10, 15, and 20 V (d) $\Delta T_j$ versus $P_D$ of                    |

| GaN/Dia and GaN/Si HEMTs84                                                                                    |

| Figure 3.14 TCAD Simulated $\Delta T_{\rm j}$ versus $P_{\rm D}$ of GaN/Dia and GaN/Si                        |

| HEMTs86                                                                                                       |

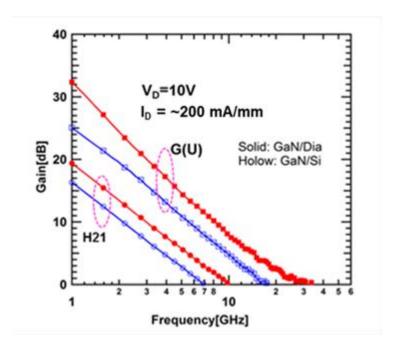

| Figure 3.15 Small-signal microwave characteristics of GaN/Dia and                                             |

| GaN/Si HEMTs of a 2-µm gate device87                                                                          |

| Figure 3.16 Current gain ( $H_{21}$ ) of GaN/Dia and GaN/Si HEMTs for different                               |

| $V_{\rm D}$ of a 2-µm gate GaN/Dia and GaN/Si HEMTs88                                                         |

| Figure 3.17 The $f_T$ reduction ( $f_{Treduc.}$ ) and $g_{mmax}$ reduction ( $g_{mreduc.}$ ) versus    |

|--------------------------------------------------------------------------------------------------------|

| $P_{D}$ of GaN/Dia and GaN/Si HEMTs. Inset: $f_{max}$ reduction ( $f_{maxreduc}$ .) versus             |

| <i>P</i> <sub>D</sub> for GaN/Dia and GaN/Si HEMTs90                                                   |

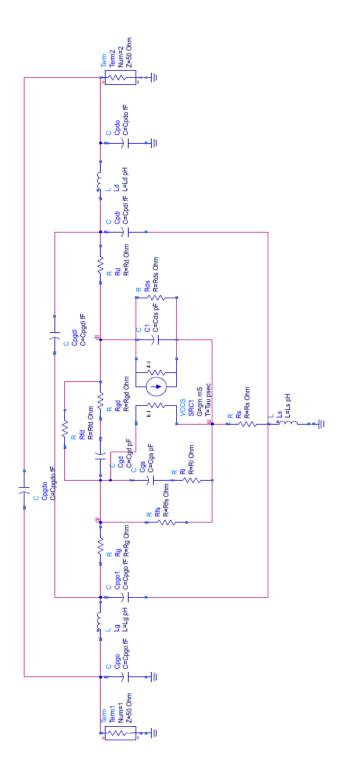

| Figure 3.18 The small-signal equivalent circuit of 22-elements GaN HEMT                                |

| modelled in ADS circuit simulator. Circuit elements are been described in                              |

| chapter 292                                                                                            |

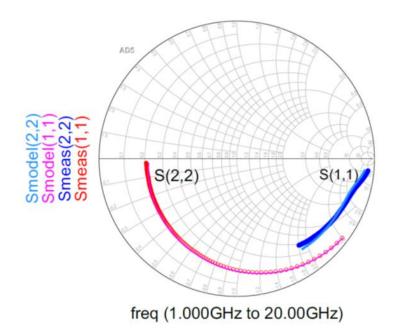

| Figure 3.19 A comparison of the measured and modelled S-parameters                                     |

| for a GaN HEMTs-on-CVD diamond with a bias condition of $V_D$ = 10 V and                               |

| $I_{\rm D}$ ~ 200 mA/mm. (a) shows the S11 and S22, and (b) shows the S12 and                          |

| S21 plot in smith chart93                                                                              |

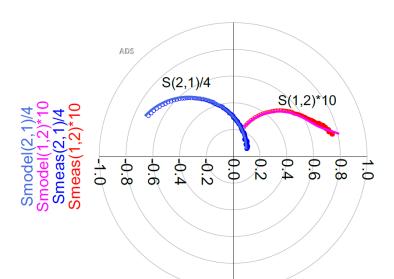

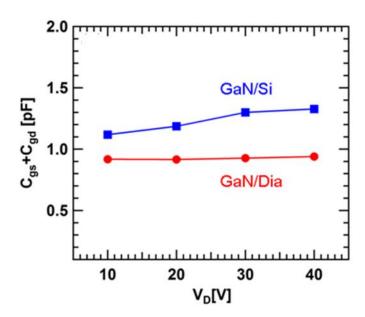

| Figure 3.20 Extracted gate capacitance from measured small-signal                                      |

| characteristics GaN/Dia and GaN/Si HEMTs94                                                             |

| Figure 3.21 Extracted normalized effective carrier mobility ( $\mu_{	ext{eff}}$ ) and                  |

| effective carrier velocity ( $v_{	ext{eff}}$ ) versus drain bias characteristics $V_{	ext{D}}$ of a 2- |

| µm gate GaN/Dia and GaN/Si HEMTs96                                                                     |

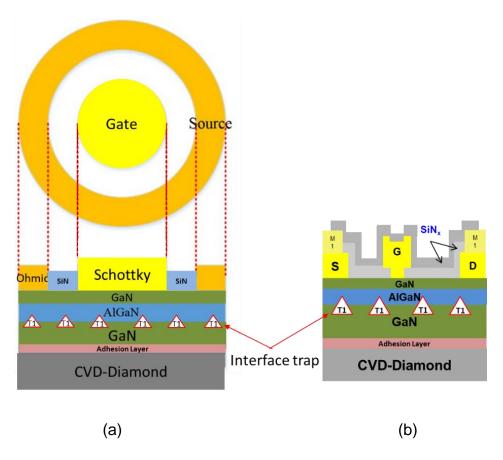

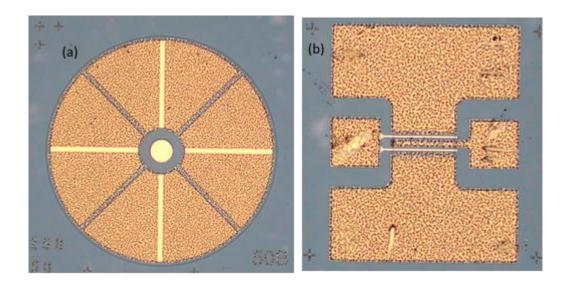

| Figure 4.1 Schematic cross-sectional diagram of the fabricated (a)                                     |

| Schottky diodes and (b) 0.25-um gate AlGaN/GaN HEMT on CVD-                                            |

| Diamond101                                                                                             |

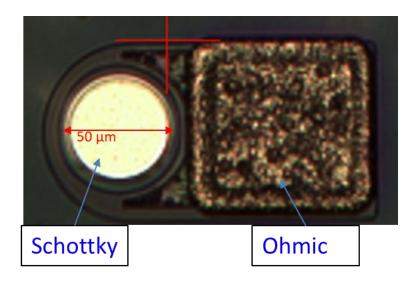

| Figure 4.2 Optical microscope image of fabricated AlGaN/GaN Schottky                                   |

| diode on CVD diamond102                                                                                |

| Figure 4.3 Optical microscope image of fabricated AlGaN/GaN HEMTs on                                   |

| CVD diamond, showing source (S), Gate (G), and Drain electrode (D)                                     |

| 103                                                                                                    |

| Figure 4.4 Normalized C-V characteristics of AlGaN/GaN Schottky diode-                                 |

| on-CVD diamond at 1 MHz for different temperatures (25 - 200 $^{\circ}$ C)                             |

| 104                                                                                                    |

| Figure 4.5 Depth versus concentration profile of AlGaN/GaN HEMT-on-                                    |

| CVD diamond105                                                                                         |

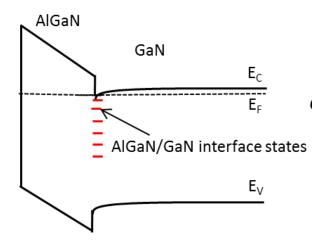

| Figure 4.6 Schematic energy band diagram illustrating traps at                                         |

| AlGaN/GaN interface trap106                                                                            |

|                                                                                                        |

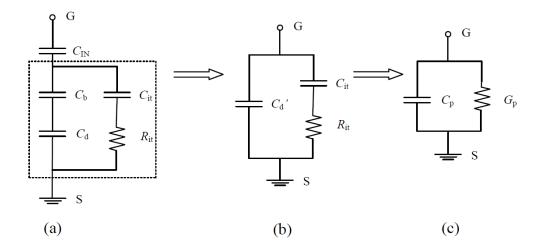

| Figure 4.7 Simplified equivalent circuit of a diode for interface trap density            |

|-------------------------------------------------------------------------------------------|

| calculation by AC conductance method (G-f), where $G_p$ is paralle                        |

| conductance which is measured at a wide range of frequencies by                           |

| conductance frequency technique108                                                        |

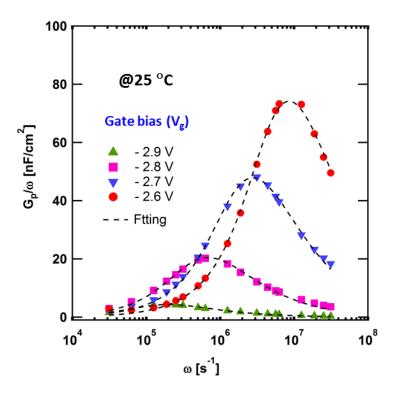

| Figure 4.8 Variation of conductance versus radial frequency for different                 |

| gate voltages at 25 °C, dotted black lines represent the fitting curve of                 |

| experimental G <sub>p</sub> /ω values109                                                  |

| Figure 4.9 Estimated interface trap density and trap state energy level,                  |

| relative to the conduction band, for different Vg (-2.9 V to -2.6 V, $\Delta V$ = -0.1    |

| V) measured at 25 °C111                                                                   |

| Figure 4.10 Variation of conductance versus radial frequency at a fixed                   |

| gate voltage for different temperatures (25- 200 °C). Dotted black lines                  |

| represent the fitting curve of experimental $G_p/\omega$ values112                        |

| Figure 4.11 Trap time constants extracted from fitted data at different                   |

| temperatures at fixed $V_{	exttt{g}}$ 113                                                 |

| Figure 4.12 Estimated interface trap density and trap state energy level,                 |

| relative to the conduction band, for different $V_g$ (-2.9 V to -2.6 V, $\Delta V$ = -0.1 |

| V) measured at various temperatures (25- 200 °C)114                                       |

| Figure 4.13 A comparative chart of interface traps density ( $D_T$ ), estimated           |

| using conductance method, in conventional AlGaN/GaN HEMT on various                       |

| substrates115                                                                             |

| Figure 4.14 Schematic cross-sectional diagram of AlGaN/GaN HEMT                           |

| illustrating the possible locations of traps: trap T1 at the surface, trap T2             |

| in the AlGaN barrier, trap T3 at the AlGaN/GaN interface, and trap T4 in                  |

| the GaN buffer116                                                                         |

| Figure 4.15 Temperature-dependent pulsed $I_{DS}-V_{DS}$ characteristics of               |

| HEMTs stressed at various quiescent bias conditions117                                    |

| Figure 4.16 Variation of $I_D$ collapse and $D_T$ at different temperatures (25-          |

| 200 °C)118                                                                                |

| Figure 4.17 Temperature-dependent pulsed IDS-VDS characteristics                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| $(V_g=+1V)$ of HEMTs stressed at higher quiescent bias conditions, (Inset)                                                                           |

| variation of I <sub>D</sub> at collapse at different temperatures (25- 200 °C)119                                                                    |

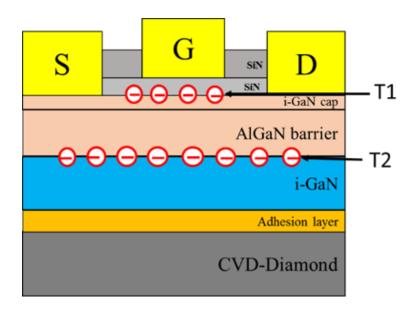

| Figure 5.1 Cross-sectional schematic diagram of AlGaN/GaN MIS-HEMT                                                                                   |

| with SiN dielectric on CVD diamond substrate. T1 and T2 represent the                                                                                |

| SiN/GaN interface trap and AlGaN/GaN hetero-interface traps,                                                                                         |

| respectively123                                                                                                                                      |

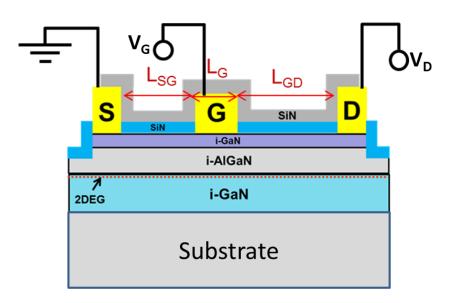

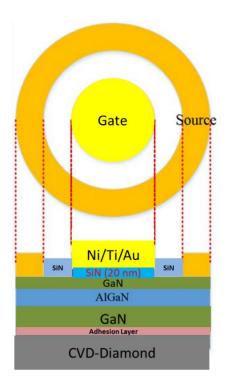

| Figure 5.2 Cross-sectional schematic diagram of AlGaN/GaN MIS-HEMT                                                                                   |

| with SiN dielectric on CVD diamond substrate125                                                                                                      |

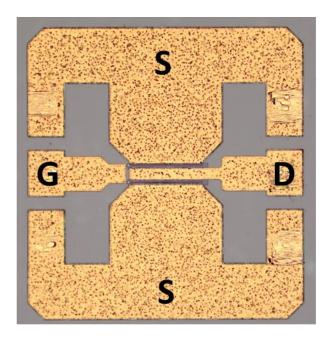

| Figure 5.3 Optical image of AlGaN/GaN (a)MIS Diode and (b) MIS-HEMT                                                                                  |

| on CVD diamond substrate125                                                                                                                          |

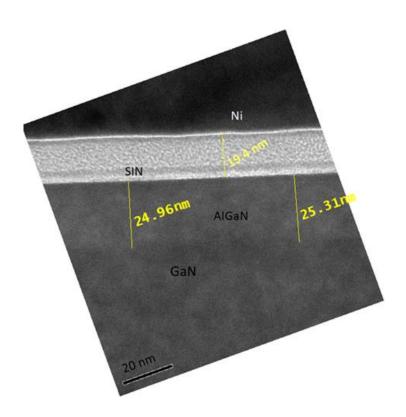

| Figure 5.4 Cross-sectional TEM image of fabricated AlGaN/GaN MIS-                                                                                    |

| HEMT on CVD diamond, focusing SiN dielectric on CVD diamond                                                                                          |

| substrate126                                                                                                                                         |

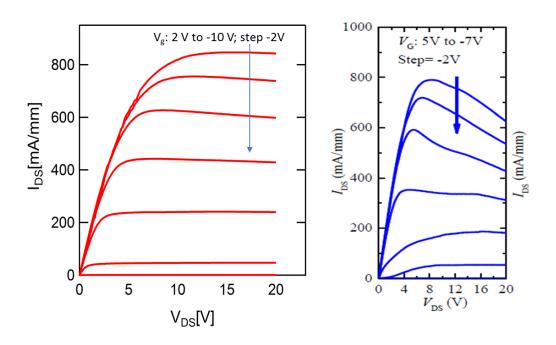

| Figure 5.5 $I_{DS}$ - $V_{DS}$ characteristics for (a) AlGaN/GaN MISHEMTs on CVD                                                                     |

| diamond (b) AlGaN/GaN MISHEMTs on Si substrate127                                                                                                    |

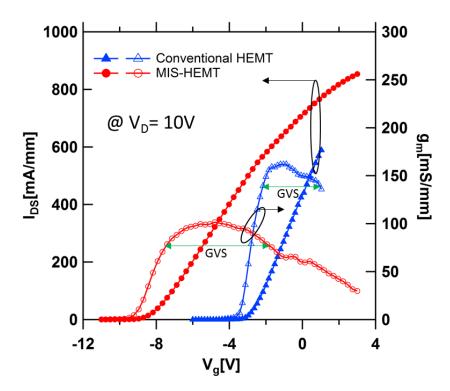

| Figure 5.6 Transfer characteristics of HEMTs and MISHEMTs on CVD                                                                                     |

| diamond substrate129                                                                                                                                 |

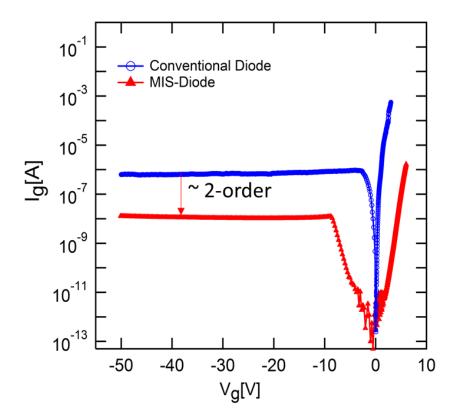

| Figure 5.7 Two terminal gate leakage current characteristics of                                                                                      |

| AlGaN/GaN MIS-diode and conv. diode on CVD diamond substrate .130                                                                                    |

| Figure 5.8 C-V characteristics of AlGaN/GaN MIS-diode and conventional                                                                               |

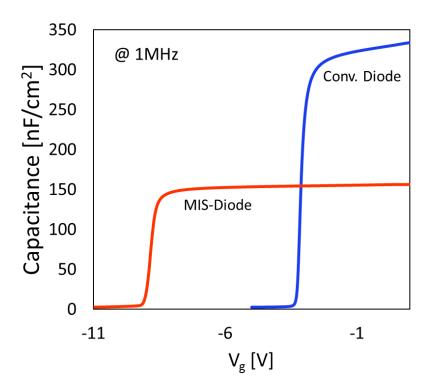

| diode at 1 MHz132                                                                                                                                    |

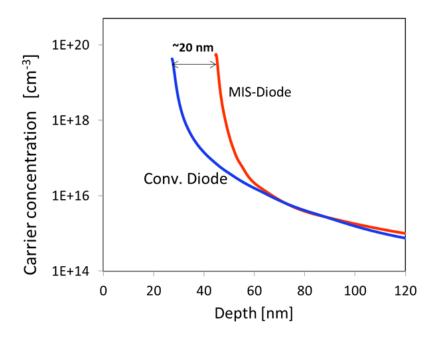

| Figure 5.9 Depth- carrier concentration profile of conventional (Conv.) and                                                                          |

|                                                                                                                                                      |

| MIS-diode estimated from C-V characteristics132                                                                                                      |

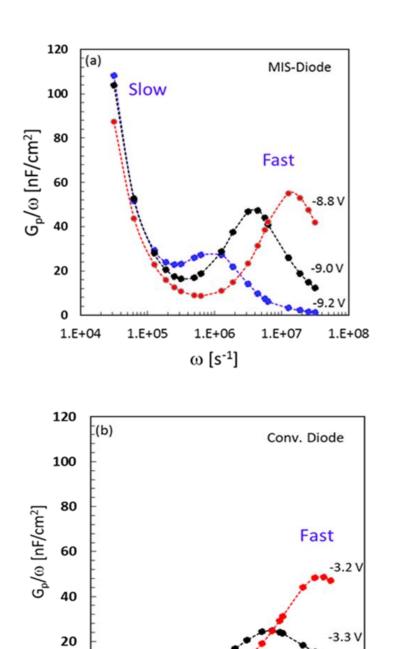

| MIS-diode estimated from C-V characteristics132 Figure 5.10 Frequency-dependent conductance as a function of radial                                  |

|                                                                                                                                                      |

| Figure 5.10 Frequency-dependent conductance as a function of radial                                                                                  |

| Figure 5.10 Frequency-dependent conductance as a function of radial frequency for AlGaN/GaN (a) MIS-Diode, and (b) conventional Diode on CVD diamond |

| Figure 5.10 Frequency-dependent conductance as a function of radial frequency for AlGaN/GaN (a) MIS-Diode, and (b) conventional Diode on CVD diamond |

| Figure 5.12 Trap state time constant as a function of th | e gate voltage of |

|----------------------------------------------------------|-------------------|

| MIS-Diode and Conv.Diode                                 | 132               |

### **List of Tables**

| Table 1.1 material properties of GaN and other semiconductor materia at 300K |     |

|------------------------------------------------------------------------------|-----|

| Table 1.2 Thermal/electrical/physical properties of bulk substrate mater     | ial |

| for GaN semiconductor at 300 K1                                              | 1   |

| Table 1.3. Database of physical origin of traps with the trap energy in Gal  | N-  |

| based devices1                                                               | 13  |

| Table 3.1 The temperature-dependent model of thermal conductivity use        | ed  |

| n simulation82                                                               | 2   |

### 1 Introduction

### 1.1 GaN HEMT technology: An overview

In the past few years, Gallium Nitride (GaN) based High-Electron-Mobility Transistors (HEMTs) have made tremendous progresses which makes them very attractive for high-frequency, high-power microwave and high-power switching device applications [1-4]. This is because GaN HEMTs are able to handle high current, high power, and capable to operate at high frequency due to the unique material properties of GaN such as large band gap, high electron velocity and critical breakdown field [5, 6]. A detailed explanation of the formation of two-dimensional electron gas (2DEG) of GaN HEMT and its structure has been provided in chapter 2.

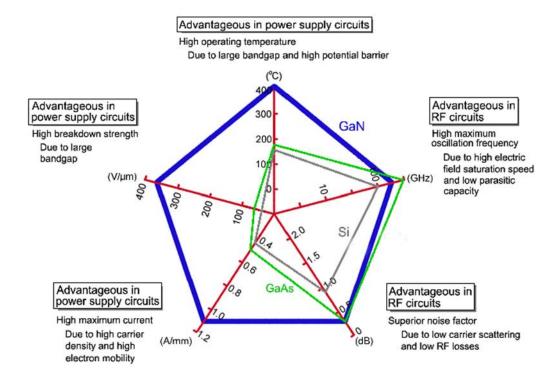

Table 1.1 and figure 1.1 compare various material properties of GaN and other semiconductors which are generally used in field-effect transistors. The superior electron mobility and high saturated drift electron velocity in 2DEG of GaN HEMT enable the device to operate at high current densities and high frequencies. The high critical field of GaN allows GaN-based devices to operate at higher voltages while high electron mobility makes it more suitable for high-frequency applications. The impact of material on the performance of semiconductor devices, figure-of-merit (FOM) are usually used. The FOM provides a rough

quantitative estimation of their relative strength with respect to specific device applications. To compare semiconductors for power device applications, the commonly used FOM are Johnson's FOM (JFOM) and Baliga FOM (BFOM). The JFOM characterizes the high-frequency performance of GaN devices and is proportional to the saturation velocity and critical electric field for impact ionization-initiated breakdown and is given by [7]:

$$JFOM = \left(\frac{E_c \ v_{sat}}{\pi}\right)^2$$

where  $v_{sat}$  is the saturation velocity, and  $E_c$  is the critical electric field. While the BFOM is used to define material parameters to minimize the conduction losses in the device at low-frequency operations. It is given by [7, 8]:

$$BFOM = \varepsilon \mu_n E_C^3$$

where  $\varepsilon$  is the relative dielectric constant,  $\mu_n$  is the electron mobility and  $E_{\mathcal{C}}$  is the critical electric field of semiconductor. Table 1 presents some figures of merit (FOM) used to quantify the device performance in high power and high frequency operation. All FOM values are normalized with respect to silicon. Due to its unique material properties, GaN-based HEMTs have exhibited much higher JFOM in comparison to GaAs and Si based transistors.

Table 1.1 Material properties of GaN and other semiconductor materials at 300K. All FOM values are normalized with respect to silicon [7].

| Properties                                                               | Si   | GaAs | 4H-SiC | GaN  |

|--------------------------------------------------------------------------|------|------|--------|------|

| Bandgap, E <sub>g</sub> (eV)                                             | 1.12 | 1.42 | 3.25   | 3.40 |

| Dielectric Constant, ε <sub>r</sub>                                      | 11.8 | 12.8 | 9.7    | 9.0  |

| Breakdown field, E <sub>Br</sub> (MV/cm)                                 | 0.25 | 0.4  | 3.0    | 3.3  |

| Electron mobility, μ (cm² /V s)                                          | 1350 | 8000 | 800    | 2000 |

| Maximum saturation velocity,<br>v <sub>sat</sub> (x10 <sup>7</sup> cm/s) | 1.0  | 2.0  | 2.0    | 3.0  |

| Thermal conductivity, k (W/m-K)                                          | 150  | 54   | 450    | 130  |

| JFOM                                                                     | 1    | 7.1  | 180    | 760  |

| BFOM                                                                     | 1    | 15.6 | 130    | 650  |

Figure 1.1 GaN material merits compared to Si and GaAs [9].

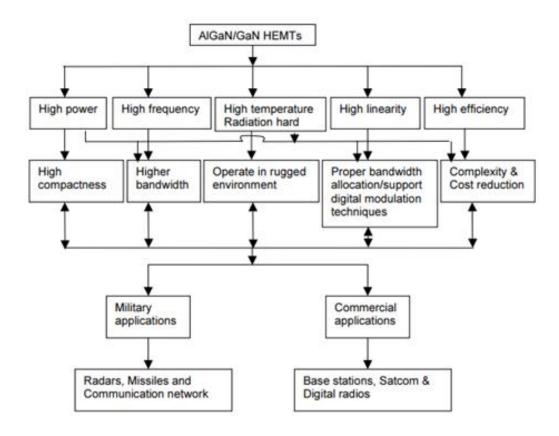

It is used in developing GaN HEMTs based devices and monolithic microwave integrated circuits (MMICs) for various electronic applications. Figure 1.4 shows the characteristics and area of application of GaN-based AlGaN/GaN HEMTs.

Figure 1.2 Characteristics and applications areas of GaN HEMTs [10].

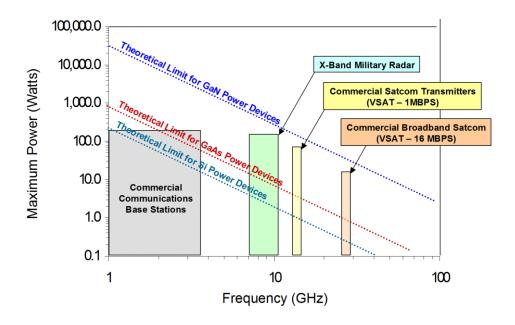

Figure 1.3 shows the RF application spectrum of Si, GaAs and GaN-based power devices along with RF power requirements and power frequency limits. From fig. 1.3 it is clear that GaN-based amplifiers are superior to GaAs and Si-based amplifiers in terms of both the output power and operating frequency limit. The theoretical limit of the GaN-based power amplifier is ~150-times and ~30-times higher than Si and

GaAs based amplifiers, respectively. In addition, GaN-based amplifiers also cover higher frequency spectrum for RF power applications in commercial, defence, and space industries. Other applications such as satellite, cellular base station, high power radar, and military systems also benefit from compact GaN-based high-power RF amplifiers.

Figure 1.3 Some RF application spectrum showing RF power requirements as well as power frequency limits of Si, GaAs and GaN-based power devices [11].

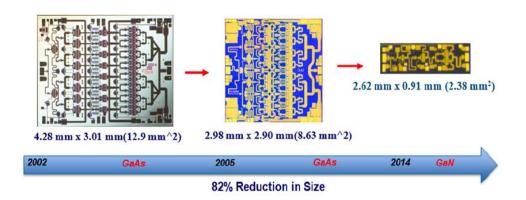

Due to the superior current density and operating voltage, GaN-based HEMTs have started to be an attractive alternative to GaAs based amplifiers, especially in the high-power transceiver system. The size of GaN-based power amplifiers has also reduced significantly due to the increased power density in comparison to GaAs-based circuits. Fig. 1.4

shows the comparative size of the power amplifier, based on GaAs and GaN HEMTs. Using GaN HEMTs, size reduction is ~ 82% as compared to GaAs based PA [12].

Figure 1.4 Advantage of GaN technology for power amplifiers (PAs) with efficient reduced size [12].

### 1.2 Issues in GaN HEMT for High Power Density Operation

### **1.2.1** Self-heating in GaN HEMTs

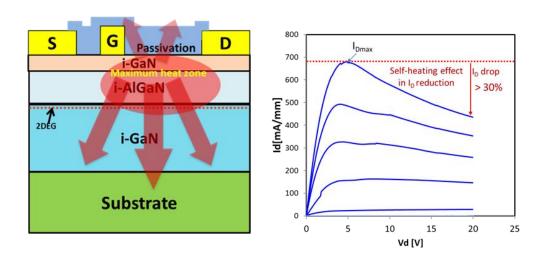

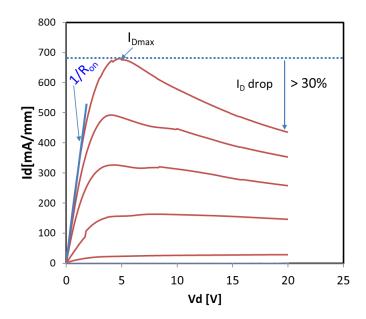

In GaN-based HEMTs, at high bias conditions generate a high electric field at the gate edge of the gate-drain region. This results in the generation of a large amount of heat due in the channel region which causes the channel temperature to rise and accelerating the phonon scattering (see figure 1.5 (a)). This will degrade the electron mobility in the channel and thereby a reduction of the drain current. The reduction of electron mobility in AlGaN/GaN HEMTs with temperature has been observed as  $\mu \sim (T/T_0)^{-1.8}$  [13]. The negative slope observed in the drain current characteristics is due to the self-heating effect (see fig. 1.5(b)).

Figure 1.5 shows the location of the maximum heat zone which is between the gate and drain due to the high electric field density that exists in this area. If the heat spreading from GaN HEMTs is insufficient, the device junction temperature increases, and the reduction of drain current density ( $I_{ds}$ ) will occur with increasing drain voltage ( $V_{ds}$ ). This self-heating becomes more severe when the device size is further reduced. Therefore, thermal management in GaN-based devices is a major concern, especially when the device is operating in a very high drain voltage (e.g.,  $V_{ds} \ge 48$  V). In such an operating condition, the device suffers substantial self-heating, which degrades the electrical (DC and RF) performance of the device and the circuit [14-17].

Figure. 1.5 (a) Schematic cross-section diagram of conventional, (b) Drain current reduction after  $I_{Dmax}$  due to self-heating effect in DC-IV output characteristics in GaN HEMTs-on-Si substrate AlGaN/GaN HEMTs showing the heat-spreading path from top and bottom.

These problems are predominant particularly when GaN HEMTs are employed on conventional substrates with low thermal conductivity (e.g., Si (Ksi=150 W/m-K), Sapphire (Ksa=46 W/m-K) and SiC (Ksic= 490 W/m-K)). Low thermal conductivity of substrates results in an increase of junction temperature ( $T_J$ ) [18, 19], and hence a decrease of 2-DEG mobility of GaN HEMTs which limits the efficient continuous wave (CW) operation at large Power densities ( $P_D$ ).

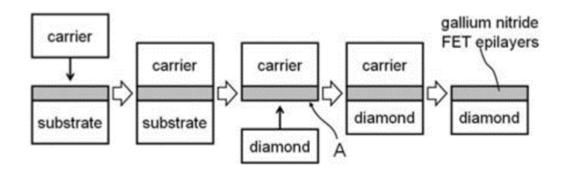

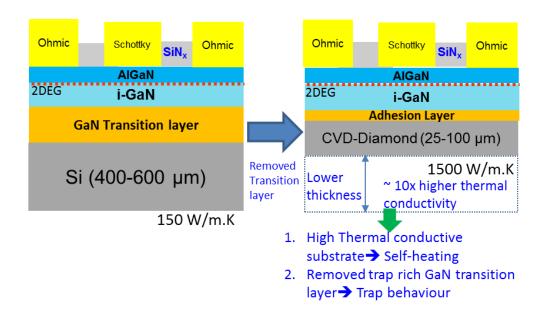

There are some conventional chip-level thermal management approaches to reduce the self-heating and junction temperature in the GaN-based device by using micro-channel liquid cooling or thermoelectric cooling. However, these methods have drawbacks like difficulty in implementation, MMIC incompatibility and in some cases need additional power and also the overall size of the module will be increased [20]. To overcome these problems, a high thermal conductive material diamond (See table 1.2) is employed near the device junction (maximum heat zone) (See Fig. 1.5). Two methods are used to extract the heat from the device, one from the top and another from the bottom of the device. However, heat extraction from the top has many challenges like high temperature (~800 C) diamond deposition, and diamond etching which can degrade the 2DEG properties of GaN HEMT. Another issue is the low effective thermal conductivity of thin diamond film which is unable to extract the significant amount of heat from the device channel. To extract the heat from the bottom of the device, thick diamond substrates, having much higher thermal conductivity (1000-2000 W/m-K), have been reported for GaN HEMTs [20, 21]. A comparative study of substrate material is listed in table 1.2. The high thermal conductivity of a thick diamond substrate helps in the faster dissipation of generated heat from the device which helps in maintaining a low junction temperature ( $T_i$ ). Low  $T_i$  reduces the 2DEG mobility degradation and improves the reliability and lifetime of the device. AlGaN/GaN HEMT-on-CVD diamond was developed using Metal-Organic Chemical vapor deposition (MOCVD) grown AlGaN/GaN HEMT-on-Si (Standard Wafer) by a proprietary process from the commercial company Element Six. The substrate transfer process was mainly done by the removal of Si substrate as well as GaN transition layer. Finally, the remaining AlGaN/GaN layers are attached to a polycrystalline diamond using a proprietary process of SiN adhesion layer in-between GaN and CVD diamond substrate [22, 23]. The schematic of the wafer transfer process is shown in figure 1.6.

Figure 1.6: Schematic of transfer process from GaN-on-Si to GaN-on-Diamond [23].

The usage of high thermal conductivity substrates is an emerging viable technique to extract the heat under high-power operations for GaN-based high-electron-mobility transistors. Several authors have reported AIGaN/GaN HEMTs on diamond substrates with remarkable DC and RF performances [24-28]. Researchers have reported AlGaN/GaN HEMTs on Diamond with DC dissipated power density ( $P_D = V_D \times I_D$ ) of 22 W/mm (CW) and 24 W/mm in pulse condition. Diduck et al has reported  $f_{\tau}$  of 85 GHz and f<sub>max</sub> of 95 GHz. Felbinger et al has reported RF power of 4.1 W/mm at 10 GHz using gate field-plate structure and observed and 29% higher unity-current-gain frequency than identical structures on Si substrate [27] P. C. Chao et al has further improved the device RF performance of GaN-on-Diamond HEMTs which was transferred from GaN-on-SiC HEMT wafer. They observed 3.6-times higher RF power capability (i.e., RF output power per active area of the device) in GaN-on-Diamond HEMTs as compared to GaN-on-SiC HEMTs [28]. These results show strong manifestation of superior thermal conductivity of Diamond as a substrate for GaN HEMT.

Table 1.2 Thermal/electrical/physical properties of bulk substrate material for GaN semiconductor at 300 K.

| Properties/Substrate                             | Sapphire         | Si                  | SiC                 | GaN             | Diamond                            |

|--------------------------------------------------|------------------|---------------------|---------------------|-----------------|------------------------------------|

| Thermal conductivity                             | 40±5             | 40±5 142.5±7.5      | 450±40              | 200±50          | 1500±500                           |

| at 300K, k [W/m-K]                               | 40±3             | 142.5±1.5           | 430140              | 200130          | 1300±300                           |

| Electrical resistivity at                        | 10 <sup>17</sup> | 2.3×10 <sup>5</sup> | 10 <sup>4</sup> to- | 10 <sup>6</sup> | 10 <sup>13</sup> -10 <sup>16</sup> |

| 300K, k [Ω.cm]                                   | 10               | 2.3×10°             | 10 <sup>6</sup>     | 10°             | 10.3-10.3                          |

| Lattice mismatch with                            | 14               | 17                  | 3.5                 | 0               | 89                                 |

| GaN [%]                                          | 14               | 17                  | 0.0                 |                 | 09                                 |

| Thermal Expansion                                | 7.5              | 2.6                 | 4.46                | 5.5             | 1.0                                |

| Coefficient [x10 <sup>-6</sup> K <sup>-1</sup> ] | 7.5              | 2.0                 | 4.40                | 5.5             | 1.0                                |

| Thermal expansion                                |                  |                     |                     |                 |                                    |

| coefficient mismatch                             | 36.4             | 52.7                | 18.9                | 0               | 81.8                               |

| GaN [%]                                          |                  |                     |                     |                 |                                    |

| Maximum available                                | 150              | 300                 | 150                 | 30              | 150                                |

| wafer diameter (mm)                              | 100              | 000                 | 100                 |                 | 100                                |

### 1.2.2 Trapping Effect in GaN HEMTs

Trapping effects in GaN HEMTs cause current collapse, drain current degradation, threshold voltage shift, transconductance-frequency dispersion, etc. [29]. The existence of traps also leads to drain current dispersion results in the reduction of output-power during device operation [30, 31]. In addition, electron trapping also leads to an increase of dynamic-on resistance (Dyn-R<sub>DS[ON]</sub>) under high-voltage operating conditions and degrades the switching performance of the device [32].

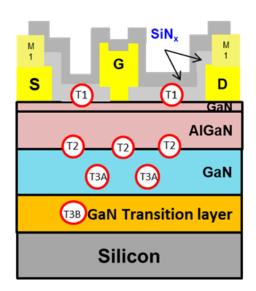

Various trapping mechanisms in GaN HEMT have been proposed to explain the device degradation due to electron trapping in different locations (e.g., surface traps, barrier traps, hetero-interface traps, and buffer traps) (See Fig. 1.6).

Figure 1.6 Schematic cross-sectional diagram of AlGaN/GaN HEMT on Si, illustrating the possible locations of traps: trap T1 at the surface, trap T2 at the GaN/AlGaN hetero-interface, and trap T3A in the GaN buffer and T3B in GaN transition layer.

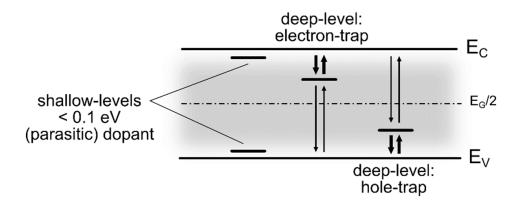

The traps can be classified based on their energy level. The traps with an energy-level close to the conduction or valence bands are called shallow-level traps, which are responsible for parasitic doping effects. Traps with an energy level deeper within the forbidden bandgap are called deep level traps. Figure 1.7 illustrate the trap energy level in the bandgap showing presence of shallow and deep-level trap.

Figure 1.7. Illustration of the shallow and deep trap energy level in the bandgap [33].

The deep-levels which are localized in the upper-half of the bandgap which has higher probability to capture and emit electrons from and to the conduction-band and behaves as electron-traps. The physical origin of traps with reference to the conduction-band energy ( $E_c$ ) in GaN HEMT are summarized in the table 1.3

Table 1.3. Database of physical origin of traps with the trap energy below conduction band in GaN-based devices (data taken from [32, 34]).

| Trap Energies (eV) | Physical Origin        | Ref            |

|--------------------|------------------------|----------------|

| 0.44,0.45 0.58     | C/O/H Impurities       | [32],[35]      |

| 0.58, 0.65         | VGa+Oxygen complex     | [32],[36],[37] |

| 0.73               | Nitrogen Interstitials | [32]           |

| 0.57, 0.72         | Fe dopant              | [38], [39]     |

| 0.27               | Nitrogen vacancies     | [40]           |

| 0.34               | Possible AlGaN surface | [41]           |

| 0.8                | Gallium vacancies      | [42]           |

| 0.62, 0.65       | GaN native defects  | [35], [43] |

|------------------|---------------------|------------|

| 0.51, 0.55, 0.69 | Nitrogen Anti-sites | [36], [44] |

Moreover, the density and the nature of these traps undermines the device reliability [45, 46]. The source of such traps is found to be either due to crystalline imperfections during the epitaxial growth, due to unintentional dope in barrier or buffer layer during epitaxy growth, or due to various device fabrications processes or wafer transfer process (in case of GaN-on-Si to GaN-on-CVD diamond). However, the exact origin and properties of these traps are still unclear in the transferred GaN HEMTs-on-CVD and need to be investigated as not many reports on the trapping behaviour are available.

## 1.3 Motivation and Objective

As we mentioned earlier, typically the GaN HEMTs-on-CVD diamond is transferred from GaN HEMTs-on-Si. In this process, two key structural changes occur in GaN HEMTs: one is replacing the high thermal conductive substrate and the other is the removal of trap rich GaN transition layer (See Fig. 1.8). These changes could affect the self-heating and trap behaviour in the GaN HEMTs-on-CVD diamond. Although the improvement in the electrical performance of GaN-on-Diamond AlGaN/GaN HEMTs has been previously reported [22-28,47-49], the detailed investigations of the self-heating effect and quantitative

estimation of electrical (mainly RF) performance have not been reported. In addition, due to the removal of the defect rich transition layer, there could be a change in the trap behaviour of the HEMT. This change in trap behaviour affects the device performance and reliability of the device. Unfortunately, so far, no detailed studies have been reported on the interface trap characteristics in GaN HEMTs-on-CVD diamond.

Figure 1.8 Schematic cross-section diagram of conventional GaN HEMTs-on-Si and GaN HEMTs-on-CVD diamond showing the major changes during the wafer transfer process.

## 1.4 Major contribution of the thesis

This thesis focuses on two key issues in the HEMTs fabricated on transferred GaN-on-Diamond from GaN-on-Si. First, the effect of substrate (CVD diamond) in the self-heating and second, the trapping

behaviour in GaN-on-Diamond.

In this thesis, a detailed investigation of the self-heating effect in DC ( $I_{dmax}$ ,  $g_m$ ) and RF ( $f_T$ ,  $f_{max}$ , Gain) performance is carried out for a wide range of drain bias voltage. The degradation in 2DEG transport properties was also analyzed in the wide range of bias voltage. In addition, TCAD numerical simulation was carried out to investigate device junction temperature under the large electric field and high-power density dissipation. The effective carrier velocity and effective mobility were also investigated to analyze the variations in device performance due to self-heating effect. The 22-element small-signal equivalent circuit parameters were extracted and analyzed the variation in RF performances due to self-heating of GaN-on-Diamond HEMTs. Such work is helpful for developing the electrical and thermal model of device as well as improving the operating limit of GaN HEMTs for next-generation high power DC and RF applications.

In addition to the self-heating effect, interface traps behavior in GaN HEMTs-on-CVD diamond was also investigated. The conductance-frequency technique was used to estimate hetero-interface trap density, trap state energy, and trap time constants. Results were compared and benchmarked with reported GaN HEMTs on various substrates like Sapphire, Si, and SiC. Further to improve the device performance, GaN-MISHEMTs-on-CVD diamond was fabricated and analyzed the gm linearity, gate leakage, and interface trap behavior.

#### 1.5 Thesis Outline

This thesis is written in six chapters. Chapter one stated the motivations and objectives of this work.

Chapter 2 provides an explanation of AlGaN/GaN HEMT principle and the device structure. This chapter also discusses the various characterization techniques used to evaluate the self-heating and trapping effects in AlGaN/GaN HEMTs. The basics of S-parameter measurements and small-signal equivalent circuit model is discussed which is crucial to investigate the variation in the device performance at high power density operation causes increased channel temperature in the device.

In chapter 3, the fabrication process of GaN HEMTs-on-CVD-diamond and Si substrates will be presented. The detailed quantitative investigation of the self-heating effect on DC and RF performances will be analyzed. The effect of bias conditions mainly on RF behaviour on HEMTs will also be analyzed. Using 22- element small-signal equivalent circuit parameters, RF performance of GaN HEMTs over a wide range of drain bias will be explained.

In chapter 4, the investigation of hetero-interface trapping characteristics in AlGaN/GaN HEMT on CVD-diamond using the conductance method will be presented. The conductance-frequency technique is used to estimate hetero-interface trap density and trap state

energy. The additional deeper traps in the bandgap are investigated by measurements performed at elevated temperatures (25 °C to 200 °C). The obtained results are benchmarked with the reported trap densities in GaN HEMTs on various substrates like Sapphire, Si, and SiC.

In chapter 5, the AlGaN/GaN metal-insulator-semiconductor (MIS) HEMTs on CVD-diamond is described to improve device characteristics further. The critical issue in MIS-HEMT is dielectric interface trap behaviour. The detailed investigation of dielectric interface and hetero-interface is carried out in AlGaN/GaN MISHEMTs on CVD-diamond and compared with the conventional Schottky AlGaN/GaN HEMTs on CVD-diamond.

In chapter 6, the summary of current work will be presented. Future research work and recommendations will also be given in chapter 6.

# 2 AIGaN/GaN HEMTs, Self-heating and

# trapping mechanism

In this chapter, the fundamentals of conventional AlGaN/GaN HEMT technology, the formation of the 2DEG channel, and current density in the device are briefly described. The self-heating issues in GaN HEMTs at high current, high dissipation power density operation and its effect in the channel temperature and device performance are also discussed. The electrical characterization techniques, which help to quantify and analyze self-heating induced device performance degradation, are also presented. To further understand the root cause of device performance degradation, a small signal equivalent circuit parameter is explained. At high power density, trapping phenomena in the device become critical for reliable operation. To understand the trapping mechanism and to evaluate the trapping behaviour, various characterization techniques are explained in this chapter. These methods are used to evaluate the self-heating and trapping effects in the device (GaN HEMTs-on-CVD diamond) described in this thesis.

#### 2.1 Introduction

GaN-based High-Electron-Mobility **Transistors** (HEMTs) have desirable intrinsic capacity for handling large current and power densities due to the unique material properties of GaN such as large band gap, high electron saturation velocity and high critical breakdown strength [5, 6]. However, the full potential of GaN HEMT has still not been fully realised due to the inherently low thermal conductivities of the conventional substrates used for GaN epitaxial growth e.g., Sapphire (K<sub>Sapp</sub>=35 W/m-K), Si ( $K_{Si}=150$  W/m-K) and SiC ( $K_{SiC}=490$  W/m-K). Low thermal conductive substrate hinders the fast dissipation of lattice heat (self-heat) which is generated in the device during high-power operation of GaN HEMTs. The high retention of heat results in the increase of channel temperature, which leads to the degradation of direct current (DC) and radio frequency (RF) performance [50, 51]. The root cause of variation in device performances can be identified by investigation the self-heating effect on the equivalent circuit parameters of the GaN HEMTs. Therefore, a more precise equivalent circuit (22-elements) parameter extraction methodology is used in this study. Polycrystalline diamond is now emerging as the best thermal conducting substrate (1000-2000 W m<sup>-1</sup>.K<sup>-</sup> 1) to extract the heat from high-power handling GaN devices [30]. Typically, for GaN-on-CVD Diamond process development, the host Si or SiC substrate and GaN transition layer (growth-defect-rich stress mitigation layer) is removed. Subsequently, the remaining HEMT layers

are then bonded onto CVD-diamond which then acts as the new substrate [24]. Thus, the overall quality of the epitaxial GaN layer will be affected in this substrate transfer process. This may lead to variation in the heterointerface trap and buffer trap behaviour of GaN HEMT-on-Diamond. Detailed characterization methodologies for the investigation of self-heating effect and trapping behaviour are described later in this chapter.

#### 2.2 AIGaN/GaN HEMT Principle

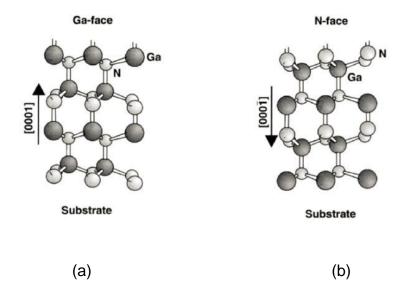

GaN crystalline structure is typically wurtzite and is more thermodynamically stable as compared to the Zinc blend and Rock Salt structure. The wurtzite structure of Gallium (Ga) and Nitrogen (N) atom face are shown in Fig. 2.1 (a) and (b), respectively. The distribution of valence electrons in the GaN bonding is strongly asymmetric due to the electron affinity difference between Ga and N atoms [45].

Figure 2.1 Crystal structure and polarization field in (a) Ga-face and (b) N-face GaN [52].

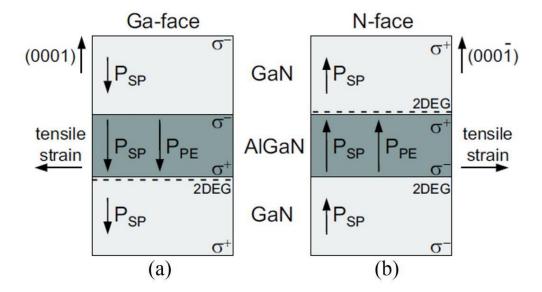

In the case of GaN crystal unit cell, Ga and N atoms are bounded partially covalent and partially ionically. The electronegativity difference of  $\sim 1.4$  eV in GaN results in the ionicity of bonding  $\sim 40\%$  [53]. The difference in ionicity leads to polarization in GaN. This kind of polarization without any external influence, such as an applied electric field or strain in the crystal lattice is called spontaneous polarization ( $P_{SP}$ ). Another type of polarization is known as piezoelectric polarization ( $P_{PE}$ ) which occurs due to deformation in the crystal lattice under external field or internal forces or stress. In the case of AlGaN/GaN heterostructure structure, the piezoelectric polarization occurs in the thin AlGaN layer, as it is below the critical thickness. Therefore, in AlGaN/GaN HEMT, both types of polarization occur to form 2DEG. Both the PE and SP occur in the same direction (See Fig. 2.2), and the total polarization in AlGaN/GaN interface can be written as  $[P = P_{PE} + P_{SP}]$  [54].

The total induced sheet charge ( $\sigma$ ) is created at the interface between the AlGaN layer and the GaN layer of AlGaN/GaN heterostructures and can be expressed as [53];

$$|\sigma| = |P_{SP-AlGaN} + P_{PE-AlGaN} + P_{SP-GaN}|$$

Figure 2.2 Spontaneous- and piezoelectric-polarization and the polarization induced sheet charge in AlGaN/GaN heterostructures with (a) Ga-face and (b) N-face [54].

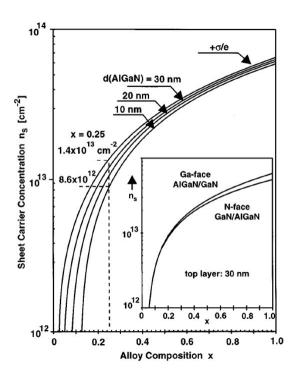

The spontaneous polarization increases with increasing the AI mole fraction (x) in  $AI_xGa_{1-x}N$  which results in the increase of total charge density. The sheet carrier concentration of a 2DEG and its dependence on alloy composition can be predicted for strained AIGaN/GaN based heterostructures. The total sheet carrier concentration  $n_s$  can be calculated using total sheet charge density and can be expressed as:

$$n_s(x) = \frac{\sigma(x)}{q} - \frac{\varepsilon_0 \, \varepsilon_r(x)}{q^2 d} \big[ q \phi_b(x) + E_F(x) - \Delta E_c(x) \big]$$

where  $\sigma$  is the total sheet charge density, q is the electron charge,  $\varepsilon_0$  is vacuum permittivity and  $\varepsilon_r$  is the relative permittivity, d is the thickness of the AlGaN barrier,  $q\phi_0$  is the Schottky barrier of the gate contact on top of

AlGaN (or GaN cap layer),  $E_F$  is the position of the Fermi level with respect to the edge of the GaN conduction band energy, and  $\Delta E_c(x)$  is the offset of conduction band energy at the AlGaN/GaN interface.

Polarization induced 2DEG sheet carrier density in AlGaN/GaN heterostructure for different thickness of AlGaN barrier is shown in fig.2.3.

Fig.2.3 The sheet carrier concentration of 2DEG in Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN HEMT for different thickness of AlGaN barrier [54]

In the AlGaN/GaN HEMT epitaxy layer, the top layer is generally an undoped thin (2-3 nm) GaN layer. The undoped GaN cap layer has the advantage of large Schottky barrier height (> 1 eV) and gate metal is directly formed on this layer in this work. Below the GaN cap layer, there is an undoped thin (8-25 nm) AlGaN barrier layer [55, 56], which primarily

induces electrons into 2DEG and hinders hot-electron spilling over into the barrier. Below the AlGaN barrier layer, there is an undoped thick (~ 1 µm) GaN channel layer that has a lower bandgap than AlGaN barrier layer. Due to the large polarization difference between AlGaN barrier and GaN channel layer, a thin layer of 2DEG is formed in the GaN HEMT. GaN layer below the GaN channel is called the buffer layer which helps to reduce the parallel leakage current and parasitic capacitance between the source and drain electrodes. The GaN buffer layer could be un-doped, C doped or Fe doped based on the optimization of buffer quality for highfrequency high power application. Below the GaN buffer layer, GaN transition layer is one of the important epitaxy layers. GaN transition layer helps to accommodate the strain and TEC mismatch between the substrate and GaN buffer layer. The lattice mismatch between GaN and substrate is 3.6%, 13.8%, 17% for SiC, Sapphire and Si substrate, respectively [57]. Finally, the bottom part is the substrate. Generally, Si, Sapphire, or SiC substrate is used for GaN growth for GaN-based HEMT development. The substrate plays an important role in heat dissipation from the device during the operation [52-54]. Therefore, a substrate with high thermal conductivity is preferred. Good thermal conductivity of substrate is essential for high power AlGaN/GaN transistors to minimize the mobility-related performance degradation with fast dissipation of selfheat generated in GaN HEMTs at high power density.

Epitaxial growth of AlGaN barrier layer over GaN layer develops

large total polarization and develops a positive sheet charge density in the bottom of AlGaN layer which induces accumulation of free mobile electrons in the top of GaN layer in order to compensate positive charges. The induced mobile electrons are confined in the triangular quantum well at the interface of AlGaN/ GaN and form a two-dimensional electron gas (2DEG) conducting channel. Typically, the 2DEG carrier density is of ~ 1×10<sup>13</sup> cm<sup>-2</sup> in Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterostructure for x = 0.2-0.5 [50-57]. The 2DEG channel is well separated from the top charge supply layer, the parasitic effects such as Coulomb scattering can be mitigated, thus resulting in a significant enhancement of electron mobility in the channel. The 2DEG quantum well is located in the un-intentionally doped GaN material. Impurity scattering can also be strongly reduced, resulting in an enhancement in the mobility of 2DEG electrons. The enhanced electron mobility in the 2DEG channel is the most important feature of the high electron mobility transistors (HEMTs).

In the thermodynamic equilibrium condition, the AlGaN/GaN heterostructure has a constant fermi level ( $E_F$ ). The  $\Delta E_C$  is a conduction band offset between AlGaN and GaN. Figure 2.4 shows the epi structure of AlGaN/GaN HEMTs and the energy band diagram with 2DEG formation. These 2DEG charge densities become the source for current flow in the channel of HEMT device.

Figure 2.4 The schematic cross-section and respective energy band diagram of a typical AlGaN/GaN HEMT.

The 3D structure of GaN HEMT is shown in Fig. 2.4 whereby the 2DEG electron can move freely in two dimensions but is tightly confined in the third dimension. The 2DEG electron in AlGaN/GaN HEMT confined to a quantum well leads to quantized energy level and exhibits higher effective mobilities than those in MOSFET. The function of gate is to control the 2DEG density and hence the source-drain current in the channel of the device. In the conventional AlGaN/GaN HEMT, due to large inherent polarization, the high-density 2DEG presents even at no external gate bias ( $V_g$ = 0 V) is also known as D-mode (depletion mode). In this thesis, the D-mode AlGaN/GaN HEMT is used for device fabrication and analysis of device performance. The depletion of 2DEG depends on the gate bias condition. If the gate bias is positive ( $V_g$  = 0 V), more electrons are accumulated in the 2DEG quantum well, resulting in enhanced 2DEG density and increased source-drain current density. When the gate bias is

negative ( $V_g$ <0V), electrons are depleted from the quantum well, resulting in reduced 2DEG density and decreased source-drain current density (See Fig. 2.5). The 2DEG is completely depleted at a certain gate voltage called pinch-off voltage.

Figure 2.5 The energy band diagram of AlGaN/GaN HEMTs at (a) unbiased gate (b) positive gate bias, and (c) negative gate bias [58].

The GaN HEMT is generally grown using molecular beam epitaxy (MBE) or Metal-organic chemical vapor deposition (MOCVD) technique. After the growth of AlGaN/GaN HEMT, the 2DEG properties of HEMT are evaluated in terms of parameters such as, 2DEG carrier concentration  $(n_s)$ , electron mobility ( $\mu$ ), and sheet resistance ( $R_{sh}$ ).

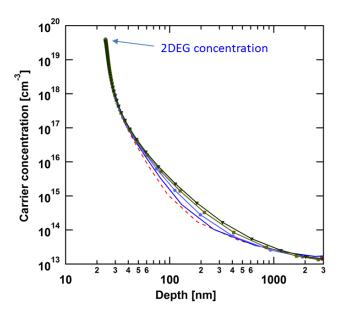

Figure 2.6 Typical depth versus carrier density profile of AlGaN/GaN HEMT [59].

Figure 2.6 shows the typical depth versus carrier density profile of AlGaN/GaN HEMT-on-Si substrate. The high carrier density (~ 10<sup>19</sup> cm<sup>-3</sup>) is at the interface between the AlGaN barrier and GaN channel region. Generally, background carrier density of ~ 10<sup>15</sup> cm<sup>-3</sup> exist in GaN layer. However, increased carrier density near the GaN/substrate interface was observed which could be due to interdiffusion at the GaN/substrate interface. This can be minimized by improving the epitaxy growth method by eliminating the degenerate layer at GaN/substrate interface [60].

Figure 2.7 Temperature dependence sheet carrier density  $(n_s)$  and mobility  $(\mu)$  and  $R_{sh}$  of AlGaN/GaN HEMT [59].

Typically,  $n_s$  in AlGaN/GaN HEMT is affected very little by temperature in the typical operating range of ~300 to 450 K (See Fig. 2.6) [59]. On the contrary, the 2DEG carrier mobility degrades with increasing temperature due to the optical phonon scattering [61,62]. The 2DEG mobility generally follows power-law relation with the temperature at T > ~ 200 K.

$$\mu(T) = \mu_0 \left(\frac{T}{T_0}\right)^{\gamma}$$

$\mu(T)$  is the mobility at required temperature T,  $\mu_0$  is the mobility at room temperature 300 K, and  $\gamma$  is the mobility exponent power index. The  $\gamma$  values are reported in between -1.5 to -2.7 for AlGaN/GaN HEMT. The 2DEG sheet resistance ( $R_{sh}$ ) of GaN HEMT can be calculated as per the following expression

$$R_{sh} = \frac{1}{qn_s\mu}$$

The R<sub>sh</sub> is inversely proportional to the  $n_s$  and  $\mu$ . The degradation in  $R_{sh}$  is mainly by temperature dependence  $\mu$  in the 2DEG.