## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

## Design of transmitter front-end for WLAN 802.11ax application

Liu, Bei

2020

Liu, B. (2020). Design of transmitter front-end for WLAN 802.11ax application. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/142579

https://doi.org/10.32657/10356/142579

This work is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License (CC BY-NC 4.0).

Downloaded on 09 Apr 2024 12:49:53 SGT

# Design of Transmitter Front-End for WLAN 802.11ax Application

#### **LIU BEI**

School of Electrical & Electronic Engineering

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirement for the degree of Doctor of Philosophy

#### **Statement of Originality**

I hereby certify that the work embodied in this thesis is the result of original research, is free of plagiarised materials, and has not been submitted for a higher degree to any other University or Institution.

| 21-01-2020 | Liu bei |  |

|------------|---------|--|

|            |         |  |

| Date       | Liu Bei |  |

#### **Supervisor Declaration Statement**

I have reviewed the content and presentation style of this thesis and declare it is free of plagiarism and of sufficient grammatical clarity to be examined. To the best of my knowledge, the research and writing are those of the candidate except as acknowledged in the Author Attribution Statement. I confirm that the investigations were conducted in accord with the ethics policies and integrity standards of Nanyang Technological University and that the research data are presented honestly and without prejudice.

| 21-01-2020 | X-1/1\TY        |

|------------|-----------------|

|            |                 |

| Date       | Boon Chirn Chve |

7+E11

#### **Authorship Attribution Statement**

This thesis does not contain any materials from papers published in peer-reviewed journals or from papers accepted at conferences in which I am listed as an author.

| 21-01-2020 | Liu Bei |  |

|------------|---------|--|

|            |         |  |

| Date       | Liu Bei |  |

#### Acknowledgements

In my four years of PhD's study, many people have provided me with warm and great help, and I have gained much valuable experience. Here I would like to thank those who have contributed to my research work and the completion of my thesis.

First and foremost, I would like to express my sincere thanks and appreciation to my supervisor Associate Professor Boon Chirn Chye for giving me the opportunity to work under his guidance. His profound academic knowledge and patient guidance deeply influenced me and benefited me a lot in academic research. Moreover, Prof. Boon provided us with a relaxed and harmonious learning and research environment. More importantly, he encouraged me to overcome the challenging and difficulties encountered in my PhD study.

I would like to thank senior research staffs, Dr. Yi Xiang, Dr. Pilsoon Choi and Mao mengda. They shared me with their experiences and skills in RFIC design, and gave me a lot of valuable advices and comments on my research work. Here, I want to express my gratitude especially to Dr. Yi Xiang for his great help in paper writing and revision. I would also like to thank Liang Zhipeng for his generous help in digital circuit design, and would like to thank other colleagues, Yang Kaituo, Feng Guanyin, Devrishi Khanna and Li Chenyang for discussion, co-operation and help.

Lastly and most importantly, my gratitude is extended to my wife, Sun Yue and my parents in China for their encouragement and selfless support, which is a solid foundation of my PhD study.

#### **Summary**

As the successor to current IEEE 802.11ac, the emerging IEEE 802.11ax will increase the efficiency of wireless local area network (WLAN) networks, especially in the highdensity WLAN deployment scenario, and the data rate is expected to reach 10 Gbps. Carrier aggregation (CA) will be a key feature of 802.11ax system to boost data rate. Voltage-controlled oscillator (VCO) pulling and crosstalk between RF channels are two main problems related to carrier aggregation due to the inevitable coupling and leakage between different signal transmitting channels in one complementary metal-oxide silicon (CMOS) chip, which introduce severe impacts on adjacent channel leakage ratio (ACLR) and error vector magnitude (EVM). To address these two problems, high isolation between signal transmitting channels is required, but may not be realizable in some practical cases due to the constraint of layout. Firstly, this thesis proposes a new transmitter architecture using parallel direct-conversion and double-conversion configuration, which can address the problems of crosstalk and VCO pulling simultaneously without large physical isolation. Based on the proposed transmitter architecture, a transmitter front-end supporting two-carriers aggregation for 5-GHz WLAN 802.11ax application is designed and implemented in TSMC 40-nm CMOS technology. For contiguous intra-band carrier aggregation with two VHT80, MCS9 signals (80-MHz bandwidth, 256-quadrature amplitude modulation (QAM) and 11.25dB peak-to-average power ratio (PAPR)), the transmitter front-end delivers an average output power of 5.3+4.8 dBm for two carriers with the EVM  $\leq$  -32 dB, and the EVM can reach -36.1 dB.

802.11ax's systems are designed to operate in the existing 2.4-GHz and 5-GHz (4.9-5.9 GHz) spectrums, requiring a 2.4/5-GHz dual-band transmitter front-end. A single

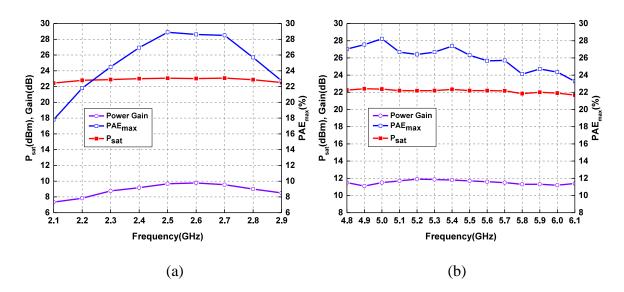

transmitter supporting reconfigurable 2.4/5-GHz dual-band operation is superior to the dual-band architecture using two transmitters channels in terms of lower cost. Currently, no reconfigurable dual-band transmitter using only one transmitting channel is available in academia and industry. Therefore, another effort of this thesis is to design such a reconfigurable 2.4/5-GHz dual-band transmitter front-end for 802.11ax application. As a core block in a transmitter, the power amplifier (PA) should also operate in the 2.4and 5-GHz bands. This thesis presents a new design methodology of the reconfigurable dual-band output matching network to extract high passive efficiency. A 2.4/5-GHz dualband PA is designed to validate the proposed matching methodology. In the 2.4-GHz and 5-GHz WLAN bands, the PA achieves a saturated output power (Psat) of 23 dBm and 21.9-22.4 dBm with power-added efficiency (PAE) of 27% and 24.2-28.2%, respectively. Then, a transmitter front-end supporting the 2.4/5-GHz dual-band operation for WLAN 802.11ax application is designed. The measurement results verify that the transmitter front-end can support the 802.11ax signal with 1024-QAM modulation both in the 2.4and 5-GHz bands. Since only one RF channel is used, the proposed transmitter front-end has the advantages of simpler design, smaller chip size and lower cost, in comparison with other state-of-the-art dual-band WLAN transmitters.

### **Table of Contents**

| Acknowled    | lgements                                          | .i |

|--------------|---------------------------------------------------|----|

| Summary      |                                                   | ii |

| List of Figu | uresvi                                            | ii |

| List of Tab  | lesx                                              | V  |

| List of Acr  | onymsxv                                           | ۷i |

| Chapter 1    | Introduction                                      | 1  |

| 1.1 Me       | otivation                                         | 1  |

| 1.2 Ma       | ajor Contribution                                 | 4  |

| 1.3 Th       | nesis Organization                                | 5  |

| Chapter 2    | Review of transmitter                             | 7  |

| 2.1 Co       | onventional transmitter architecture              | 7  |

| 2.1.1        | Direct up-conversion transmitter                  | 7  |

| 2.1.2        | Heterodyne transmitter                            | 8  |

| 2.1.3        | Real-IF transmitter                               | 9  |

| 2.1.4        | PLL modulation transmitter                        | 0  |

| 2.2 Tr       | ansmitter architecture for carrier aggregation1   | 0  |

| 2.2.1        | Architecture with parallel fully separated chains | 0  |

| 2.2.2        | Architecture with carriers combined after PAs1    | 1  |

| 2.2.3        | Architecture with carriers combined before PA1    | 2  |

| 2.2.4        | Architecture with carriers combined in baseband   | 3  |

| 2.2    | 2.5  | Summary of different architectures              | 14  |

|--------|------|-------------------------------------------------|-----|

| 2.3    | Du   | al-band WLAN Transmitter                        | 15  |

| Chapte | er 3 | Crosstalk and VCO pulling                       | 19  |

| 3.1    | Cro  | osstalk                                         | 20  |

| 3.2    | VC   | CO pulling                                      | .25 |

| 3.3    | Co   | upling factor between two channels in layout    | .31 |

| 3.3    | 3.1  | Coupling factor between two active devices      | .31 |

| 3.3    | 3.2  | Coupling factor between two metal signal traces | .36 |

| 3.4    | Sur  | mmary                                           | .43 |

| Chapte | r 4  | Design of a Transmitter for Carrier Aggregation | .45 |

| 4.1    | Pro  | posed transmitter architecture                  | .46 |

| 4.2    | Me   | echanism of VCO pulling mitigation              | .47 |

| 4.3    | Me   | echanism of crosstalk mitigation                | .48 |

| 4.4    | Tra  | nnsmitter front-end design                      | 52  |

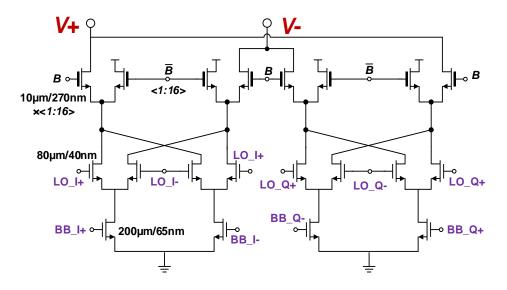

| 4.4    | .1   | Mixer design                                    | .53 |

| 4.4    | 1.2  | LO input balun design                           | 58  |

| 4.4    | 1.3  | Divider design                                  | .60 |

| 4.4    | 1.4  | Driver and Power Amplifier Design               | 65  |

| 4.5    | Tra  | ansmitter measurement results                   | .71 |

| 4.5    | 5.1  | Single Carrier Performance                      | 73  |

| 4.5    | 5.2  | Carrier Aggregation Performance                 | 75  |

| 4.6      | Sui   | mmary                                                        | 81        |

|----------|-------|--------------------------------------------------------------|-----------|

| Chapter  | r 5   | Reconfigurable 2.4/5-GHz Dual-band Transmitter Front-End     | 82        |

| 5.1      | Bac   | ckground of dual-band or broadband PAs                       | 83        |

| 5.2      | 2.4   | /5-GHz Dual-band PA                                          | 84        |

| 5.2      | 2.1   | Optimum Load Impedance Analysis                              | 84        |

| 5.2      | 2.2   | Dual-band Output Matching Network Design                     | 86        |

| 5.2      | 2.3   | Implementation of output matching network                    | 92        |

| 5.2      | 2.4   | Implementation and measurement of dual-band PA               | 95        |

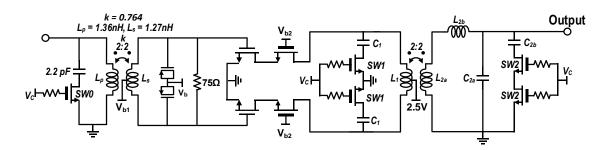

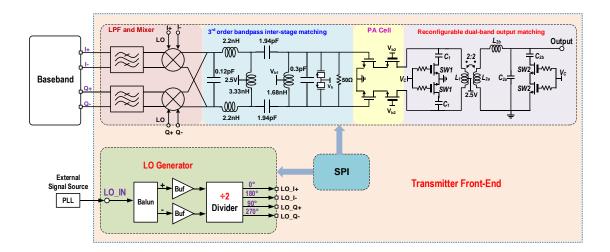

| 5.3      | 2.4   | /5-GHz Dual-band Transmitter Front-End                       | 104       |

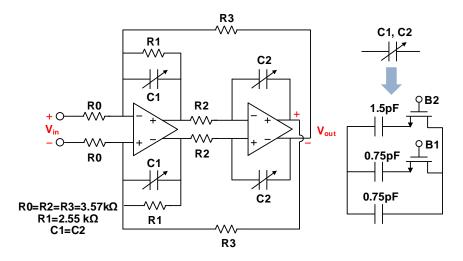

| 5.3      | .1    | LPF and Mixer                                                | 104       |

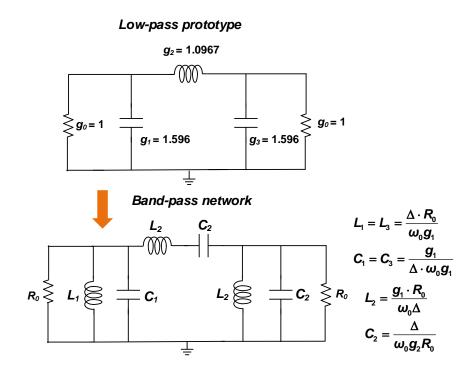

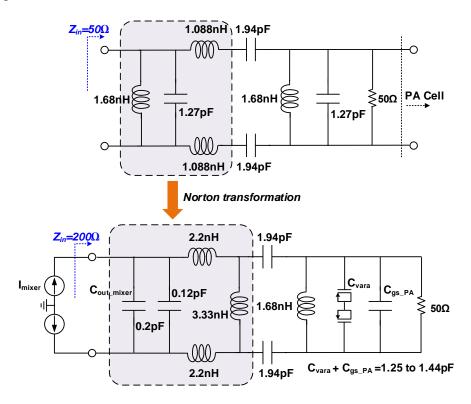

| 5.3      | 3.2   | Inter-stage matching between mixer and PA stage              | 106       |

| 5.3      | 3.3   | LO generator                                                 | 108       |

| 5.3      | 3.4   | Implementation and measurement of dual-band transmitter fr   | ront-end  |

|          |       |                                                              | 108       |

| 5.4      | Sui   | mmary                                                        | 113       |

| Chapter  | r 6   | Conclusion and Future Works                                  | 114       |

| 6.1      | Co    | nclusions                                                    | 114       |

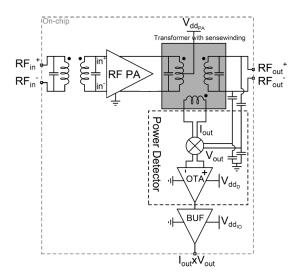

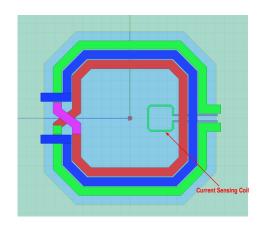

| 6.2      | Tru   | ie power detector                                            | 115       |

| 6.3      | Tra   | insmitter with true power detector for carrier aggregation   | 116       |

| 6.4      | Tra   | ansmitter supporting 2.4/5-GHz dual-band operation and 5-GHz | z carrier |

| aggregat | tion. |                                                              | 118       |

| Author   | 's Pu | ıblications                                                  | 121       |

| Bibliography | 7   |

|--------------|-----|

|              | 120 |

## **List of Figures**

|     | Figure 1.1. Carrier aggregation scenarios.                                        | 2   |

|-----|-----------------------------------------------------------------------------------|-----|

|     | Figure 1.2. 5-GHz WLAN frequency allocation for 802.11ax                          | 2   |

|     | Figure 2.1. Direct up-conversion transmitter [34]                                 | 7   |

|     | Figure 2.2. Heterodyne transmitter [34].                                          | 8   |

|     | Figure 2.3. Real-IF transmitter [34].                                             | 9   |

|     | Figure 2.4. PLL modulation transmitter [34].                                      | 10  |

|     | Figure 2.5. Parallel separated chain architecture [1], [3].                       | 11  |

|     | Figure 2.6. Architecture with carriers combined at output of PAs [1], [3]         | 11  |

|     | Figure 2.7. Architecture with carriers combined before PA [1], [3].               | 12  |

|     | Figure 2.8. Architecture with carriers in digital baseband [1], [3].              | 13  |

|     | Figure 2.9. Diagram of the dual-band transmitter architecture with shared baseban | nd. |

| ••• |                                                                                   | 15  |

|     | Figure 2.10. Diagram of the dual-band transmitter architecture enabling concurred | ent |

| lı  | ual-band operation                                                                | 15  |

|     | Figure 3.1. Effect of crosstalk caused by baseband coupling on SNR                | 20  |

|     | Figure 3.2. Effect of crosstalk caused by LO coupling on SNR.                     | 20  |

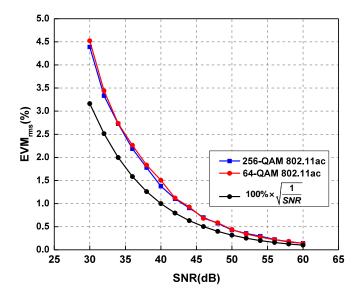

|     | Figure 3.3. EVM versus SNR.                                                       | 22  |

|     | Figure 3.4. Simulated constellation for 802.11ac signals. (a) 64-QAM. (b) 256-QA  | M.  |

| ••• |                                                                                   | 23  |

|     | Figure 3.5. Simulated EVM <sub>rms,avg</sub> versus SNR.                          | 23  |

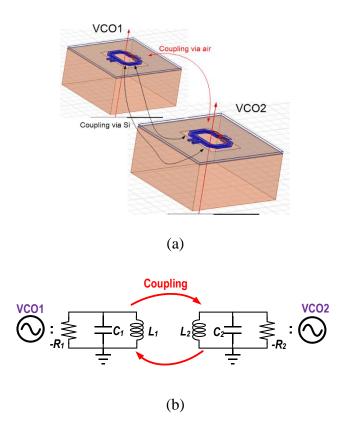

|     | Figure 3.6. Coupling between two VCOs.                                            | 25  |

|     | Figure 3.7. VCO pulling between PLLs.                                             | 26  |

|     | Figure 3.8. Effect of VCO pulling on transmitter for carrier aggregation          | 26  |

| Figure 3.9. Model of VCO pulling between two PLLs                                        |

|------------------------------------------------------------------------------------------|

| Figure 3.10. Simulated magnitude of sideband for pulling PLLs' output with               |

| frequency offset                                                                         |

| Figure 3.11. Spectrum for 80 + 80 MHz contiguous carrier aggregation30                   |

| Figure 3.12. Spectral mask for 80 + 80 MHz contiguous carrier aggregation30              |

| Figure 3.13. Coupling between active devices and between metal signal traces31           |

| Figure 3.14. Model of two active devices in TSMC 40-nm CMOS technology. (a) Top          |

| view. (b) Cross-sectional view                                                           |

| Figure 3.15. Coupling through substrate between active devices                           |

| Figure 3.16. Simulation model in HFSS                                                    |

| Figure 3.17. Simulated coupling factor between two active devices                        |

| Figure 3.18. Model to simulate coupling factor with one active is surrounded by a        |

| guarding ring. (a) Top view. (b) Cross-sectional view                                    |

| Figure 3.19. Simulated coupling factor between one active device and the other active    |

| device with guard ring                                                                   |

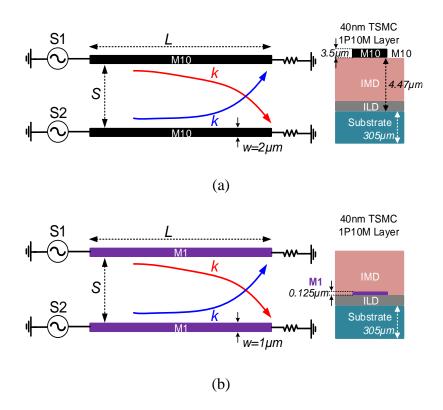

| Figure 3.20. Model to simulate coupling factor for single ended signal traces. (a) Top   |

| metal M10. (b) Bottom metal M1                                                           |

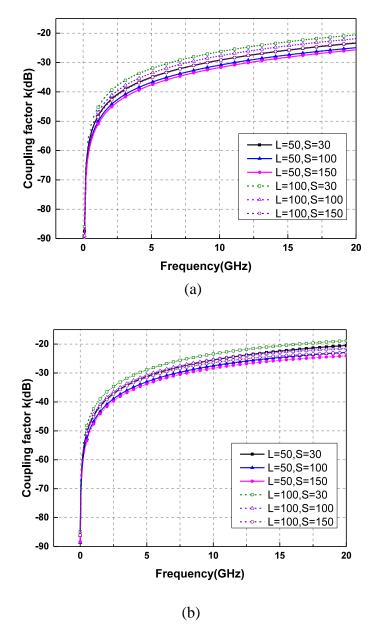

| Figure 3.21. Simulated coupling factor with different length and spacing for single      |

| ended. (a) Top layer metal M10. (b) Bottom layer metal M1                                |

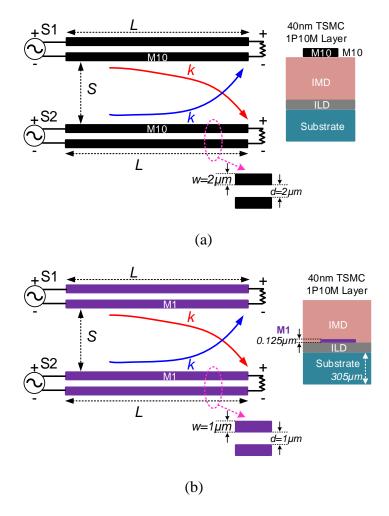

| Figure 3.22. Model to simulate coupling factor for differential signal traces. (a) Top   |

| layer metal M10. (b) Bottom layer metal M1                                               |

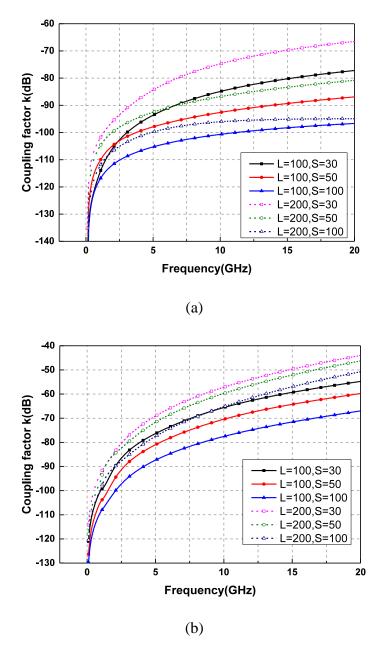

| Figure 3.23. Simulated coupling factor with different length and spacing for             |

| differential signal traces. (a) Top layer metal M10. (b) Bottom layer metal M139         |

| Figure 3.24. Model to simulate coupling factor for non-ideal differential signal traces. |

| 40                                                                                       |

| Figure 3.25. Simulated coupling factor for L=200, S=100 µm with different phase        |

|----------------------------------------------------------------------------------------|

| deviation40                                                                            |

| Figure 3.26. Simulation model for coupling factor between two microstrip lines41       |

| Figure 3.27. Simulated coupling factor between two microstrip lines (unit: $\mu m$ )41 |

| Figure 3.28. Simulation model for coupling factor between two CPWs42                   |

| Figure 3.29. Simulated coupling factor between two CPWs (unit: µm)43                   |

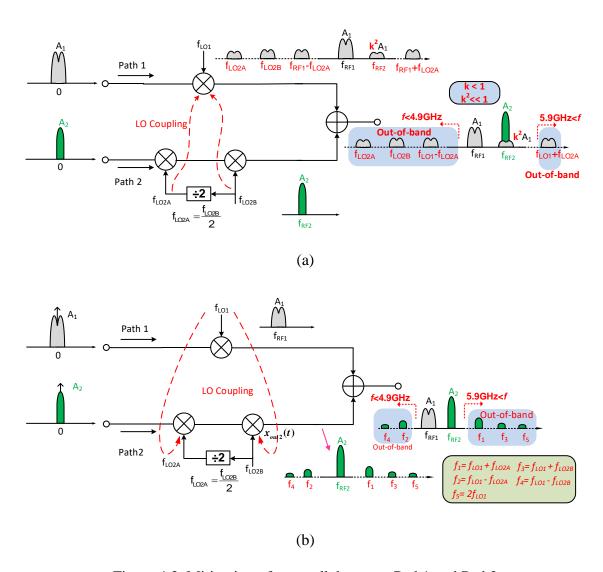

| Figure 4.1. Proposed parallel direct-conversion and double-conversion transmitter      |

| architecture                                                                           |

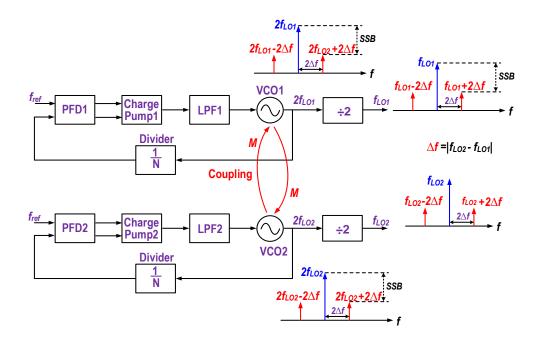

| Figure 4.2. Diagram of LO generator with PLLs integrated on-chip47                     |

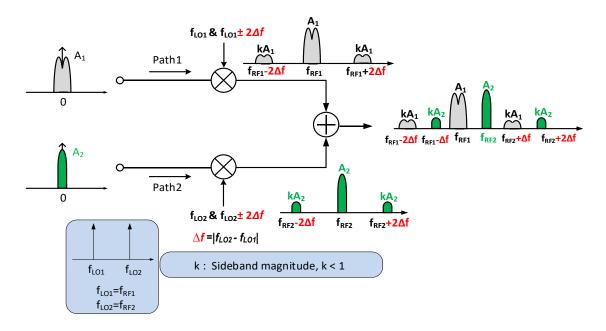

| Figure 4.3. Mitigation of crosstalk between Path1 and Path2                            |

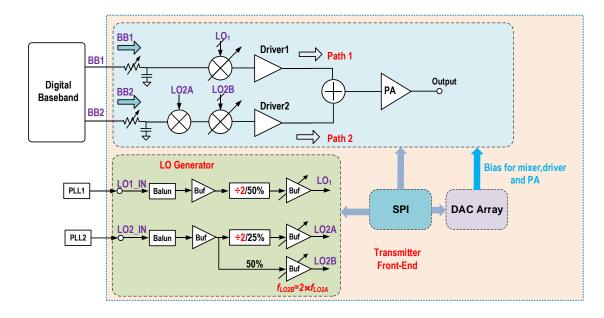

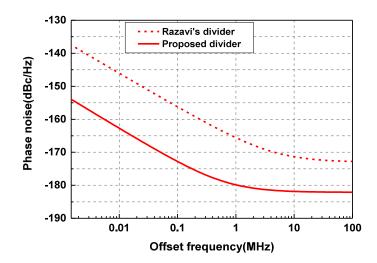

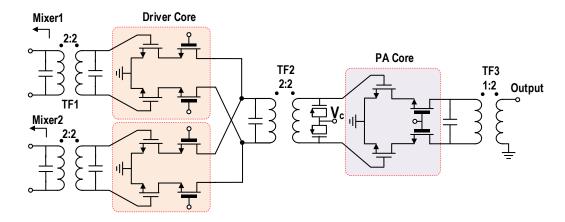

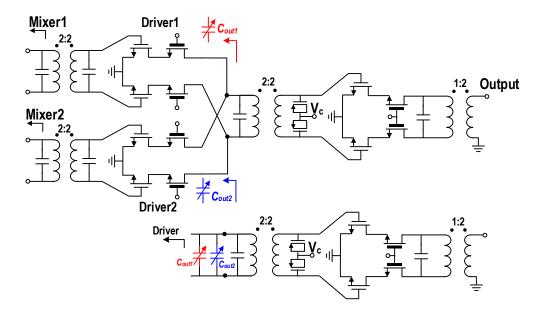

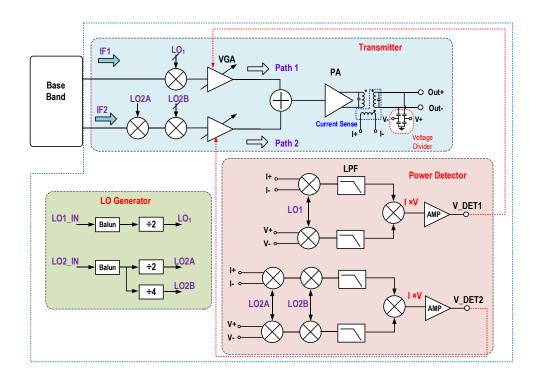

| Figure 4.4. Diagram of the proposed transmitter front-end                              |

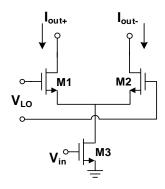

| Figure 4.5. Single-balanced mixer                                                      |

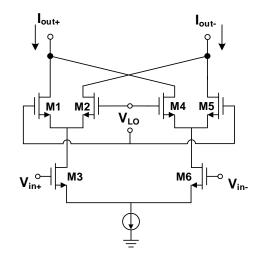

| Figure 4.6. Double-balanced mixer                                                      |

| Figure 4.7. Passive mixer [50]55                                                       |

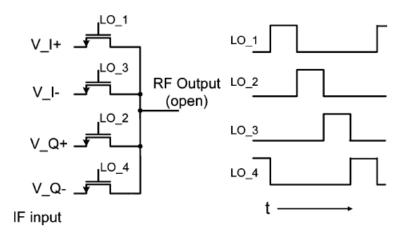

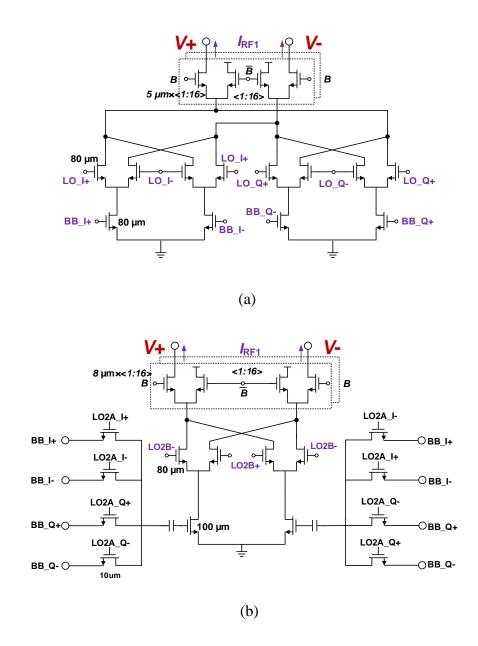

| Figure 4.8. Schematic of the proposed mixer. (a) Path1. (b) Path257                    |

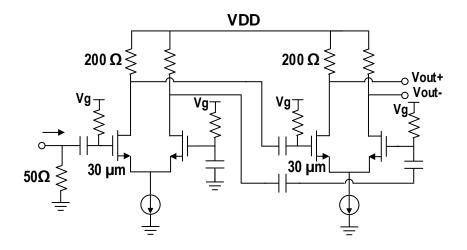

| Figure 4.9. Schematic of the active balun                                              |

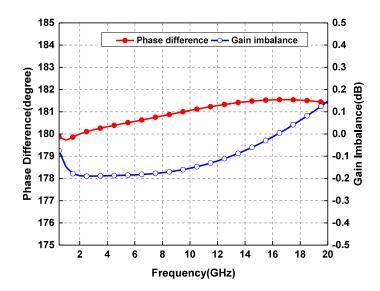

| Figure 4.10. Simulated phase difference and gain imbalance of the active balun59       |

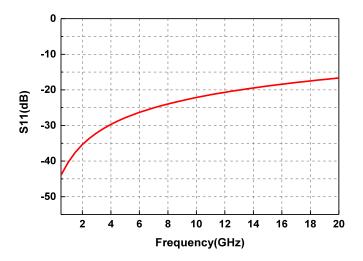

| Figure 4.11. Simulated S <sub>11</sub> of the active balun                             |

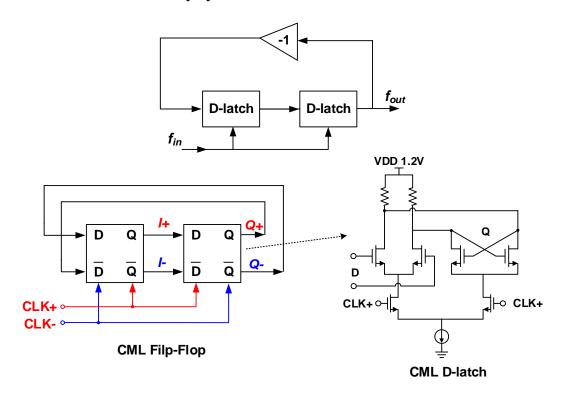

| Figure 4.12. Divider-by-2 with CML flip-flop60                                         |

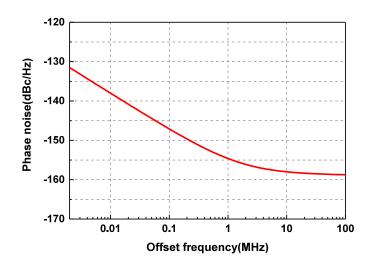

| Figure 4.13. Simulated phase noise of the divider for LO161                            |

| Figure 4.14. Schematic of 25%-duty-cycle divider in Razavi's paper [67]62              |

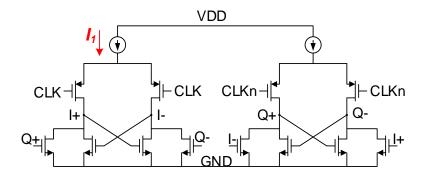

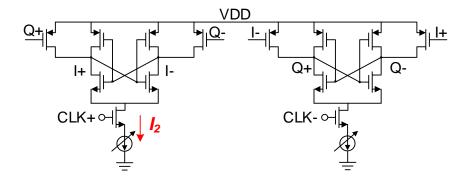

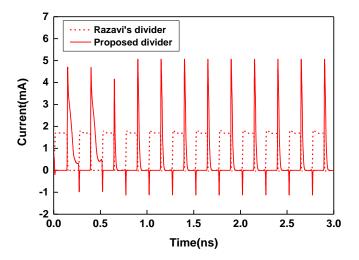

| Figure 4.15. Schematic of the proposed divider                                         |

| Figure 4.16. Simulated current waveforms of Razavi's divider and the proposed          |

| divider63                                                                              |

| Figure 4.17. Simulated phase noises of Razavi's divider and the proposed divider. 64   |

| Figure 4.18. Schematic of the driver and the PA.                                   | 55 |

|------------------------------------------------------------------------------------|----|

| Figure 4.19. (a) Input capacitance compensation. (b) Simulated AM-PM distortion of | of |

| the PA6                                                                            | 57 |

| Figure 4.20. Schematic of the DACs to provide bias voltage6                        | 58 |

| Figure 4.21. Physical structure of the transformers (a) between the mixer and the  | ıe |

| driver. (b) between the mixer and the PA. (c) output6                              | 58 |

| Figure 4.22. Simulated P <sub>sat</sub> and PAE at different frequencies6          | 59 |

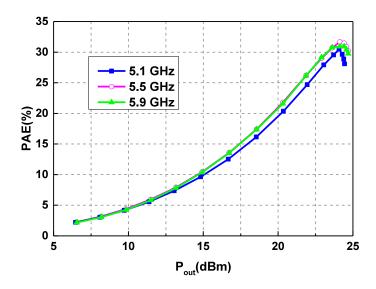

| Figure 4.23 Simulated PAE versus output power at 5.1, 5.5 and 5.9 GHz7             | 70 |

| Figure 4.24. Output capacitance of the two drivers                                 | 71 |

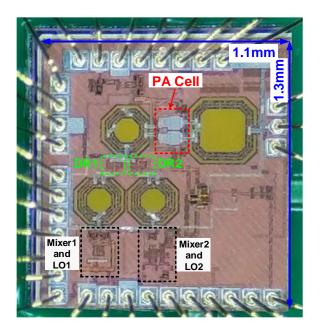

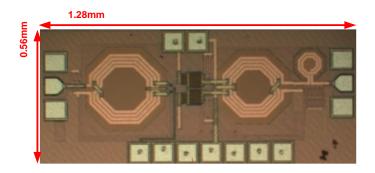

| Figure 4.25. Die photograph of the proposed transmitter front-end                  | 72 |

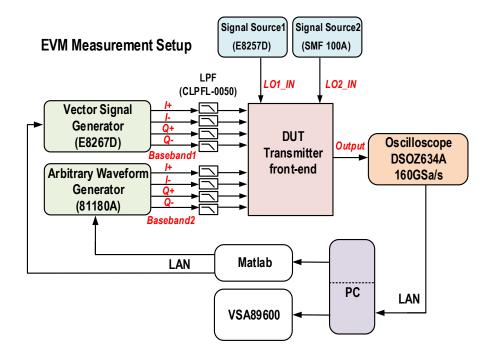

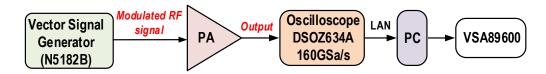

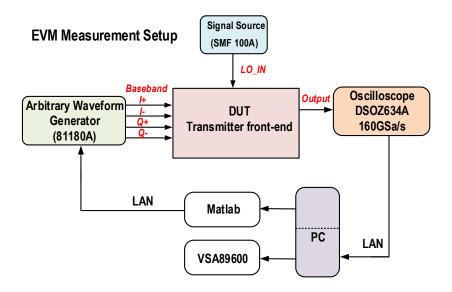

| Figure 4.26. EVM measurement setup                                                 | 72 |

| Figure 4.27. Measured EVM with VHT20, MSC5 802.11ax signal for single carrie       | er |

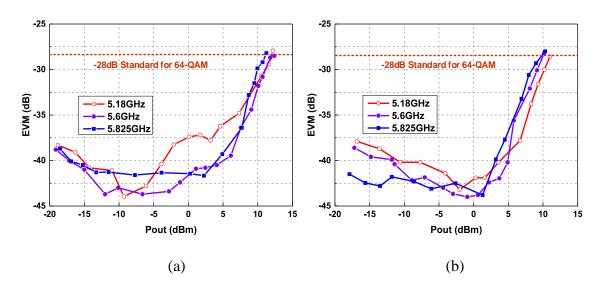

| mode. (a) Path1. (b) Path2                                                         | 74 |

| Figure 4.28. Measured EVM with VHT80, MSC9 802.11ax signal for single carrie       | er |

| mode. (a) Path1. (b) Path27                                                        | 74 |

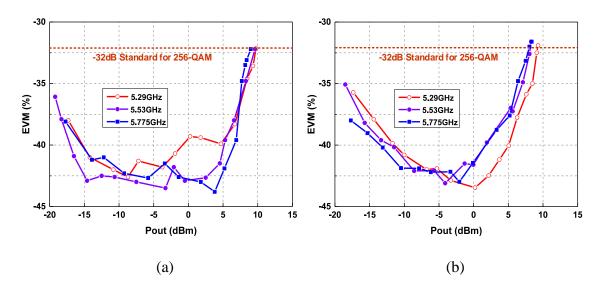

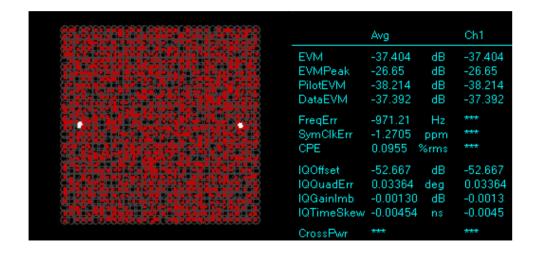

| Figure 4.29. Measured constellation and EVM for Path1 at 5.53 GHz7                 | 15 |

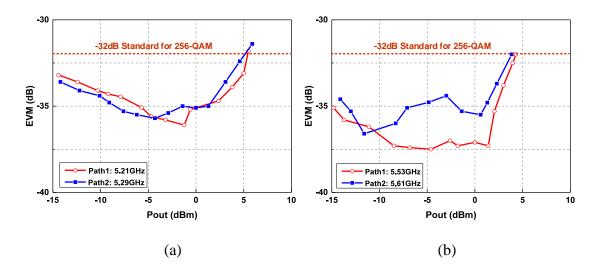

| Figure 4.30. Measured EVM performance for contiguous carrier aggregation mod       | e. |

| (a) 5.21+5.29 GHz. (b) 5.53+5.61 GHz                                               | 76 |

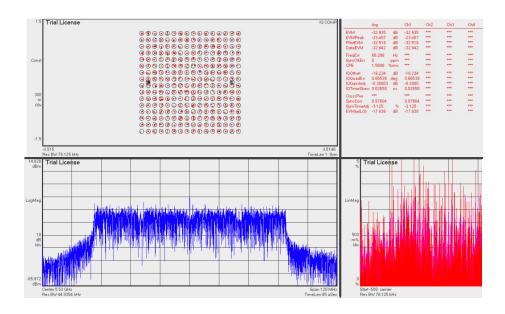

| Figure 4.31. Measured EVM performance for non-contiguous carrier aggregation. (a   | a) |

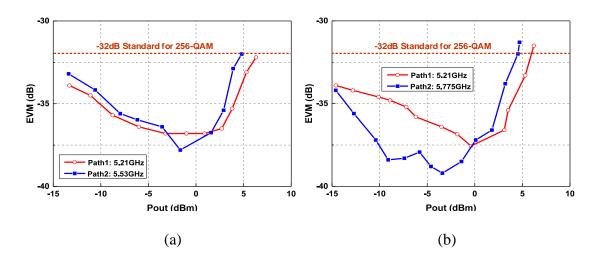

| 5.21+5.53 GHz. (b) 5.21+5.775 GHz. (c) 5.61+5.775 GHz                              | 17 |

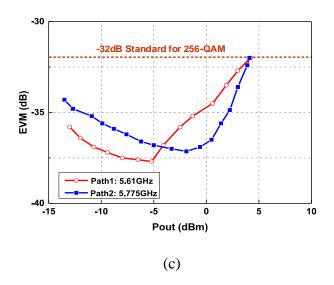

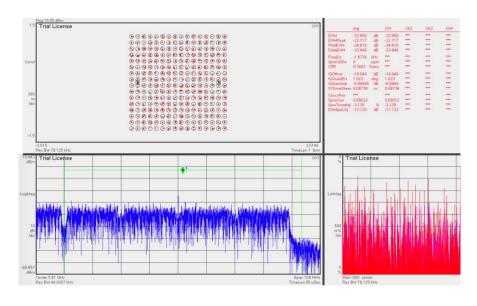

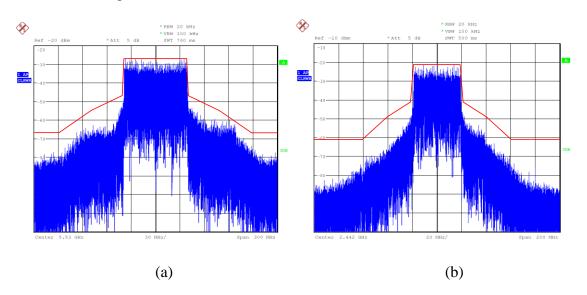

| Figure 4.32. Measured constellation, EVM and spectrum for contiguous carrie        | er |

| aggregation. (a) 5.61 GHz. (b) 5.53 GHz7                                           | 78 |

| Figure 4.33. Spectrum for contiguous carrier aggregation with power difference     | ce |

| between two carriers.                                                              | 30 |

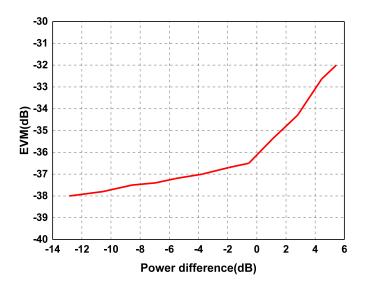

| Figure 4.34 Measured EVM versus power difference                                   | RO |

| Figure 4.35. Measured spectrum for contiguous carrier aggregation. (a) 1-GHz span.                    |

|-------------------------------------------------------------------------------------------------------|

| (b) 5-GHz span                                                                                        |

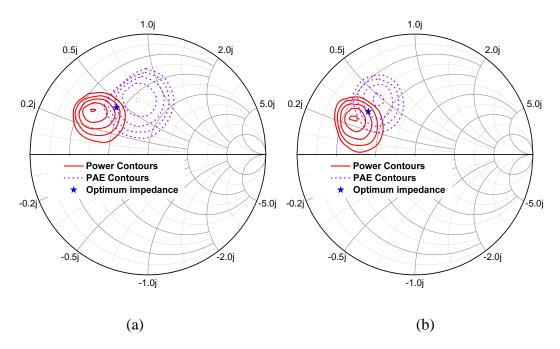

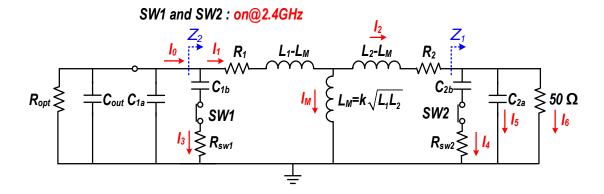

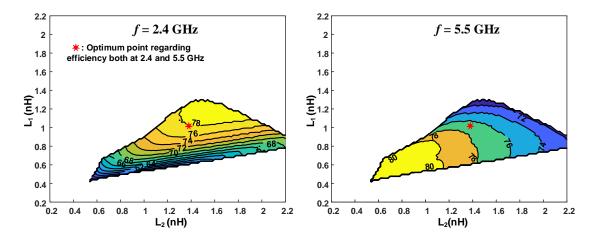

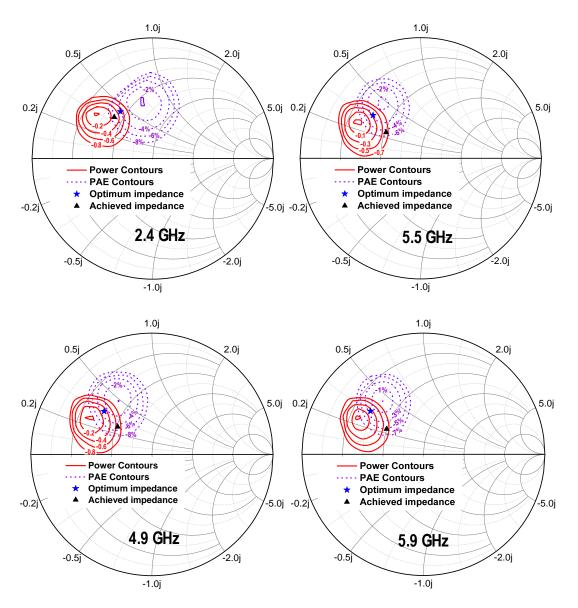

| Figure 5.1. Load-pull simulation results. (a) 2.4 GHz. (b) 5.5 GHz85                                  |

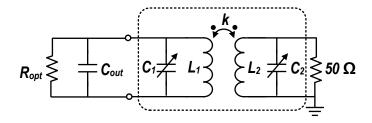

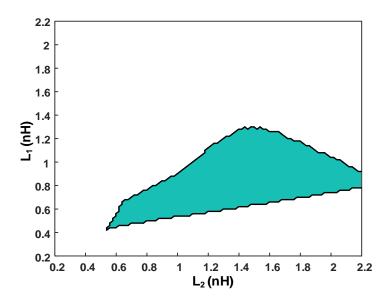

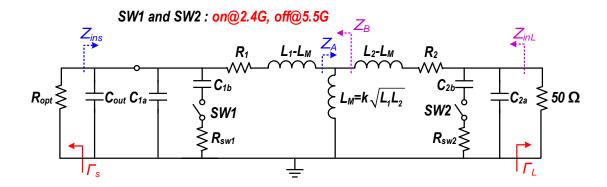

| Figure 5.2. Prototype of the reconfigurable dual-band output matching network86                       |

| Figure 5.3. Equivalent circuit of the dual-band output matching network86                             |

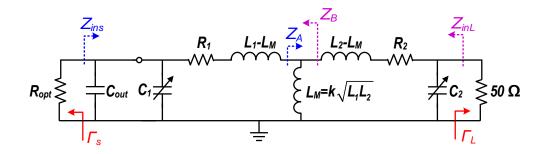

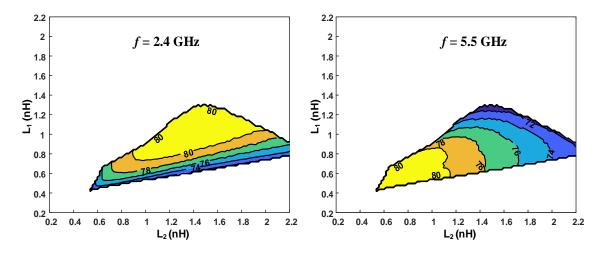

| Figure 5.4. Range of $L_1$ and $L_2$ where optimum impedances can be achieved at 2.4 and              |

| 5.5 GHz                                                                                               |

| Figure 5.5 Efficiency contours of output matching network in achieved range, and                      |

| unit in contours is %                                                                                 |

| Figure 5.6. Equivalent practical circuit of dual-band output matching network89                       |

| Figure 5.7. Model used to calculate efficiency of output matching network90                           |

| Figure 5.8. Efficiency contours of output matching network with considering on-                       |

| resistance of switches, and unit in contours is %                                                     |

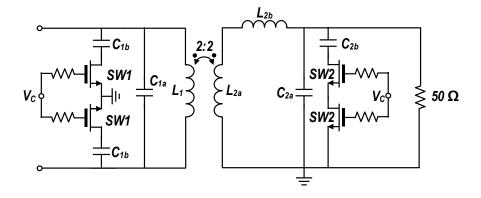

| Figure 5.9. Implemented the dual-band output matching network92                                       |

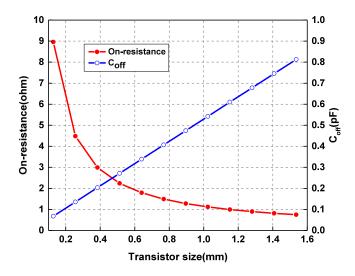

| Figure 5.10. On-resistance and $C_{off}$ of the switch transistor versus size93                       |

| Figure 5.11. Achieved load impedance of implemented output matching network in                        |

| 2.4- and 5-GHz bands                                                                                  |

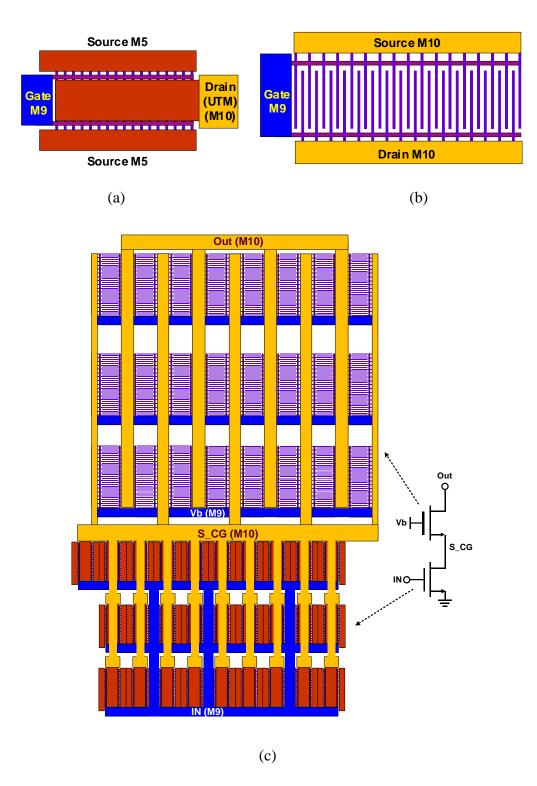

| Figure 5.12. Layout of the cascode structure in the PA core96                                         |

| Figure 5.13. Schematic of the dual-band PA                                                            |

| Figure 5.14. Micrograph of the fabricated PA                                                          |

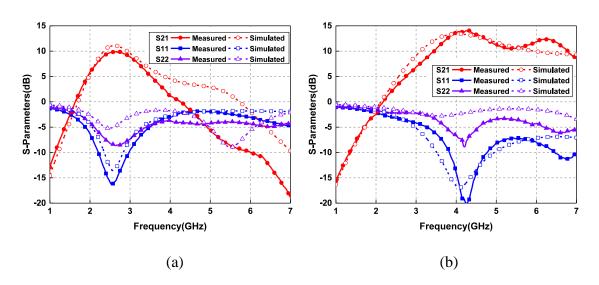

| Figure 5.15. Measured S-parameters. (a) 2.4-GHz mode. (b) 5-GHz mode98                                |

| Figure 5.16. Measured P <sub>sat</sub> , power gain and PAE <sub>max</sub> at different frequencies99 |

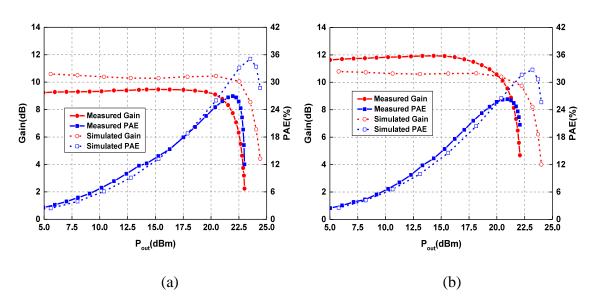

| Figure 5.17. Measured power gain and PAE versus output power. (a) At 2.4 GHz. (b)                     |

| At 5.5 GHz mode.                                                                                      |

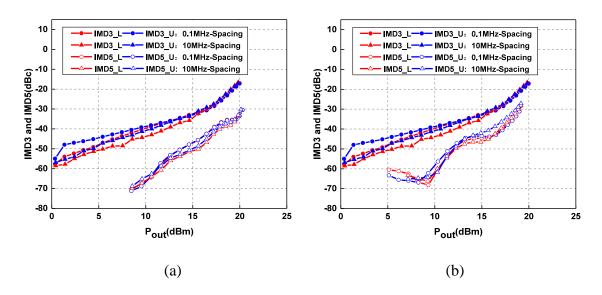

| Figure 5.18 Measured IMD3 and IMD5 (a) At 2.4 GHz (b) At 5.5 GHz                                      |

| Figure 5.19. PA's EVM measurement setup                                                        |

|------------------------------------------------------------------------------------------------|

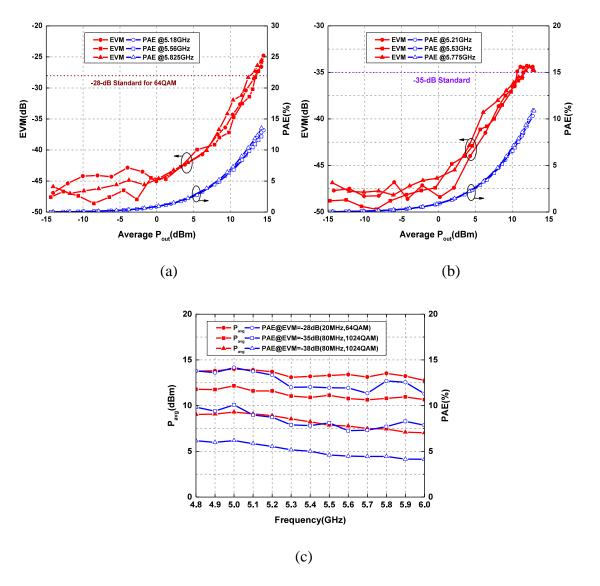

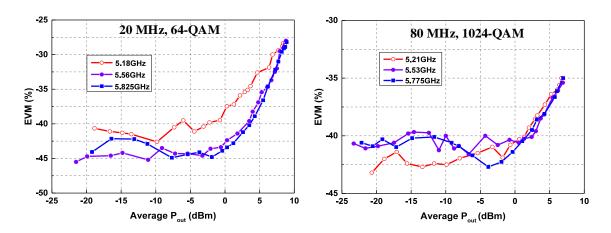

| Figure 5.20. Measured EVM performance in 5-GHz band. (a) EVM and PAE                           |

| different average output power levels for 20MHz, 64-QAM signal. (b) For 80MHz, 102             |

| QAM signal. (c) P <sub>avg</sub> and PAE versus frequencies when EVM requirements are satisfie |

|                                                                                                |

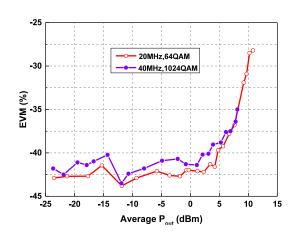

| Figure 5.21. Measured EVM performance in 2.4-GHz mode. (a) EVM and PAE                         |

| different average output power levels at 2.442 GHz. (b) $P_{avg}$ and PAE versus frequencies   |

| when EVM requirements are satisfied.                                                           |

| Figure 5.22. Diagram of the transmitter front-end.                                             |

| Figure 5.23. Schematic of the LPF.                                                             |

| Figure 5.24. Schematic of the mixer10                                                          |

| Figure 5.25. Low-pass prototype and band-pass network10                                        |

| Figure 5.26. Inter-stage matching network and Norton transformation10                          |

| Figure 5.27. Micrograph of the fabricated dual-band transmitter front-end10                    |

| Figure 5.28. EVM measurement setup                                                             |

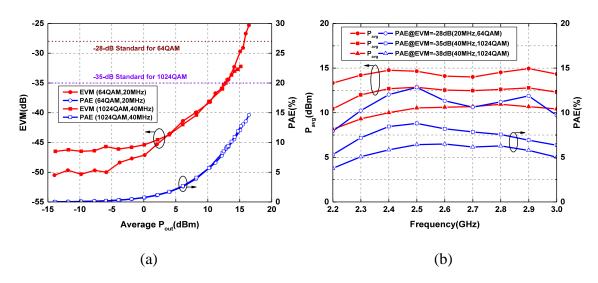

| Figure 5.29. Measured EVM versus output levels for different modulation signals                |

| 5-GHz mode.                                                                                    |

| Figure 5.30. Measured EVM in different output levels for modulation signal at 2.44             |

| GHz                                                                                            |

| Figure 5.31. Measured 1024-QAM constellation at 5.53 GHz.                                      |

| Figure 5.32. Output spectrum from transmitter front-end. (a) VHT80, MCS10 sign                 |

| at 5.53 GHz. (b)VHT40, MCS10 signal at 2.442 GHz                                               |

| Figure 6.1. True power detector [105]                                                          |

| Figure 6.2 Transformer with current sense coil                                                 |

|    | Figure    | 6.3. | Possible   | transmitter   | architecture | with   | power    | detector  | tor   | carrier  |

|----|-----------|------|------------|---------------|--------------|--------|----------|-----------|-------|----------|

| ag | ggregatio | n    |            |               |              |        |          |           | ••••• | 118      |

|    | Figure    | 6.4. | Transmitte | r architectur | e supporting | dual-l | oand and | d carrier | aggre | egation. |

|    |           |      |            |               |              |        |          |           |       | 119      |

### **List of Tables**

| Table 2-1.     | . Comparison of different transmitter architectures for CA    | 14          |

|----------------|---------------------------------------------------------------|-------------|

| Table 4-1      | Measured performance summary and compassion with state        | -of-the-art |

| 802.11ac/ax    | transmitters.                                                 | 79          |

| Table 5-1.     | . Performance comparison with other broadband and dual-band P | 'As100      |

| Table 5-2.     | . Performance comparison of state-of-the-art 802.11ac PAs     | 103         |

| Table 5-3      | . Transmitter front-end performance summary and comparison    | with state- |

| of-the-art 802 | 2.11ac/ax transmitter.                                        | 112         |

#### **List of Acronyms**

ACLR Adjacent Channel Leakage Ratio

AWG Arbitrary Waveform Generator

BPF Band-Pass Filter

CMOS Complementary Metal-Oxide Silicon

CA Carrier Aggregation

CML Current-Mode Logic

CPW Coplanar Waveguide

DAC Digital-to-Analog Convertor

DPD Digital Pre-Distortion

EM Electromagnetic

EVM Error Vector Magnitude

GMSK Gaussian Minimum Shift Keying

ISM Industrial, Scientific, and Medical

IF Intermediate Frequency

LPF Low-Pass Filter

LO Local Oscillator

OFDMA Orthogonal Frequency-Division Multiple Access

OQPSK Offset Quadrature Phase-Shift Keying

PA Power Amplifier

PAE Power-Added Efficiency

PAPR Peak-to-Average Power Ratio

PGA Programmable-Gain Amplifier (PGA)

PLL Phase-Locked Loop

PPA Pre-PA Amplifier

P<sub>sat</sub> Saturated Output Power

QAM Quadrature Amplitude Modulation

SNR Signal-to-Noise Ratio

VCO Voltage-Controlled Oscillator

VGA Variable-Gain Amplifier

V-I Voltage-to-Current

VSG Vector Signal Generator

WLAN Wireless Local Area Network

5G Fifth-Generation

#### Chapter 1

#### Introduction

#### 1.1 Motivation

Recently, the accelerating growth of smartphones and mobile devices is propelling the wireless communication to evolve towards higher data rate. Currently, the development of new IEEE 802.11 standards, driven by the increasing demand on the broadband wireless local area network (WLAN), becomes a hot research topic in recent years. As the main 5-GHz WLAN standards, IEEE 802.11ac system utilizes a wider bandwidth and more complex modulation scheme, and thus can provide up to 866 Mbps date rate. As the successor to current IEEE 802.11ac, the emerging IEEE 802.11ax introduces orthogonal frequency-division multiple access (OFDMA), utilizes smaller sub-carrier spacing and employs 1024-quadrature amplitude modulation (QAM) to improve overall spectrum efficiency and boost the data rate. Besides, carrier aggregation (or channel bonding) technique is a key feature of 802.11ax standard to increase the data rate significantly. By introducing carrier aggregation, the data rate of 802.11ax is expected to reach 10 Gb/s, in order to meet the tremendous demand for high data rate applications, such as interactive and high-definition video.

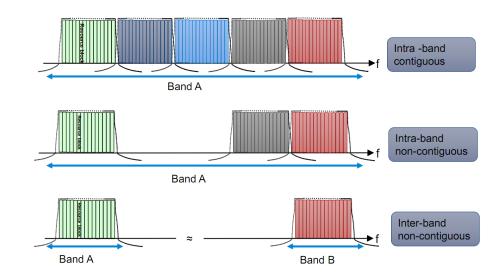

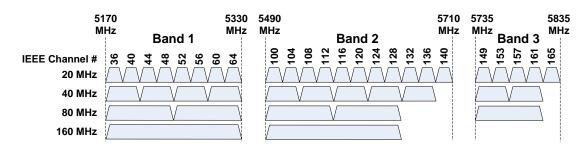

Carrier aggregation (CA), originating from LTE-Advanced, combines multiple contiguous or non-contiguous frequency bands together, to form a wider frequency band to increase the transmission data rate. There are three kinds of carrier aggregation: intraband contiguous aggregation, intra-band non-contiguous aggregation, and inter-band non-contiguous aggregation [1], as shown in Figure 1.1. In the 5-GHz band, three discontinuous frequency bands are allocated for 802.11ax: 5.17 GHz ~ 5.33 GHz, 5.49 GHz ~ 5.71 GHz, and 5.735 GHz ~ 5.835 GHz [2], as shown in Figure 1.2. In practical

application, all three carrier aggregation modes will be supported in 802.11ax transceiver.

Figure 1.1. Carrier aggregation scenarios.

Figure 1.2. 5-GHz WLAN frequency allocation for 802.11ax.

Some transmitter architectures have been introduced and discussed in [1] and [3]. The main difference between these proposed architectures lies in where the carriers are combined in the transmitter. To support intra-band contiguous carrier aggregation, a single transmitter chain with all carriers aggregated at digital baseband is feasible [4]. Since the aggregated signals are processed in only one RF transmitter chain after generated from digital-to-analog convertor (DAC), this architecture is the least complex architecture in terms of the number of RF blocks required. In practice, this architecture can further support non-contiguous carrier aggregation with a small frequency spacing. However, in 802.11ax application scenario where the frequency spacing between carriers is quite large, the sampling rate of DAC has to be extremely high accordingly, causing

considerable power consumption and intensifying the complexity of DAC.

To support inter-band carrier aggregation, the architecture with carriers combined in RF part can be utilized. However, the conventional architecture for carrier aggregation in RF part has inherent problems of crosstalk and voltage-controlled oscillator (VCO) pulling caused by the interaction between transmitter channels in RFIC implementation [5]-[9], which introduce severe impacts on adjacent channel leakage ratio (ACLR) and error vector magnitude (EVM). To address these two problems, high isolation between the transmitter channels is required. In order to increase the isolation and reduce the interaction between the transmitter channels, a sufficiently large physical separation between transmitter channels is required. However, in practice, large physical separation between transmitter channels requires a large chip size, and may not be achieved due to the constraint of layout in some cases. Thus, one motivation of the work in this thesis is to propose a new carrier aggregation transmitter architecture that can effectively mitigate the problems of crosstalk and VCO pulling simultaneously without a large physical isolation required on-chip.

Besides the 5-GHz WLAN band, 802.11ax will also operate in the existing unlicensed 2.4-GHz band. Therefore, 802.11ax's devices will be designed with the dual-band operation, requiring a dual-band transmitter or a broadband transmitter covering both the 2.4- and 5-GHz bands. In the literature and commercial products, two separate RF transmitting channels with different operating frequencies are integrated together to enable the 2.4/5-GHz dual-band operation [10]-[20]. Although the architecture using two RF channels can meet the requirement of the dual-band operation for 802.11ax, the chip size will be large and the cost will be high due to two RF channels used. In terms of low cost, a single transmitter supporting reconfigurable 2.4/5-GHz operation is superior to the dual-band architecture using two transmitters. Currently, no reconfigurable dual-band

transmitter using only one transmitting channel is available in academia and industry. Therefore, the other motivation of the thesis is driven by the requirement for such a reconfigurable 2.4/5-GHz dual-band transmitter front-end.

As a core block in a transmitter, the power amplifier (PA) should operate in dual bands or in a broadband to cover both the 2.4- and 5-GHz bands. There are two general approaches that have been proposed to implement dual-band or multi-band and broadband PAs in complementary metal-oxide silicon (CMOS) technology. The first approach is based on using distributed configurations [21]-[23] and various broadband matching techniques such as reactive filter synthesis [24]-[28]. Nevertheless, no matter using the distributed configurations or the broadband matching techniques, PAs inherently suffer from low power efficiency and large size, making them unsuitable for low cost application. The other approach is based on using reconfigurable components in the matching networks, such as switches [29]-[31]. However, in the relevant publications, the passive efficiency of the reconfigurable dual-band matching network is quite low, having a significant impact on PAs' final efficiencies. Therefore, one more effort of this thesis is to design such a reconfigurable 2.4/5-GHz dual-band PA with high efficiency in the dual-band transmitter front-end.

#### 1.2 Major Contribution

The major contribution of this thesis is summarized as follows.

1. Crosstalk and VCO pulling are two main problems related to carrier aggregation, which are caused by inevitable coupling or leakage though low-resistance Si substrate and electromagnetic radiation. In this thesis, the effect of crosstalk between different signal paths on signal-to-noise (SNR) and EVM for 802.11ax signal is thoroughly analysed. Besides, VCO pulling is investigated, and the impact of VCO pulling on ACLR is demonstrated. Furthermore, the coupling strength between different signal paths in

practical layout is explored, indicting a large physical separation between transmitter channels is required to guarantee a low coupling strength.

- 2. In some practical cases, due to the constraint of layout, high isolation between signal transmitting channels may not be realized to address the problems of crosstalk and VCO pulling. A new transmitter architecture using parallel direct-conversion and double-conversion configuration is proposed to solve the problems of crosstalk and VCO pulling simultaneously without a large physical isolation requirement. The proposed transmitter architecture can support arbitrary mode of carrier aggregation for 802.11ax in the 5-GHz WLAN band. A 5-GHz transmitter front-end supporting two-carriers aggregation is designed to verify the effectiveness of the proposed transmitter architecture.

- 3. Besides the 5-GHz WLAN band, 802.11ax systems operate in the 2.4-GHz WLAN band, requiring a 2.4/5-GHz dual-band PA and dual-band transmitter front-end. A new design methodology of a reconfigurable dual-band output matching network with high passive efficiency is proposed. A 2.4/5-GHz dual-band PA is designed to validate the methodology, and the synthesis procedure of the reconfigurable output matching network is described in detail, providing a guideline for other researchers to employ the proposed methodology. Based on the implemented standalone PA, a 2.4/5-GHz dual-band transmitter front-end is designed and implemented, which is the first published design for dual-band WLAN 802.11ax application in the literature and industry.

#### 1.3 Thesis Organization

This thesis is organized as follows.

Chapter 2 firstly gives a brief review on the transmitter architectures for single carrier and some possible transmitter architectures for carrier aggregation. Secondly, these transmitter architectures for carrier aggregation are compared in terms of their applicability, cost and system's complexity. Finally, the prevalent dual-band WLAN

transmitter architectures in commercial products are discussed.

In Chapter 3, firstly, the problem of crosstalk related to carrier aggregation is introduced, and the impact of crosstalk on EVM for different modulation schemes including 64-QAM and 256-QAM is theoretically investigated. Then, the degradation of ACLR caused by VCO pulling is analysed. Finally, to explore the isolation between two practical RF channels, the coupling strength between active devices and between the passive signal traces in TSMC 40-nm technology are simulated.

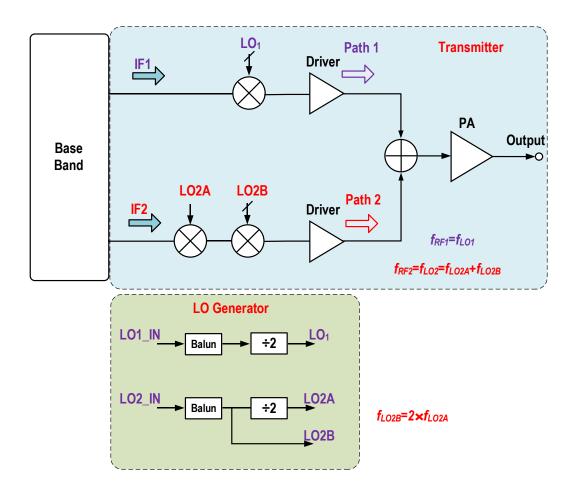

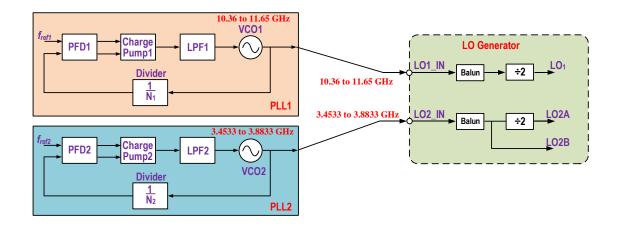

Chapter 4 presents a novel carrier aggregation transmitter architecture using parallel direct-conversion and double-conversion configuration to solve the problems of crosstalk and VCO pulling, and explicitly explains the mechanism of crosstalk and VCO pulling mitigation. Based on the proposed architecture, a transmitter front-end is designed and implemented in TSMC 40-nm technology. The implemented transmitter front-end consists of LO generator, mixer, driver and PA, and the design of these circuit blocks are described. The transmitter front-end is measured using two 802.11ax signals with 80-MHz bandwidth and 256-QAM, and the measurement results are reported in Chapter 4.

In Chapter 5, a new design methodology of a reconfigurable dual-band output matching network to achieve high passive efficiency is introduced. By employing the proposed methodology, a 2.4/5-GHz dual-band standalone PA and transmitter front-end are designed and fabricated, and the experimental results are presented.

Finally, Chapter 6 concludes the work in this thesis and gives some recommendations for the future works.

#### Chapter 2

#### **Review of transmitter**

The transmitter is the building block of the communication systems, and it is the physical layer of the system and the actual device that sends the modulated signal through wireless channel. Thus, the transmitter plays a key role in the performance of wireless communication systems. In this chapter, to better understand transmitter architecture, we firstly introduce some conventional transmitter architectures for single carrier [32]-[35]. Then, a brief review on some transmitter architectures applicable for carrier-aggregation is given, and the design challenges in terms of their applicability, cost and complexity of system are discussed for these transmitter architectures. In addition, two dual-band transmitter architectures used in the commercial 2.4/5-GHz dual-band WLAN products are reviewed.

#### 2.1 Conventional transmitter architecture

#### 2.1.1 Direct up-conversion transmitter

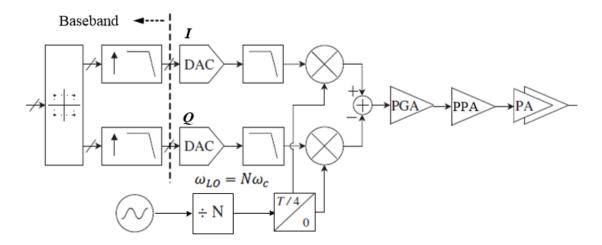

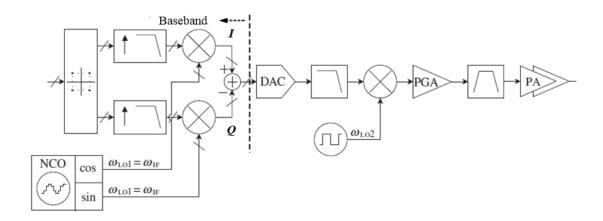

Figure 2.1. Direct up-conversion transmitter [34].

The direct up-conversion transmitter shown in Figure 2.1 is the most common

transmitter architecture, and this topology directly converts the baseband spectrum to the RF carrier. The up-conversion mixer is followed by the amplification blocks including a programmable-gain amplifier (PGA) or variable-gain amplifier (VGA), a Pre-PA amplifier (PPA) and a PA. The analog baseband I and Q signals are filtered by a low-pass filter before being applied to the up-conversion mixer. To avoid oscillator pulling, local oscillator (LO) frequency  $f_{LO}$  is chosen sufficiently far from carrier frequency  $f_c$ . Mostly,  $f_{LO}$  is chosen as twice  $f_c$ . However, this architecture cannot fully eliminate injection pulling, since PA's nonlinearity produces a finite power at the second harmonic of the carrier. Besides injection pulling, this architecture suffers from other drawbacks: IQ mismatch, DC offset, LO leakage. In order to compensate these drawbacks, the digital assisted calibrations are employed.

#### 2.1.2 Heterodyne transmitter

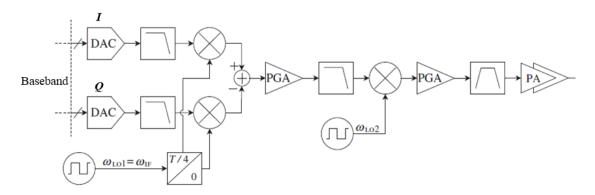

Figure 2.2. Heterodyne transmitter [34].

To avoid injection pulling, another transmitter architecture is proposed, named twostep architecture or heterodyne architecture, as shown in Figure 2.2. The up-conversion is performed in two steps: the baseband I and Q signals are first up-converted to an intermediate frequency (IF)  $\omega_1$ , and then the IF signal is translated to a carrier frequency  $\omega_1+\omega_2$ . As a result, the LO frequency remains far from the PA output spectrum. Since the quadrature modulation is performed at lower frequency, IQ matching is superior to that in the direct up-conversion architecture. In this architecture, a passive bandpass filter is required to reject the unwanted sideband. Compared with the direct up-conversion architecture, this architecture has a higher complexity of implementation and larger chip area, resulting in a higher cost. In addition, the power consumption is also higher due to more circuit blocks used in the transmitter.

#### 2.1.3 Real-IF transmitter

Figure 2.3. Real-IF transmitter [34].

Real-IF transmitter architecture is presented in Figure 2.3. In this architecture, the modulated IF signal is generated in digital domain. Due to the high accuracy associated with the digital signal processing, the imbalance between I and Q signals is negligible. Besides, no LO leakage exists in the transmitter, and in-band image signal is also negligible. Moreover, the digital implementation allows for great agility in phase or frequency jump of the LO waveforms, thus, this architecture could be used in the application involving frequency hopping. Another advantage of this architecture is that only one DAC is used along the signal path. While, since the IF modulation is realized in digital domain, the sampling rate in the digital signal processing is quite high, inducing a high power consumption.

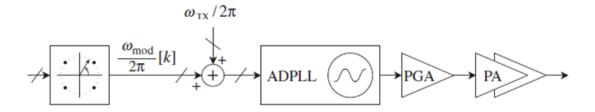

#### 2.1.4 PLL modulation transmitter

Figure 2.4. PLL modulation transmitter [34].

Phase-locked loop (PLL) modulation transmitter architecture shown in Figure 2.4 is suited to the systems with constant-envelope or pure phase/frequency modulation, such as offset quadrature phase shift keying (OQPSK), pi/4QPSK, Gaussian minimum shift keying (GMSK), PSK. In practice, this architecture is often used in Bluetooth. The main benefit of this architecture is that the minimum set of the processing blocks are required to generate phase/frequency modulation. This architecture also suffers from oscillator pulling. The intrinsic limitation of this architecture is that it cannot be used in the systems with non-constant envelope modulation, such as QPSK and QAM in WLAN and LTE applications.

#### 2.2 Transmitter architecture for carrier aggregation

In order to support carrier aggregation, the baseline transmitter for single-carrier operation can be extended in several ways. The topology of transmitter architecture depends on where the aggregated carriers are combined in the transmitter. Here, four main possible transmitter architectures for carrier aggregation are introduced [1], [3].

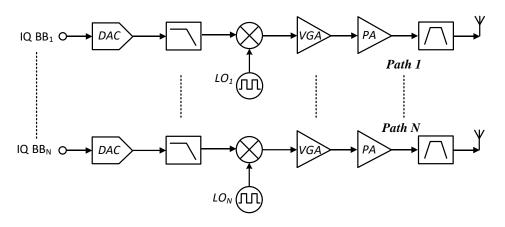

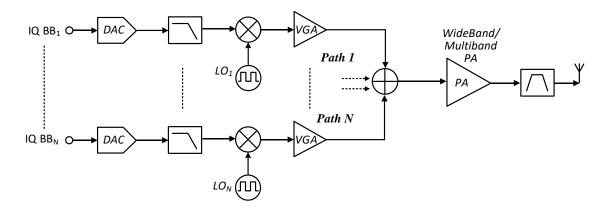

#### 2.2.1 Architecture with parallel fully separated chains

This architecture includes multiple separated transmitters, and each transmitter consists of a baseband chain, an up-conversion mixer, an amplification unit, an output bandpass filter and an antenna, as shown in Figure 2.5. In practice, this topology is well suitable for inter-band carrier aggregation. While, due to multiple passive filters and

antennas used, this architecture is not economically efficient, and it can only be implemented in the case where there is no constraint by the cost. Practically speaking, this architecture is not feasible for the system where the cost is limited, such as mobile phone. Although it has potential to be used in 5-GHz WLAN 802.11ax access points if the overall size and cost are not concerned, using too many antennas will become troublesome in mobile phone when supporting more than two carriers.

Figure 2.5. Parallel separated chain architecture [1], [3].

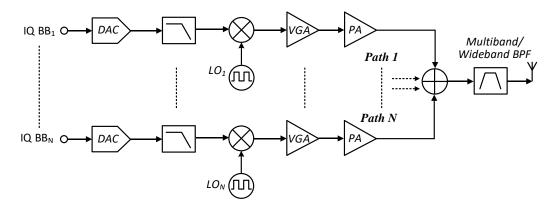

#### 2.2.2 Architecture with carriers combined after PAs

Figure 2.6. Architecture with carriers combined at output of PAs [1], [3].

In order to reduce the number of the passive components (filters and antennas), another candidate architecture is proposed for carrier aggregation [1], [3], as shown in Figure 2.6. In this architecture, the RF output signals from the PAs are combined through a RF combiner or multiplexer. For inter-band carrier aggregation, if the frequency

spacing between the aggregated carries are too large, all the passive components including RF combiner or multiplexer, filter and antenna are required to have a wideband or multiband performance. In practice, it is a great challenge to design such wideband or multiband passive components.

Besides, the PAs may affect each other, causing the load modulation effect, which has a drastic impact on the linearity of the output signal from the PAs and leads to an extreme degradation on EVM performance. In order to avoid load modulation effect between the PAs, the port isolation of the combiner or multiplexer should be sufficiently high, which further intensifies the difficulty in designing RF combiner or multiplexer. In CMOS technique, RF combiner or multiplexer with high port isolation is unavailable. For this reason, off-chip RF combiner or multiplexer is required, bringing in an external cost besides the cost of the filter and antenna.

#### 2.2.3 Architecture with carriers combined before PA

Figure 2.7. Architecture with carriers combined before PA [1], [3].

An alternative architecture is shown in Figure 2.7 [1], [3], [8]. In this architecture, the RF signals are combined before the power amplifier, and only one PA with multi-band or broadband performance is utilized. Since the transistor size of the VGAs is much smaller than that of the PAs, the load modulation between the VGAs is negligible. Therefore, no isolation is required associated with the combination of the carriers.

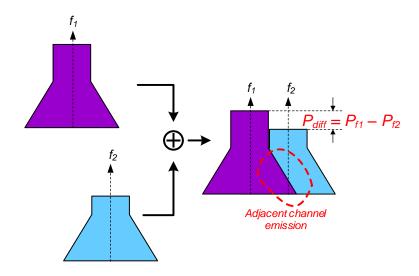

After combination, the PA processes multiple carriers concurrently, and the total bandwidth of the signals processed in the PA is the sum of all carriers' bandwidth. In this case, the adjacent channels emission of one carrier will decrease the SNRs of other carriers and will further impact the EVMs of other carriers. Thus, the requirement of the linearity is more stringent for the PA processing multiple carriers, compared to the PA processing only one carrier. Consequently, the main practical challenge for this architecture is designing a multi-band/broadband power amplifier with high linearity and high efficiency.

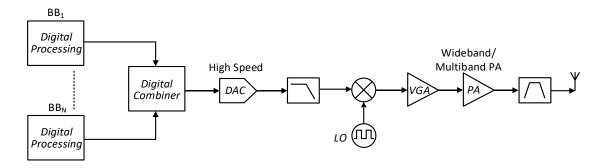

#### 2.2.4 Architecture with carriers combined in baseband

Figure 2.8. Architecture with carriers in digital baseband [1], [3].

Different from the architectures with the carriers combined in the RF part, another possible architecture with the carriers aggregated in digital baseband is presented in Figure 2.8. In this architecture, the aggregated signals from the DAC are processed in only one transmitter chain. As a result, this architecture is the least complex architecture in terms of the number of RF blocks required. While, since the aggregated baseband signal is converted from digital domain to analog domain through a single DAC, the bandwidth of the aggregated signal is constrained by the sampling rate of the DAC. Hence, this architecture is suitable for contiguous intra-band CA or non-contiguous CA with a small frequency spacing between the carriers. For the scenario where the frequency spacing between the carriers is quite large, the sampling rate of the DAC has

to be at least twice the frequency spacing, and will be extremely large, causing considerable power consumption and intensifying the complexity of the DAC. For example, the sampling rates of the DAC are 3.9 GS/s and 1.14 GS/s in [4] and [37], respectively. In order to support inter-band carrier aggregation in the 5-GHz WLAN bands, the sampling rate of the DAC will exceed 1.2 GS/s. Besides, since the carriers are combined in the digital baseband, the complexity of the baseband digital processing will drastically increase, and more digital hardware resources will be occupied and more power will be consumed.

#### 2.2.5 Summary of different architectures

Table 2-1. Comparison of different transmitter architectures for CA.

| Architecture | Suitable for cellphone | RF<br>Complexity | Cost of RF<br>Part | Inter-<br>band CA | Intra-<br>band CA |  |

|--------------|------------------------|------------------|--------------------|-------------------|-------------------|--|

| 1            | No                     | Low              | High               | Yes               | Yes               |  |

| 2            | Yes                    | High             | High               | Yes               | Yes               |  |

| 3            | Yes                    | Low              | Medium             | Yes               | Yes               |  |

| 4            | Yes                    | Low              | Low                | No                | Yes               |  |

Architecture 1, 2, 3 and 4 are the architectures discussed in section 2.2.1-2.2.4, respectively.

To summarize, the comparison of the above mentioned transmitter architectures for carrier aggregation is listed in Table 2-1. Due to the high cost caused by using multiple filters and antenna, Architecture-1 with multiple separated transmitter chains is not suitable for low cost WiFi application in cellphone. Although Architecture-2 with the carriers combined after the power amplifier uses only one filter and one antenna, a broadband combiner with high port isolation is required to alleviate the load modulation between the power amplifiers, which will intensify the complexity of the RF part and increase the cost of the whole transmitter. As for Architecture-4 with the carriers aggregated at digital baseband, it features the lowest complexity of RF part, though, it is not suitable for inter-band carrier aggregation due to extremely high sampling rate of

baseband signal processing. Therefore, considering the feasibility and cost of the RF part, Architectue-3 with the carriers combined before the power amplifier is prior to other architectures to support arbitrary carrier aggregation mode for 5-GHz WLAN 802.11ax application in cellphone.

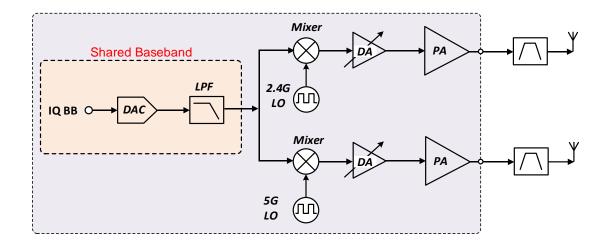

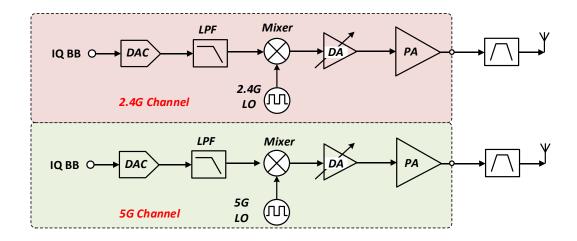

#### 2.3 Dual-band WLAN Transmitter

Figure 2.9. Diagram of the dual-band transmitter architecture with shared baseband.

Figure 2.10. Diagram of the dual-band transmitter architecture enabling concurrent dual-band operation.

Currently, WLAN standards have two operation bands: 2.4-GHz ISM band and 5-GHz band. Due to the 2.4-GHz ISM band is shared by WLAN, Bluetooth, Zigbee and

other more applications, it is very crowded in the 2.4-GHz band. Sometimes when other applications occupy the 2.4-GHz band, it is difficult for WLAN to transmit and receive data with a high data rate in the 2.4-GHz band. On the other hand, the existing 5-GHz WLAN band (5.18 to 5.825 GHz) has more available channels and has a flexibility in channel bandwidth. It is much less crowded in the 5-GHz band, and wider bandwidth can be utilized to improve data rate. Therefore, as the main standard of WLAN, 802.11ac operates in the 5-GHz band and is backward compatible with the previous 802.11a. While, since the path loss of link is smaller in the 2.4-GHz band than in the 5-GHz band, the transceivers operating in the 5-GHz band will consume more power to achieve the same coverage range, compared with the transceiver operating in the 2.4-GHz band. Thus, although the 2.4-GHz band may not provide enough bandwidth for WLAN devices in some cases, the function of the 2.4-GHz operation is still necessary for low-to-moderate applications and 2.4-GHz WLAN standards 802.11b/g are still commonly used today.

In practice, most commercial WLAN transceivers are designed to have a 2.4/5-GHz dual-band operation [10]-[17], such that the transceivers can support all existing WLAN standards (802.11a/b/g/n/ac). In some scenarios, the WLAN devices have to toggle from the 2.4-GHz operation to the 5-GHz operation if there is not enough available bandwidth in the 2.4-GHz band, or have to toggle from the 5-GHz operation to the 2.4-GHz operation when the required data rate is no longer high. The dual-band WLAN transceivers proposed in [10]-[17] can meet the requirement of the switching operation modes. Since this thesis focuses on transmitter design, the receiver part of the RF transceivers in [10]-[17] are not involved. In these dual-band transceivers, the transmitter parts use the similar architecture, and the block diagram of the dual-band transmitter architecture is shown in Figure 2.9. In the architecture, there are two separated RF channels including direct up-conversion mixer, driver and power amplifier. A single

analog baseband block including DACs and low pass filters is shared between the 2.4-GHz and 5-GHz channels to reduce the complicity and chip area. At one time, only one RF channel works, and the operation mode can be switched between the 2.4-GHz and 5-GHz modes.

In [18]-[20], another transmitter architecture is presented to support the 2.4-GHz and 5-GHz simultaneous operation, as shown in Figure 2.10. Different from the architecture shown in Figure 2.9, this architecture has two fully separated channels, and each RF channel has its own baseband block. The main benefit of this dual-band transmitter architecture is simultaneous dual-band operation capability, which enables full throughput by utilizing the bandwidths both in the 2.4-GHz and 5-GHz bands. On the other hand, the complexity of this architecture is significantly increased due to the two baseband signal processing units and the baseband analog blocks required in the whole system.

In CMOS implementation, the chip size of the RF transceiver is dominated by the passive components used in the matching networks including inductors and transformers. In the transmitter, the inter-stage matching networks between the mixer and the driver, and between the driver and the PA are required. Besides, the output matching network for the PA is also required. In general, the inductors and transformers are utilized in the inter-stage and output matching networks, which occupy most of the chip area. Therefore, the two architectures shown in Figure 2.9 and Figure 2.10 both have a large size due to the two separated RF channels used. For the architecture in Figure 2.9, if two RF channels can be merged into one RF channel with a dual-band function, the number of the matching networks will be the half and the chip size will be considerably reduced. In terms of low cost, a single transmitter supporting reconfigurable 2.4/5-GHz dual-band operation is superior to the dual-band architecture in Figure 2.9 using two transmitter

channels. Currently, no reconfigurable dual-band transmitter using only one transmitting channel is available in academia and industry. Therefore, one part of the effort in this thesis is to design such a reconfigurable 2.4/5-GHz dual-band transmitter front-end for WLAN 802.11ax application.

## Chapter 3

# Crosstalk and VCO pulling

To support carrier aggregation, more carrier signals have to be processed concurrently in one CMOS transceiver chip. Due to the low-resistance silicon substrate, coupling or leakage between different signal processing paths is unavoidable, leading to two main problems, namely crosstalk and VCO pulling. Besides, in CMOS transceiver, since the physical spacing between signal processing paths is very small and is even in um-level, the electromagnetic radiation is another major contributor to the near-filed coupling and leakage, and the coupling strength caused by the electromagnetic radiation is dependent with the operating frequency, which will be discussed in the following parts of this chapter. Among the transmitter architectures for carrier aggregation introduced in Chapter 2, except for the architecture with carriers aggregated in digital domain, all other architectures have the intrinsic problem of crosstalk and VCO pulling in CMOS implementation. Practically speaking, the coupling or leakage between signal processing paths should be minimized to reduce the effect of crosstalk and VCO pulling on the transceiver's performance, which is the main consideration in designing a transceiver supporting carrier aggregation, especially for 5-GHz 802.11ax with wide bandwidth and high order modulation scheme. In this thesis, we only focus on transmitter design for carrier aggregation, and how the performance of transmitter is affected by crosstalk and VCO pulling will be investigated in this chapter. While, the effect of crosstalk and VCO pulling on receiver is not involved and discussed in this thesis. In additional, to explore the strength of interaction between two signal processing channels in practical layout, the coupling factor between active devices and between the passive signal traces are simulated in this chapter.

## 3.1 Crosstalk

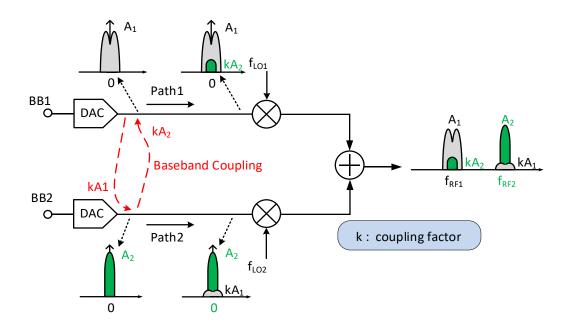

Figure 3.1. Effect of crosstalk caused by baseband coupling on SNR.

Figure 3.2. Effect of crosstalk caused by LO coupling on SNR.

In general, crosstalk is mainly caused by the baseband coupling and the LO coupling [8], [9], and crosstalk has a significant impact on the signal-to-noise ratio (SNR) of the transmitted signals. Figure 3.1 demonstrates the effect of the baseband coupling on the transmitted signals. In Figure 3.1, two RF transmitting paths both use a direct-conversion

mixer, and two carriers are combined after the mixer. The coupling signal from BB1 falls on top of BB2 and vice versa. As a result, before injected into the mixer, both the signals BB1 and BB2 are interfered by the coupling signal from the other path. Consequently, the SNR of each baseband signal is degraded. In Figure 3.1, the bandwidth of the baseband signal BB1 is assumed to be larger than that of the signal BB2, so only the SNR of the signal BB1 is affected by the interference. Whereas, as for the signal BB2, not only the SNR is degraded, but also the ACLR is degraded. However, in practical carrier aggregation scenario, all carriers have the same bandwidth; thus, in this thesis, the degradation of the ACLR caused by the baseband coupling or the LO coupling is only demonstrated in figures, but not considered in the further analysis.

The effect of crosstalk caused by the LO coupling in direct-conversion transmitter is demonstrated in Figure 3.2. LO signal couples from one path to the other, and there are two LO signals for the mixer in each path. As a result, there are two mixing products of the mixer, and one is the desired RF signal, and the other interference exists at the same frequency of the desired signal in the other path. After combination, the SNR of each transmitting signal is degraded by the resulted interferences. Hence, the LO coupling has the similar impact on the SNR of the RF signals as the baseband coupling does.

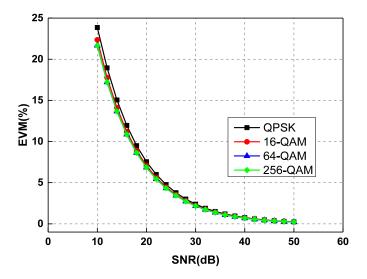

As demonstrated in above Figure 3.1 and Figure 3.2, crosstalk have an impact on the SNR, and the degradation of the SNR then affects the EVM performance, which is the most widely adopted standard in the industry to quantify the performance of the signal in the transmitter. Regardless of the impairments of transmitter, such as AM-AM and AM-PM distortion of PA, IQ mismatch, DC offset and phase noise of LO, EVM is a function of SNR [38], expressed by

$$EVM = 100\% \cdot \sqrt{\frac{\sqrt{M} + 1}{3 \cdot SNR \cdot (\sqrt{M} - 1)}}$$

(3.1)

where *M* is the order of modulation. A calculation has been performed to show how EVM is affect by SNR for four modulations, QPSK, 16-QAM, 64-QAM and 256-QAM, and the calculated results are shown in Figure 3.3. Seen from Figure 3.3, when SNR is 50 dB, the values of EVM are nearly 0.3% for all four modulations.

Figure 3.3. EVM versus SNR.

While, in practice, EVM<sub>rms,avg</sub> is measured instead of EVM through a vector signal analyzer. As an alternative definition of EVM, EVM<sub>rms,avg</sub> normalizes the error vector to the average symbol energy [39], [39], only depending on SNR, expressed by

$$EVM_{rms,avg} = 100\% \cdot \sqrt{\frac{1}{SNR}} \cdot \tag{3.2}$$

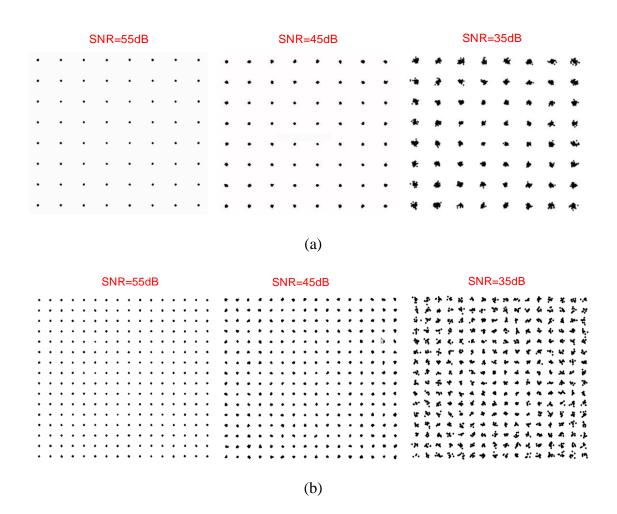

In the following part of this thesis, EVM refers to EVM<sub>rms,avg</sub>. In order to explore the impact of SNR on EVM for practical WLAN signals, a simulation has been performed to calculate the constellation and EVM using 802.11ac signals with different SNRs. Since 802.11ac signal has the same modulation as 802.11ax signal does, 802.11ac signal can be an alternative of 802.11ax signal when simulating the constellation and EVM. In the simulation, 80-MHz 802.11ac signals with 64-QAM and 256-QAM modulation are used. The simulated constellations versus different SNRs are illustrated in Figure 3.4. From

Figure 3.1. Simulated constellation for 802.11ac signals. (a) 64-QAM. (b) 256-QAM.

Figure 3.2. Simulated EVM<sub>rms,avg</sub> versus SNR.

the simulated results, when SNR is higher, the demodulated data points are more concentrated to the ideal points in the constellation, and better EVM can be achieved.

Figure 3.5 plots the simulated EVM with respect to SNR. In Figure 3.5, the EVM curves for 64-QAM and 256-QAM almost overlap, showing that EVM (EVM<sub>rms,avg</sub>) is independent of the modulation, which is in accordance with (3.2). In addition, the simulated EVM for 802.11ac signals is slightly higher than that predicted from (3.2), but has the same tendency with SNR. From Figure 3.5, the 50-dB SNR results in the EVM of 0.42%. Considering the stringent EVM requirement of 2.5% (-32 dB) for 256-QAM modulation, the deterioration of the EVM by 0.42% has a severe impact on system performance, which will intensify the noise and linearity requirement for the circuit blocks in the transmitter. Therefore, for the 802.11ax system employing 256-QAM and 1024-QAM modulation, an SNR of better than 50 dB is required. While, for LTE-Advance, the EVM requirement for 16-QAM is 12.5%, and thus 30 dB SNR is high enough to meet such loose EVM requirement. Compared with LTE-A, it deserves much effort to increase the isolation between signal paths to achieve a high SNR for the 802.11ax system operating in the carrier aggregation mode.

We have thus far analysed the impact of SNR on EVM, and now turn to study how SNR is affected by the coupling in layout. In Figure 3.1 and Figure 3.2, the SNR of the transmitting signal in Path1 can be simply defined as follows:

$$SNR_dB = 20\log\frac{A_1}{kA_2}$$

(3.3)

where k is the coupling factor between the signal paths, which is dependent on the operating frequency, the length of the signal paths and spacing between the paths. Assuming the transmitting signals in Path1 and Path2 have the same amplitude and bandwidth,

$$SNR_dB = -20\log k. \tag{3.4}$$

Then,

$$EVM_{rms,avg} = 100\% \cdot \sqrt{\frac{1}{SNR}} = 100\% \cdot \sqrt{k}$$

(3.5)

Thus, without considering the amplitude of the transmitting signals, EVM is mainly dependent with the coupling factor between the signal paths, and crosstalk is a dominant contributor to EVM. As analysed in above, for 802.11ax system, to ensure a good EVM performance, the SNR should be above 50 dB, which means the coupling factor is required to be lower than 50 dB (0.0032).

## 3.2 VCO pulling

Figure 3.6. Coupling between two VCOs.

In transmitter supporting multiple carriers, two or more PLLs are integrated on the same substrate and operate concurrently. Due to the coupling between VCOs through the substrate and electromagnetic radiation, as shown in Figure 3.6, the oscillators undergo a mutual interaction between each other, resulting in unwanted sidebands or spurs at the oscillators' output, which is called VCO pulling [5]-[7], [40], [41]. These resulted

Figure 3.3. VCO pulling between PLLs.

Figure 3.4. Effect of VCO pulling on transmitter for carrier aggregation.

sidebands or spurs are at an offset equal to the frequency spacing between the PLLs' outputs, as shown in Figure 3.7. As a result, for the mixer in each path, there are three LO signals, one desired LO, and two interferences caused by VCO pulling. Then, these three LO signals will produce three RF output signals after the mixer, one desired RF output and two interferences, as illustrated in Figure 3.8. Due to these interferences, the

requirement of emission mask for 5-GHz 802.11ax may not be satisfied. For contiguous carrier aggregation, these two resulted inferences will be located in the lower and upper adjacent channels of the desired carriers, thus ACLR will degrade, which is the worst case for the effect of VCO pulling on transmitter's output spectrums.

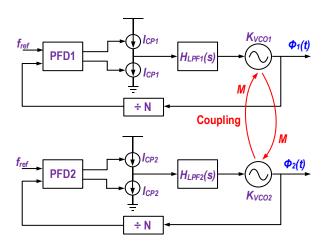

Figure 3.9. Model of VCO pulling between two PLLs.

To evaluate the effect of VCO pulling, it is critical to estimate the magnitude of the sidebands. In Figure 3.9, the output phases of the PLLs in time domain,  $\Phi_I(t)$  and  $\Phi_2(t)$  can be expressed as [7]

$$\Phi_1(t) = \omega_1 t + \theta_1 + \Delta \Phi_1(t) \tag{3.6}$$

$$\Phi_2(t) = \omega_2 t + \theta_2 + \Delta \Phi_2(t) \tag{3.7}$$

where  $\omega_1$  and  $\omega_2$  are the desired angular frequencies of the two PLLs' outputs,  $\theta_1$  and  $\theta_2$  are dictated by the phases of the reference clocks as well as the delays caused by the charge-pump and divider, and  $\Delta\Phi_1(t)$  and  $\Delta\Phi_2(t)$  represent the phase perturbations caused by VCO pulling, respectively.

The differential forms of (3.6) and (3.7) are as follows:

$$\frac{d\Phi_1(t)}{dt} = \omega_1 + \frac{d\Delta\Phi_1(t)}{dt}$$

(3.8)

$$\frac{d\Phi_2(t)}{dt} = \omega_2 + \frac{d\Delta\Phi_2(t)}{dt}.$$

(3.9)

$\frac{d\Delta\Phi_1(t)}{dt}$  and  $\frac{d\Delta\Phi_2(t)}{dt}$  can be derived as:

$$\frac{d\Delta\Phi_{1}(t)}{dt} = -K_{VCO1} \frac{I_{CP1}}{2\pi} \frac{\Delta\Phi_{1}(t)}{N_{1}} * h_{LPF1}(t) + \frac{k\omega_{1}}{2Q_{1}} \sin(\Delta\omega t + \theta_{2} - \theta_{1})$$

(3.10)

$$\frac{d\Delta\Phi_{2}(t)}{dt} = -K_{VCO2}\frac{I_{CP2}}{2\pi}\frac{\Delta\Phi_{2}(t)}{N_{2}}*h_{LPF2}(t) - \frac{k\omega_{2}}{2Q_{2}}\sin\left(\Delta\omega t + \theta_{2} - \theta_{1}\right) \quad (3.11)$$

where  $\Delta\omega = \omega_2 - \omega_I$ ,  $K_{VCOI}$  and  $K_{VCO2}$  are the gains of the VCOs,  $Q_I$  and  $Q_2$  are the LC tank's quality factors in the VCOs, k is the coupling factor between the VCOs,  $I_{CPI}$  and  $I_{CP2}$  are the magnitudes of the charge-pump currents,  $N_I$  and  $N_2$  are the division ratios of the dividers,  $h_{LPFI}(t)$  and  $h_{LPF2}(t)$  are the transfer functions of the loop filters in the two PLLs, respectively. The closed form solutions of (3.10) and (3.11) are derived by the following equations:

$$\Delta\Phi_{1}(t) = \frac{-jk\omega_{1}e^{j(\theta_{2}-\theta_{1})}}{2Q_{1}} \times \frac{e^{st}}{s + \frac{I_{CP1}}{2\pi} \frac{K_{VCO1}}{N_{1}} H_{LPF1}(s)} \bigg|_{s=j\Delta\omega}$$

(3.12)

$$\Delta\Phi_{2}(t) = \frac{jk\omega_{2}e^{j(\theta_{2}-\theta_{1})}}{2Q_{2}} \times \frac{e^{st}}{s + \frac{I_{CP2}}{2\pi} \frac{K_{VCO2}}{N_{2}} H_{LPF2}(s)}$$

(3.13)

For simplicity, assuming the two PLLs have the same parameters, the sidebands' magnitude can be approximately predicted by

$$M_{SB}(\Delta\omega) = \frac{k\omega_0}{2Q} \left| \frac{1}{s + \frac{I_{CP}}{2\pi} \frac{K_{VCO}}{N} H_{LPF}(s)} \right|_{s = i\Delta\omega}$$

(3.14)

According to (3.14), increasing the quality factor Q of the LC tank can reduce the VCO pulling effect. However, in a bulk CMOS technology, the quality factor of the inductor cannot be very high. Thus, it is not feasible to alleviate VCO pulling mainly through

increasing the quality factor of the VCOs. In addition, reducing the coupling factor between two VCOs can effectively lower the unwanted sidebands, which can be done by increasing the physical spacing between two VCOs, placing ground shielding around the *LC* tank and using separated DC supply and ground for each VCO [7], [8]. Moreover, the sidebands' magnitude becomes lower with the increase of the frequency spacing between the VCOs.

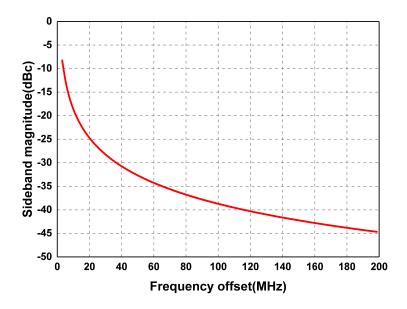

To roughly evaluate the sidebands' magnitude for practical mutual pulling PLLs, a calculation has been performed according to (3.14), based on a reasonable assumption of the PLL parameters. The parameters of the PLLs are assumed:  $K_{VCO} = 50 \text{ MHz/V}$ ,  $I_{CP} = 50 \text{ }\mu\text{A}$ , N = 275,  $f_0 = 11 \text{ GHz}$ , Q = 15. The parameters of the loop filter in the PLLs are assumed:  $C_I = 20 \text{ pF}$ ,  $R_I = 150 \text{ k}\Omega$ ,  $R_2 = 1.5 \text{ pF}$ , and its' transfer function is

$$H_{LPF}(s) = \frac{1 + sC_1R_1}{s^2C_1C_1R_1 + s(C_1 + C_2)}.$$

(3.15)

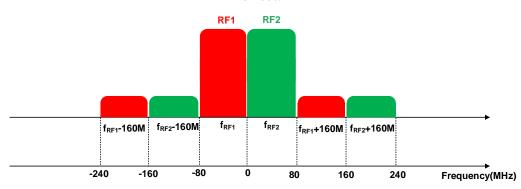

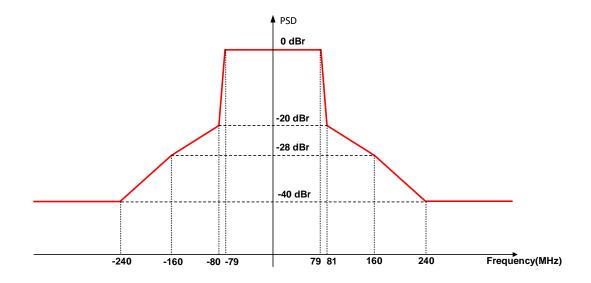

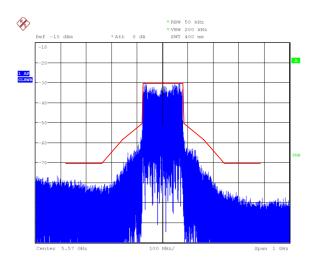

With these assumed parameters, the -3-dB closed loop bandwidth of the PLL is 405 kHz, and the loop phase margin is  $60.3^{\circ}$ . The coupling factor between the two VCOs is assumed to be -50 dB, which is also a reasonable value for practical cases. The calculated result is plotted in Figure 3.10 for  $\Delta f$  varying from 1 MHz to 200 MHz. Obviously, increasing the frequency spacing between the VCOs can significantly reduce the sideband magnitude. For 80 + 80 MHz contiguous carrier aggregation in the 802.11ax system, the sidebands' magnitude is -42.8 dB from Figure 3.10. Considering the effect of VCO pulling, the spectrum for 80 + 80 MHz contiguous carrier aggregation is illustrated in Figure 3.11. Referring to the spectral mask for 80 + 80 MHz contiguous carrier aggregation shown in Figure 3.12, -42.8-dB sideband can satisfy the spectral mask, though, there is almost no margin of the noise and non-linearity for circuits in transmitter. To ensure good ACLR performance, the isolation between the VCOs has to be lower

than -50 dB, requiring a large physical isolation in practical layout.

Figure 3.10. Simulated magnitude of sideband for pulling PLLs' output with frequency offset.

Figure 3.11. Spectrum for 80 + 80 MHz contiguous carrier aggregation.

Figure 3.12. Spectral mask for 80 + 80 MHz contiguous carrier aggregation.

In some practical cases where a large physical isolation cannot be achieved, increasing the frequency spacing between two VCOs is an effective approach to solve the problem of VCO pulling. In [8], the division ratio of the divider in one path is the double of the division ratio of the divider in the other path. Accordingly, one VCO operates at twice the operating frequency of the VCO in the other path. In this way, a large frequency separation can be obtained when supporting contiguous carrier aggregation. Although the approach used in [5] to achieve a large frequency separation is feasible for LTE-A with the operating frequency below 3 GHz, it is not suitable for 802.11ax in the 5-GHz WLAN band of 5.17-to-5.835 GHz. Such approach will require a PLL with the frequency as high as 23.34 GHz, which drastically intensifies the PLL's design complexity. Besides, the power consumption of the PLL and divider operating in such high frequency from 20.68 to 23.34 GHz will be higher.

### 3.3 Coupling factor between two channels in layout

#### 3.3.1 Coupling factor between two active devices

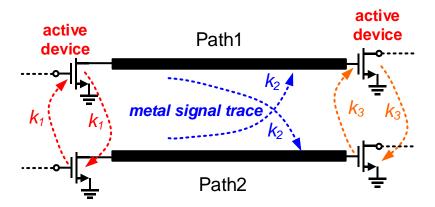

Figure 3.13. Coupling between active devices and between metal signal traces.

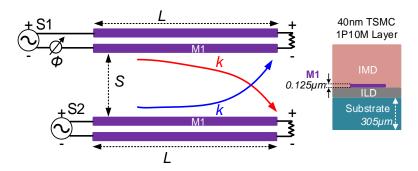

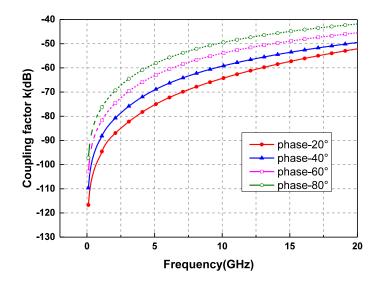

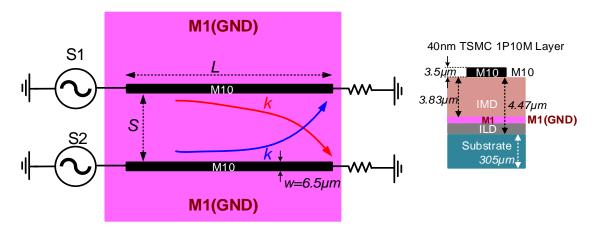

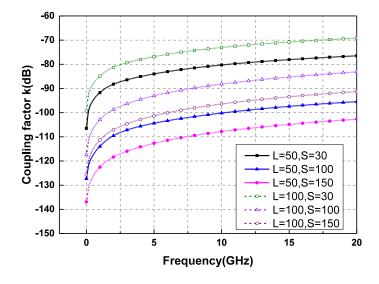

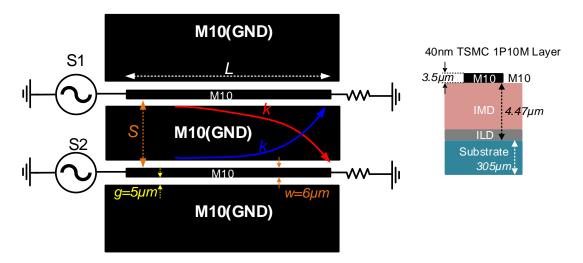

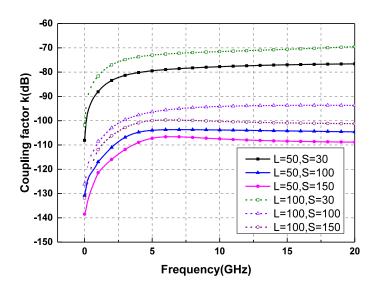

To characterize the coupling factor in practical layout, some physical models are created to simulate the coupling factor in TSMC 40-nm CMOS 1P10M technology. The coupling exists between the devices and between the metal signal traces in practical

layout, as shown in Figure 3.13. Thus, the coupling factor is categorized into two types to investigate: the coupling factor between the active devices and the coupling factor between the metal signal traces.

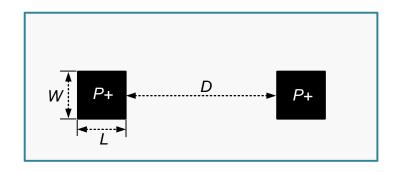

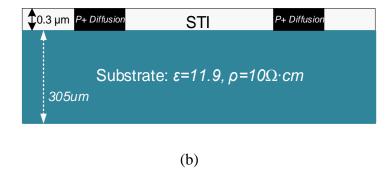

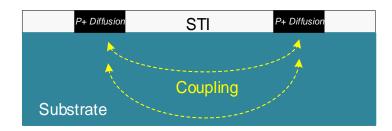

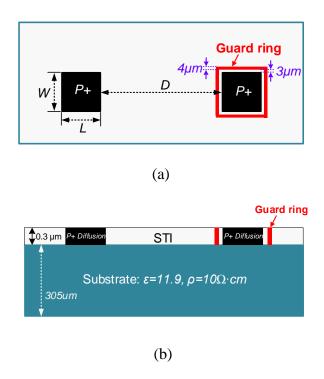

First of all, we investigate the coupling factor between the two actives with different sizes and spacings [42]-[47]. In practice, one transistor may have a large number of fingers, then the width or length of one transistor's layout may reach 100 µm or even become larger than 100 µm, thus it is not feasible to accurately model the transistors in simulating the coupling factor. On the other hand, if the coupling exists between the two RF channels through the active devices, all the transistors used in the two channels will undergo the coupling. Take the LO coupling for example, all the transistors used in the mixers and LO generation circuits will undergo the coupling. In general, it is not easy to simulate the coupling factor for a practical transmitter layout accurately. For simplicity, the active devices are modelled as a rectangle shape with P+ diffusion in the simulation, and Figure 3.14 demonstrates the model of the two active devices in TSMC 40-nm CMOS technology. In this technology, the thickness of the substrate is 305 µm, and the relative dielectric constant and resistivity of Si substrate are 11.9 and 10  $\Omega$ ·cm, respectively. Shallow trench isolation (STI) is used to prevent the electric current leakage and increase the isolation between the adjacent active devices in horizontal direction. Although STI can provide isolation in some degree, the coupling through the substrate underneath the active devices is still unavoidable, shown in Figure 3.15.

Figure 3.14. Model of two active devices in TSMC 40-nm CMOS technology. (a) Top view. (b) Cross-sectional view.

Figure 3.15. Coupling through substrate between active devices.

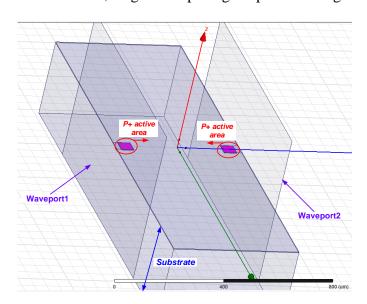

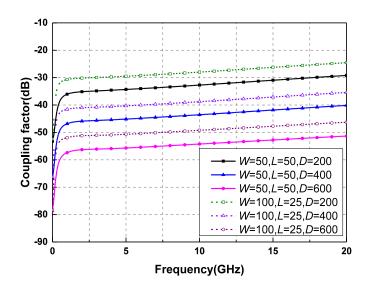

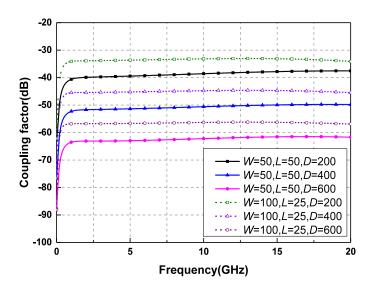

The simulation has been performed in the EM simulation software HFSS V15. The screenshot of the simulation model in HFSS is shown Figure 3.16. The solution type is 'Driven Terminal', and the excitation is 'waveport'. The simulated coupling factors for some cases with different width, length and spacing are plotted in Figure 3.17. Seen from

Figure 3.16. Simulation model in HFSS.

Figure 3.17. Simulated coupling factor between two active devices.

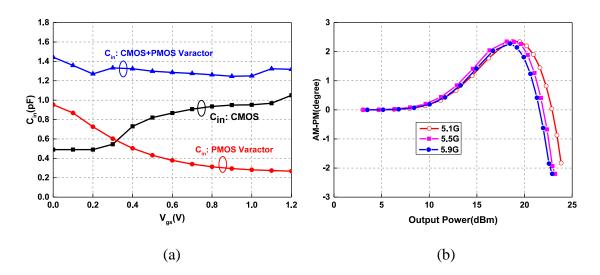

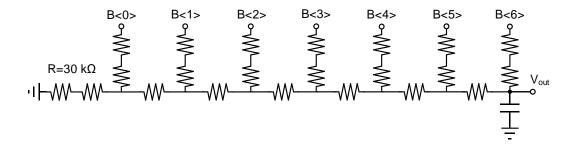

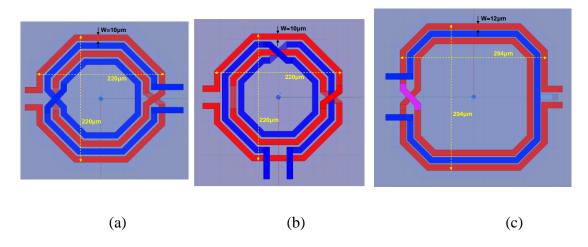

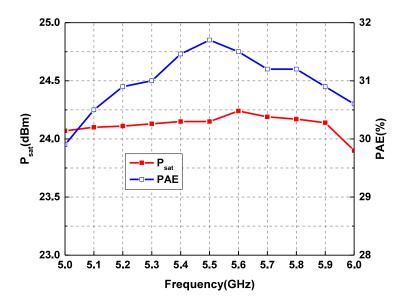

Figure 3.17, the coupling factor is dependent on the area of the active device and the spacing between the devices. Besides, the coupling factor becomes a slightly higher as the frequency increases, showing the portion of the coupling caused by the near field electromagnetic radiation increases when the frequency becomes higher. Obviously, increasing the physical spacing between the active devices is an effective approach to reducing the coupling. For the active device with a length of 25 µm and a width of 100 µm, the physical spacing is required to be larger than 400 µm to ensure the coupling factor below -50 dB. If accounting for the active devices in the whole transmitter path, the total equivalent size of all active devices undergoing coupling will become quite large. Consequently, in order to guarantee low coupling to achieve a good EVM performance, the physical isolation may be required to be larger than hundreds of micrometres, when only considering the coupling between active devices. While, the spacing of hundreds of micrometres may not be realizable in some practical cases due to the constraint of layout.