# This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Exploring low complexity embedded architectures for deep neural networks

Chatterjee, Soham

2021

Chatterjee, S. (2021). Exploring low complexity embedded architectures for deep neural networks. Master's thesis, Nanyang Technological University, Singapore. https://hdl.handle.net/10356/150553

https://hdl.handle.net/10356/150553

https://doi.org/10.32657/10356/150553

This work is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License (CC BY-NC 4.0).

Downloaded on 09 Apr 2024 11:41:05 SGT

# Exploring Low Complexity Embedded Architectures for Deep Neural Networks

#### Soham Chatterjee

#### School of Electrical & Electronic Engineering

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirements for the degree of Master of Engineering

### Statement of Originality

I hereby certify that the work embodied in this thesis is the result of original research, is free of plagiarised materials, and has not been submitted for a higher degree to any other University or Institution.

| 16-04-21 | Schon Chatteries |

|----------|------------------|

|          |                  |

| Date     | Soham Chatteriee |

#### Supervisor Declaration Statement

I have reviewed the content and presentation style of this thesis and declare it is free of plagiarism and of sufficient grammatical clarity to be examined. To the best of my knowledge, the research and writing are those of the candidate except as acknowledged in the Author Attribution Statement. I confirm that the investigations were conducted in accord with the ethics policies and integrity standards of Nanyang Technological University and that the research data are presented honestly and without prejudice.

| 16-04-21 | <u> Aeindan Ban</u> |

|----------|---------------------|

|          |                     |

| Date     | Prof. Arindam Basu  |

#### Authorship Attribution Statement

This thesis contains material from 3 papers published in the following peer-reviewed journal(s) / from papers accepted at conferences in which I am listed as an author.

Chapter 3 is published as D. Singla, S. Chatterjee, L. Ramapantulu, A. Ussa, B. Ramesh, A. Basu, "HyNNA: Improved Performance for Neuromorphic Vision Sensor based Surveillance using Hybrid Neural Network Architecture," 2020 IEEE International Symposium on Circuits and Systems Conference (ISCAS), Sevilla, Spain 2020.

The contributions of the co-authors are as follows:

- A/Prof Arindam Basu provided the initial project direction and edited the manuscript drafts.

- Deepak Singla worked on data preprocessing and implemented the different RoI proposal schemes.

- I trained the different neural network models and wrote scripts to calculate the memory and FLOPs of the models. I also wrote the sections related to neural network architecture, training, performance and results in the manuscript.

- Dr. Lavanya Ramapantulu prepared the manuscript draft and guided me on how to calculate the model memory and FLOPs.

- Bharath Ramesh, Andres Ussa and A/Prof Arindam Basu reviewed and finalised the manuscript draft.

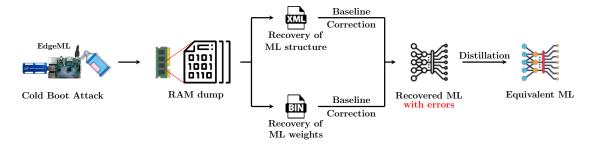

Chapter 4 contains material submitted for publication as S. Chatterjee, YS Won, D. Jap, S. Bhasin, A. Basu, "DeepFreeze: Cold Boot Attack and Model Recovery on Commercial EdgeML Device", **submitted to** 2021 Design Automation Conference (DAC), San Francisco, United States of America 2021.

The contributions of the co-authors are as follows:

- A/Prof Arindam Basu and Dr. Shivam Bhasin provided the initial project direction and edited the manuscript drafts.

- I performed the recovery of model architecture and weights from the RAM dump as well performed Knowledge Distillation training to perform model accuracy and weight recovery. I also prepared parts of the manuscript related to the same.

- Dr. Yoo-Seung Won performed the Cold Boot Attack and RAM dump as well as prepared parts of the manuscript related to the same.

• Dr. Dirmanto Jap prepared and reviewed the manuscript.

Chapter 5 partly contains material published as YS Won, S. Chatterjee, D. Jap, S. Bhasin, A. Basu, "Time to Leak: Cross-Device Timing Attack On Edge Deep Learning Accelerator," 2021 International Conference on Electronics, Information, and Communication (ICEIC), Jeju Shinhwa World, Republic of Korea 2021.

The contributions of the co-authors are as follows:

- Dr. Shivam Bhasin provided the initial project direction, co-designed the study and reviewed the manuscript

- A/Prof. Arindam Basu reviewed the manuscript.

- I wrote the scripts to run the experiment on different hardware. I also wrote parts of the manuscript related to OpenVINO and Neural Compute Stick 2.

- Dr. Yoo-Seung Won performed the experiments on different hardware and did the analysis of the results. He also prepared the manuscript draft.

- Dr. Dirmanto Jap prepared and reviewed the manuscript.

| 16-04-21 | School Chatterijee |

|----------|--------------------|

|          |                    |

| Date     | Soham Chatteriee   |

# Acknowledgements

I wish to express my greatest gratitude to my advisor Prof. Arindam Basu for guiding me during my M.Eng. journey. I would also like to thank Prof. Shivam Bhasin for his mentorship and guidance. Further, this work would not have had been possible without the help and guidance I received from my peers at VIRTUS Lab: Deepak Singla, Lavanya Ramapantulu, Vivek Mohan and Charles Zhang Lei and at PACE Lab: Yoo-Seung Won and Dirmanto Jap.

I would also like to thank my parents (Biswajit and Bul Bul), my brother (Rohan) for all the support they have provided during the duration of my course.

Soham Chatterjee, April 2021

"Ever Tried. Ever Failed. No Matter. Try Again. Fail Again. Fail Better."

— Samuel Beckett

#### Abstract

Deep neural networks have shown significant improvements in computer vision applications over the last few years. Performance improvements have been brought about mostly by using pre-trained models like Inception-v4, ResNet-152, and VGG 19. However, these improvements have been accompanied by an increase in the size and computational complexity of the models [1]. This makes it difficult to deploy such models in energy-constrained mobile applications which have become ever crucial with the advent of the Internet of Things (IoT).

This is especially problematic in a battery-powered IoT system, where executing complex neural networks can consume a lot of energy [2]. Hence, some methods to reduce this complexity in software, like using depthwise separable convolutions [3] and quantization [4], have been proposed. Also, a very different computing paradigm of spiking neural networks (SNN) has been introduced as a method to introduce a parameterizable tradeoff between accuracy and classification energy [5], [6]. The security of such edge deployed neural networks is also a matter of concern since the IoT devices are easily accessible to hackers.

In this work, a study of the effect of using depthwise separable convolutions and Dynamic Fixed Point (DFP) weight quantization [7] on both model accuracy and complexity is done for a DNN used for classifying traffic images captured by a neuromorphic vision sensor. Initial results show that the DFP weight quantization can significantly reduce the computational complexity of neural networks with less than a 2% drop in accuracy.

Finally, the vulnerability of neural networks to side-channel [8] and cold boot attacks [9] is also being studied. To do this, trained models are deployed to edge devices like the Neural Compute Stick, EdgeTPU DevBoard, and the EdgeTPU accelerator and then attacked to retrieve the model weights, architecture and other parameters. We show that using cold boot attacks, it is possible to recover the model architecture and weights, as well as the original model accuracy. Further,

we show that with side-channel attacks, it is possible to isolate and identify the execution of individual neurons in a model. Since quantized networks have fewer and smaller weight values, they should be easier to attack. On the other hand, larger neural networks with complex architectures and dataflows should be comparatively safer from side-channel attacks.

# Contents

| A  | ckno               | wledgements                                     | 5              |

|----|--------------------|-------------------------------------------------|----------------|

| A  | bstra              | ct                                              | 7              |

| Li | $\mathbf{st}$ of   | Figures                                         | 12             |

| Li | st of              | Tables                                          | 15             |

| A  | bbre               | viations                                        | 16             |

| 1  | Intr<br>1.1<br>1.2 | Motivation and Background                       | 18<br>18<br>21 |

| 2  | Lite               | erature Review                                  | 22             |

| _  | 2.1                | IoT and Edge Computing                          | 22             |

|    | $\frac{2.1}{2.2}$  | Adapting Neural Networks for Edge Computing     | 24             |

|    | 2.2                | 2.2.1 Depthwise Separable Convolutions          | 24             |

|    |                    | 2.2.2 Pruning                                   | 26             |

|    |                    | 2.2.3 Quantization                              | 27             |

|    |                    | 2.2.4 Knowledge Distillation                    | 29             |

|    | 2.3                | Neural Network Accelerators                     | 31             |

|    |                    | 2.3.1 Neural Compute Stick                      | 31             |

|    |                    | 2.3.2 EdgeTPU Board                             | 31             |

|    | 2.4                | Neuromorphic Vision Sensors                     | 33             |

|    | 2.5                | Security and Privacy of Edge Computing Hardware | 35             |

|    |                    | 2.5.1 Electromagnetic Side-Channel Attacks      | 36             |

|    |                    | 2.5.2 Timing Side-Channel Attacks               | 39             |

|    |                    | 2.5.3 Cold Boot Attacks                         | 40             |

|    | 2.6                | Conclusion                                      | 42             |

| 3  | Neı                | romorphic Traffic Data Classification           | 43             |

CONTENTS 10

|   | 3.1  | Dataset Overview                                       |

|---|------|--------------------------------------------------------|

|   | 3.2  | Data Collection and Preparation                        |

|   | J    | 3.2.1 Event Based Image Generation                     |

|   |      | 3.2.2 Region Proposal Algorithms                       |

|   | 3.3  | Model Overview                                         |

|   | 3.4  | Model Training                                         |

|   | 3.5  | Results and Discussion                                 |

|   | 3.6  | Dynamic Fixed Point Quantization                       |

|   |      | 3.6.1 DFP Finetuning                                   |

|   | 3.7  | DFP Results                                            |

|   | 3.8  | Conclusion                                             |

| 4 | Col  | d Boot Attack on Neural Network Accelerators 56        |

|   | 4.1  | Experimental Setup and Threat Model                    |

|   | 4.2  | Cold Boot Attack Procedure                             |

|   |      | 4.2.1 Recovering Model IR Files                        |

|   |      | 4.2.1.1 Recovering Model Architecture 60               |

|   |      | 4.2.1.2 Recovering Model Weights 60                    |

|   |      | 4.2.2 Target Models                                    |

|   |      | 4.2.3 Baseline Accuracy Recovery                       |

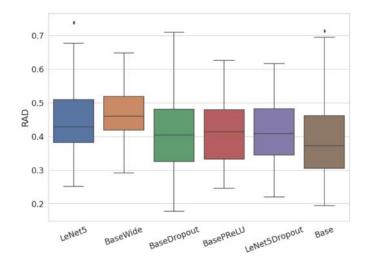

|   | 4.3  | Task Accuracy Recovery Using Knowledge Distillation 63 |

|   | 4.4  | Results and Discussion                                 |

|   |      | 4.4.1 Original Weight Recovery                         |

|   |      | 4.4.2 Transfer Learning Scenario                       |

|   | 4.5  | Challenges and Mitigation                              |

|   | 4.6  | Conclusion                                             |

| 5 | Side | e-Channel Attacks on Neural Network Accelerators 69    |

|   | 5.1  | Timing Side-Channel Attack                             |

|   |      | 5.1.1 Experimental Setup and Threat Model              |

|   |      | 5.1.2 Attack Procedure                                 |

|   |      | 5.1.3 Results and Mitigation                           |

|   | 5.2  | Electromagnetic Side-Channel Attack                    |

|   |      | 5.2.1 Previous Work                                    |

|   |      | 5.2.2 Threat Model and Hardware Setup                  |

|   |      | 5.2.3 Attack Procedure                                 |

|   |      | 5.2.4 Results                                          |

|   |      | 5.2.5 Challenges and Mitigation                        |

|   | 5.3  | Conclusion                                             |

| 6 | Sun  | nmary and Future Work 84                               |

|   | 6.1  | Summary                                                |

|   | 6.2  | Future Work                                            |

| CONTENTS                        | 11 |

|---------------------------------|----|

| 7 List of Author's Publications | 89 |

| List of Author's Publications   | 90 |

| Bibliography                    | 91 |

# List of Figures

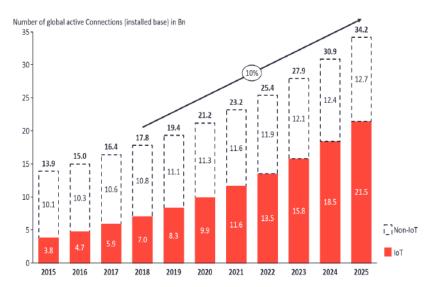

| 1.1  | Growth of IoT devices connected to the internet compared to non-<br>IoT devices. Taken from [10]                                      | 18             |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----------------|

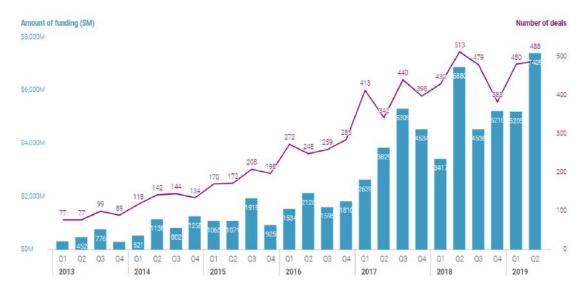

| 1.2  | Funding that AI based companies have received per quarter. Taken from [11]                                                            | 19             |

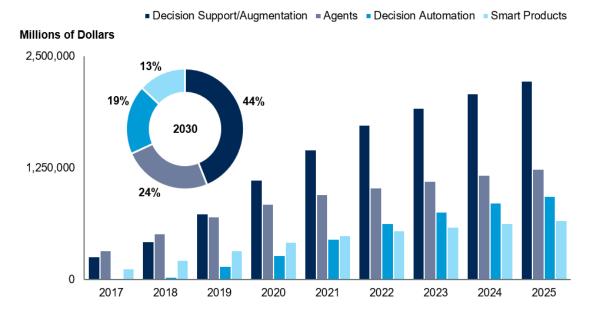

| 1.3  | Business value brought about by AI based products over the next decade. Taken from [12]                                               | 19             |

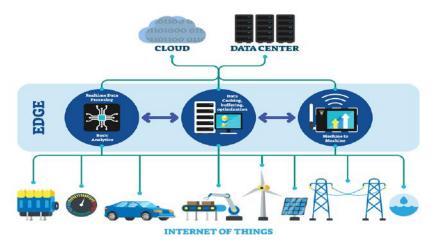

| 1.4  | Edge Computing is a computing paradigm where computation is done on nodes near where the data is generated. Taken from [13]           | 20             |

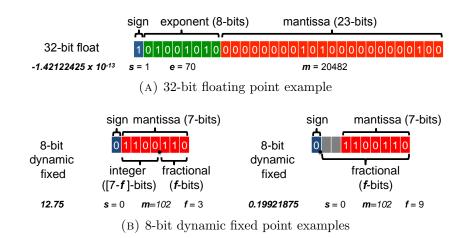

| 2.1  | Various methods of number representations. Taken from [2] (a) 32-bit floating point example                                           | 28<br>28<br>28 |

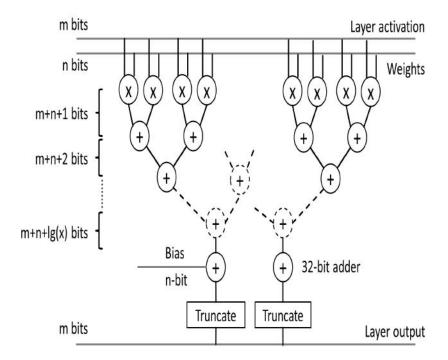

| 2.2  | Data path of quantized convolutional and fully connected layers.  Taken from [7]                                                      | 29             |

| 2.3  | Intel Neural Compute Stick 2. Taken from [14]                                                                                         | 32             |

| 2.4  | EdgeTPU DevBoard. Taken from [15]                                                                                                     | 32             |

| 2.5  | EdgeTPU Accelerator. Taken from [14]                                                                                                  | 33             |

| 2.6  | Experimental Setup for performing side channel attack. Taken from [16]                                                                | 37             |

| 2.7  | Traces generated from probe. Different operations generate different leakage patterns. Taken from [16]                                | 38             |

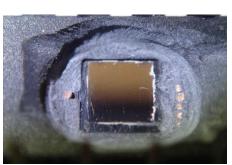

| 2.8  | EdgeTPU Accelerator with its housing and heat sink removed. Attacks are done after removing the housing of the board. This helps      |                |

| 2.9  | to get better reading of the leakages                                                                                                 | 39             |

|      | Taken from [9]                                                                                                                        | 41             |

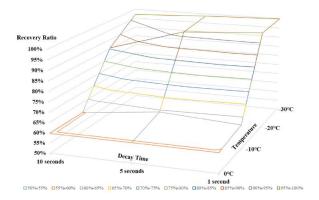

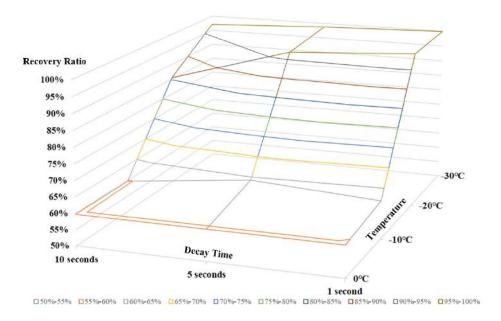

| 2.10 | CBA recovery results for different decay times and freezing temperatures. Recovery is better the higher the temperature and lower the |                |

|      | decay time. Taken from [9]                                                                                                            | 41             |

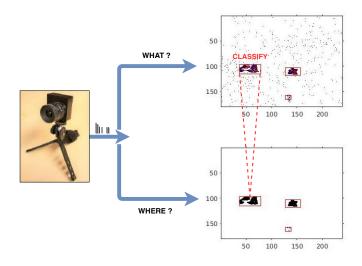

| 3.1  | what-where pathway approach with a DAVIS NVS. Taken from [17]                                                                         | 43             |

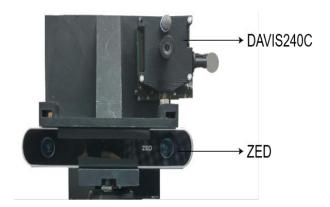

| 3.2  | Camera setup with ZED [18] RGB cameras and DAVIS [19] NVS. Taken from [20]                                                            | 45             |

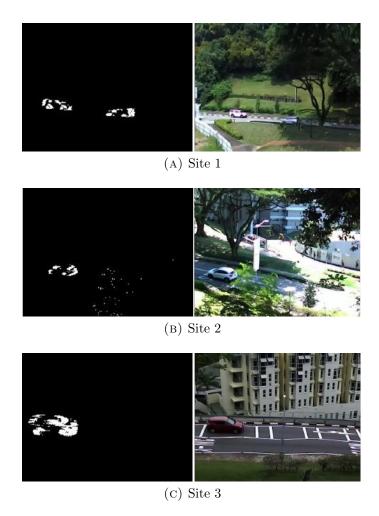

| 3.3  | Examples of EBBI (Left) and RGB Image (Right), recorded at dif-                                                                       |                |

|      | ferent sites. Taken from [20]                                                                                                         | 46             |

|      | (a) Site 1                                                                                                                            | 46             |

|            | (b) Site 2                                                                                                                                                                                                             |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | (c) Site 3                                                                                                                                                                                                             |

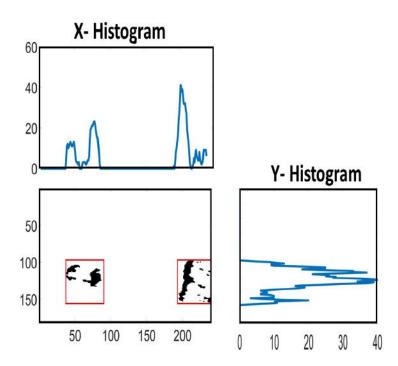

| 3.4        | X and Y histogram projection based region proposals. Taken from [21]                                                                                                                                                   |

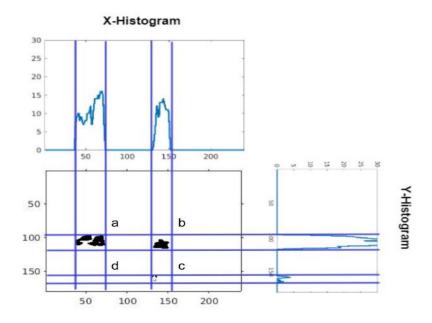

| 3.5        | Disadvantages of HIST RP based region proposal: (a) Normal Region Proposal; (b) (c) Large bounding box due to bigger object; (d) False region proposal. Taken from [21]                                                |

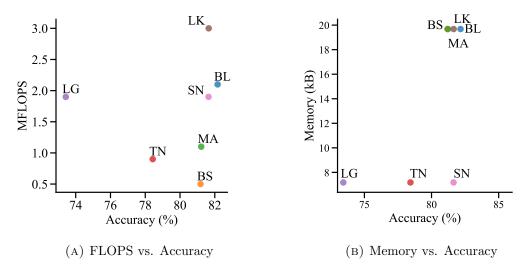

| 3.6        | FLOPS, Memory and Accuracy Trade-offs for CNN Models. Taken from [17]                                                                                                                                                  |

| 4.1        | Cold Boot Attack Procedure on NCS                                                                                                                                                                                      |

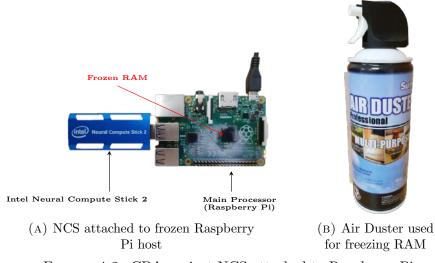

| 4.2        | CBA against NCS attached to Raspberry Pi                                                                                                                                                                               |

| 4.3        | XML script with simulated errors reported by [22]. Incorrect characters are marked in red                                                                                                                              |

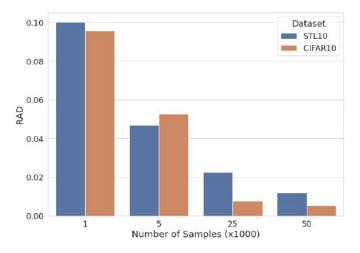

| 4.4        | RAD for 100 corruption iterations for models trained on CIFAR10.<br>Model architectures taken from [23]                                                                                                                |

| 4.5        | RAD for LeNet5 model trained on CIFAR10 for Different Percentages of Training Dataset using D1 Training Paradigm                                                                                                       |

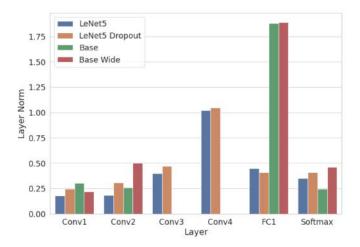

| 4.6<br>4.7 | Layer Norm Recovery Values of CIFAR10 Trained Models Cold Boot Attack recovery ratio at different temperatures and attack decay time. Taken from [9]                                                                   |

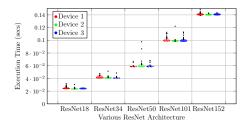

| 5.1        | Execution Time for Various ResNet Architectures using Timing Side-Channel                                                                                                                                              |

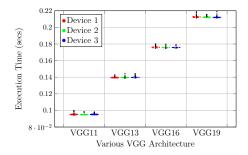

| 5.2        | Execution time for Various VGG Architectures using Timing Side-Channel.                                                                                                                                                |

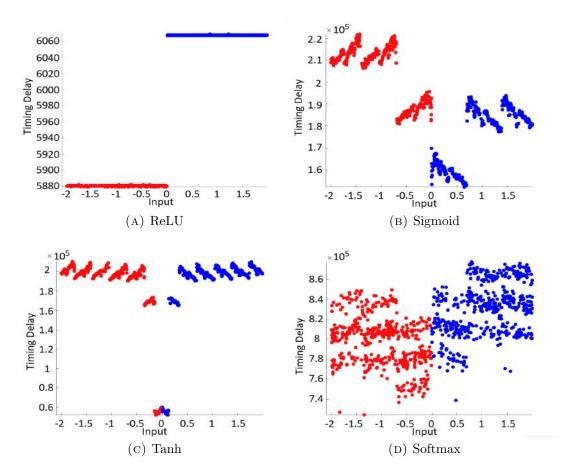

| 5.3        | Timing for different activation functions. Taken from [16] (a) ReLU                                                                                                                                                    |

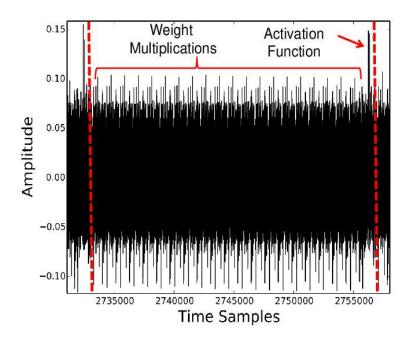

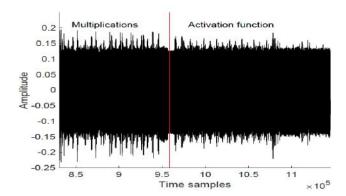

| 5.4        | Difference in trace pattern for a multiplication operation and an activation function. Taken from [16]                                                                                                                 |

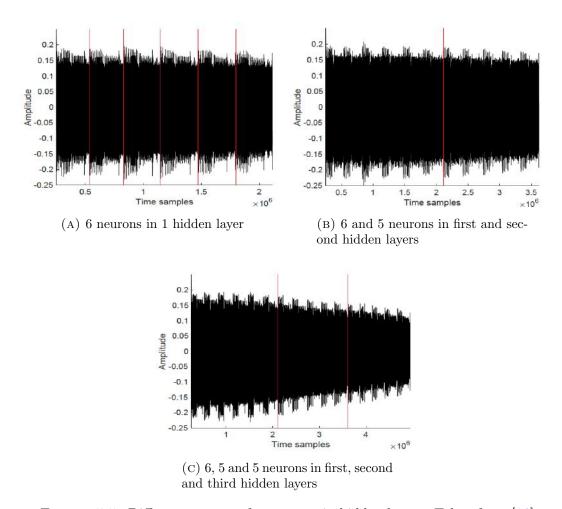

| 5.5        | Different patterns for neurons in hidden layers. Taken from [16]  (a) 6 neurons in 1 hidden layer                                                                                                                      |

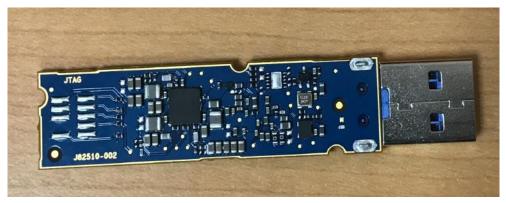

| 5.6        | <ul> <li>(c) 6, 5 and 5 neurons in first, second and third hidden layers</li> <li>NCS2 with its outer shielding and heat sink removed.</li> <li>(a) Top Side with the Myriad X VPU</li> <li>(b) Bottom Side</li> </ul> |

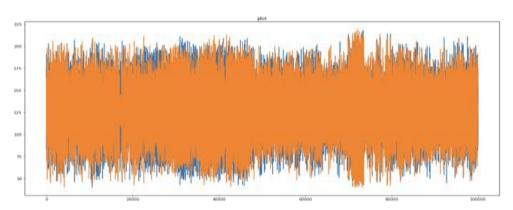

| 5.7  | An example of trace collected after running the neural network       | 77 |

|------|----------------------------------------------------------------------|----|

| 5.8  | Experimental Setup for performing side channel attack                | 78 |

|      | (a) Complete Hardware Setup                                          | 78 |

|      | (b) Setup of Raspberry Pi, Probe and NCS2                            | 78 |

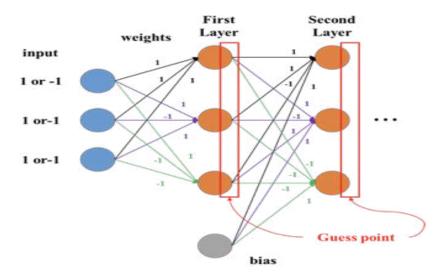

| 5.9  | Weights of the first two layers and the guess points being attacked. | 79 |

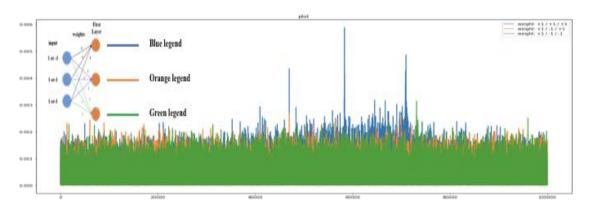

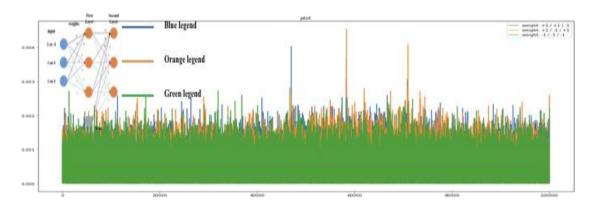

| 5.10 | Traces from the first layer of the neural network. Different colors  |    |

|      | represent the different neurons in the first layer                   | 80 |

| 5.11 | Traces from the second layer of the neural network. Different colors |    |

|      | represent the different neurons in the second layer                  | 81 |

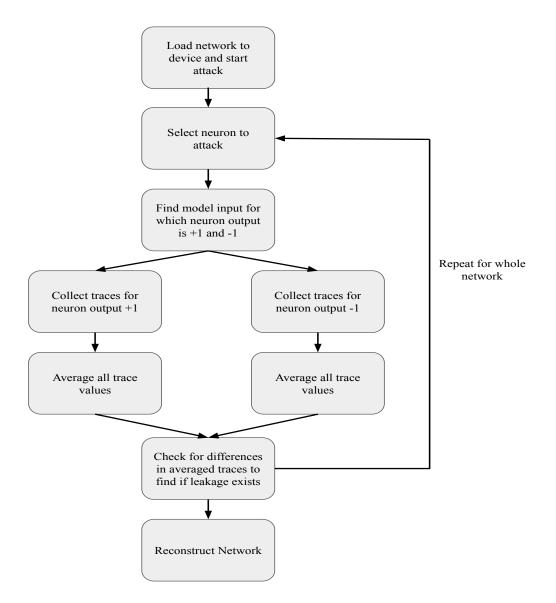

| 5 12 | Methodology to reconstruct neural network                            | 82 |

# List of Tables

| 3.1 | Class-wise distribution of data                                   | 44 |

|-----|-------------------------------------------------------------------|----|

| 3.2 | Description of CNN architectures                                  | 50 |

| 3.3 | Classification accuracy using X/Y, where X is per-sample and Y is |    |

|     | per-track overall balanced values                                 | 51 |

| 3.4 | Accuracy of model after DFP quantization and Finetuning           | 54 |

| 4.1 | Error Rate (%) With CBA on Raspberry Pi                           | 59 |

|     | Baseline Model Recovery on Different Datasets From [?]            |    |

|     | RAD after Task Accuracy Recovery on Pretrained Models             |    |

| 5.1 | Success Rate for Different Architectures                          | 72 |

## Abbreviations

AI Artificial Intelligence

CBA Cold Boot Attack

CNN Convolutional Neural Network

**DFP D**ynamic **F**ixed **P**oint

EBBI Event Based Binary Images

EIE Efficient Inference Engine

GT Ground Truth

IIoT Industrial Internet of Things

${\bf IoT} \qquad {\bf Internet\ of\ Things}$

NCS Neural Compute Stick

NVS Neuromorphic Vision Sensor

SCA Side Channel Attack

SCNN Sparse Convolutional Neural Network

SNN Spiking Neural Network

TPU Tensor Processing Unit

To My Parents, Thank you for all your love and support

# Chapter 1

## Introduction

#### 1.1 Motivation and Background

Over the last decade, the popularity of smart connected devices has led to an exponential growth of Internet of Things (IoT) devices. Around the same time, the availability of a vast amount of data and parallel computing using GPUs has also increased the applications of deep learning and neural networks.

FIGURE 1.1: Growth of IoT devices connected to the internet compared to non-IoT devices. Taken from [10]

Figure 1.1 shows that the number of IoT devices is expected to more than triple by 2025 as compared to 2018. Moreover, the number of IoT devices will be approximately twice as many as the number of non-IoT devices connected to the internet.

Figure 1.2 shows that nearly \$8 billion were invested in AI companies just in the second quarter of 2019. This number is also expected to rise over the next few years. More and more companies are investing heavily and trying to build products that use AI to enhance their functionality. Figure 1.3 shows that by 2030, it is projected that augmented intelligence and smart products will make up more than 50% of the total revenue generated by AI products. This shows the importance, value and ubiquity that AI and IoT will have in our lives over the next few years.

FIGURE 1.2: Funding that AI based companies have received per quarter. Taken from [11]

FIGURE 1.3: Business value brought about by AI based products over the next decade. Taken from [12]

While both of these fields were progressing separately, in the last few years, researchers have tried to run deep learning models on IoT devices. This computing paradigm where networks are run at the place where data is generated (IoT devices) is known as edge computing.

FIGURE 1.4: Edge Computing is a computing paradigm where computation is done on nodes near where the data is generated. Taken from [13]

Today, most data is still sent to cloud servers to perform the analytics tasks that many IoT products perform. However, due to the increase in IoT devices, this is not a feasible solution anymore. Moreover, many IoT devices generate a vast amount of data which is not possible to be sent to a cloud server. This is why there has been a shift to edge computing, whereby analytics and deep learning models are run at the node where the data is generated.

However, most edge devices are cheap and contain very little compute power. Due to this, it is not easy to run complex neural network architectures in such devices. This is why efforts have been made to reduce the compute requirements of neural networks and to pack more computational power into smaller devices.

One of the ways to do the former is to quantize [4] and prune neural networks [24]. While these methods do work, they are often accompanied by a drop in accuracy and research efforts need to be put in to regain the lost accuracy. Many companies like Intel and Google are also building custom hardware to run complex models on edge devices. The advantage here is that the original model can be executed without a drop in accuracy. However, many of these custom hardwares are limited to the types of architectures that can run them, and they consume a large amount of power.

Another problem with edge computing is security threats. Edge devices are usually placed in the open with minimal security features. This makes them very easy to attack. While software-based attacks are well studied, and security measures are known [25], hardware attacks and protection from such attacks on neural networks is still in its nascent stages [8].

The rise in popularity of both IoT and Deep Learning, along with the increase in the availability of data makes it an opportune time to apply machine learning models at the edge. This is why edge computing will become the broad topic of this research, and focus will be put on developing algorithms that can efficiently run on the edge as well as securing the models from side-channel attacks.

#### 1.2 Outline

The rest of this thesis is organized as follows: In Chapter 2, an overview of the different areas being explored is given.

In chapter 3, a neural network model for classifying images captured by a neuromorphic vision sensor data is presented. Following that, a quantization method to reduce the number of computes required to run the neural network is presented.

In chapter 4, a method to extract neural network architecture and weights from a commercial neural network accelerator using a cold-boot attack is demonstrated. Further, we also show how to regain the loss in accuracy (due to erroneous weight recovery) using knowledge distillation.

In chapter 5, a way to attack neural networks using side-channel attacks is presented. We first show that it is possible to identify the kind of pre-trained neural network running on a neural compute stick with nearly 100% accuracy. Thereafter, we try to extract the model parameters of a custom binary weighted neural network architecture. The results of the attack on this network running on a neural compute stick is reported.

Finally, in chapter 6, an overview of all the results and potential future works are outlined.

# Chapter 2

### Literature Review

In this chapter, a review of edge computing and the techniques used to reduce model complexity is presented. This includes quantization techniques like INT8 quantization [26] and efficient neural network layers like separable depthwise convolutions [27], as well as edge computing hardware like the Neural Compute Stick and the EdgeTPU [28], [29]. This is followed by a review of retina-inspired Neuromorphic Vision Sensors (NVS). Finally, the current state-of-art on side-channel attacks and protection techniques on edge computing hardware is discussed [30].

#### 2.1 IoT and Edge Computing

Internet of Things (IoT) is a system of interconnected devices that can transfer and receive data over a wireless connection. IoT devices generally contain a microcontroller and multiple sensors which they use to gather information and perform a task. This has made them very popular as smart home devices like digital assistants, smart lights and fitness trackers. However, the presence of sensors has also increased their application in industrial settings. This sub-branch of IoT called Industrial IoT or IIoT uses such devices to perform tasks like monitoring, predictive maintenance and surveillance.

To perform many of these tasks, IoT devices collect data from sensors, perform some predictive analysis on that data and then either take some action or send an alert to a human in case of anomalous behaviour. Most of this analysis is done by deep learning or machine learning models in the cloud.

Edge Computing is a computing paradigm where computation is done closer to the place where data is being generated. This is different from the more common cloud computing paradigm where data is sent to a cloud server where it is processed and then sent back.

Edge computing is quickly becoming more common with the increase in IoT devices. This is primarily because IoT devices generate a lot of data. In many cases (for instance, surveillance and security cameras), it is not possible to send all data to a cloud server to perform inference. Moreover, in time-sensitive operations, or areas without an internet connection, it is not possible to send data over a network connection.

Some other advantages of edge computing include:

- 1. **Security**: Many industries work on sensitive or IP protected materials, devices or processes. In such cases, sending data over a network can expose them to data breaches. With edge computing, the data never leaves the device where the data is generated hence giving increased security.

- 2. Power Consumption: Many IoT devices are deployed in remote areas as battery-powered units. Such devices are expected to run on their own either by harvesting energy or with limited battery changes. Since sending data over wireless connections require much power, performing computations at the edge, on the device, will be beneficial.

- 3. Network Latency and Resiliency: Sending large amounts of data over a network has some latency associated with it. This latency can be detrimental in time-sensitive operations like a self-driving car or a predictive maintenance setting. Another issue with networks is their resiliency. A self-driving car going through a tunnel will have limited network coverage, so will devices deployed in mines and remote areas. In such cases, performing calculations at the edge will improve the reliability of the IoT device.

- 4. **Bandwidth**: Some IoT devices like security cameras can produce data in the order of multiple gigabytes per hour. Sending all that data to a cloud

server will be impractical and expensive. Instead, the camera feed can be processed locally and then only important information, like the presence of an intruder, can be transferred.

However, edge devices usually have a limited amount of computational power. Furthermore, since many of them are battery-powered, running complex algorithms and neural networks on them can consume much power. This is why many methods have been explored to reduce the complexity of neural networks. These include using depthwise separable convolutions [27] and quantization [4]. Furthermore, much research has been done on creating energy-efficient neural network accelerators and on using near-data processing [2]. In the next sections, these techniques will be explored.

# 2.2 Adapting Neural Networks for Edge Computing

In this section, some techniques to change the computational complexity of the neural network by making changes in the architecture, weights and the computation method of neural networks will be explored.

#### 2.2.1 Depthwise Separable Convolutions

Convolutional Neural Networks (CNN) is the most widely used neural networks architectures for computer vision tasks. CNNs learn by identifying hierarchical patterns from images. These patterns are used to create a dense embedding that contains all the information of the image. This embedding can then be used by a fully connected network to make predictions from the image.

The most important layer in a CNN is the convolutional layer. Convolutional layers take feature maps of shape  $C_i \times H_i \times W_i$  as input and produces feature maps of shape  $C_o \times H_o \times W_o$  as output.  $C_i$  and  $C_o$  are the number of input and output depth or channels, respectively.  $H_i$ ,  $W_i$ ,  $H_o$ , and  $W_o$  are the input and output height and width of the feature maps. The input feature maps can be an RGB

image, or they can also be the output of another convolutional layer. By being able to stack multiple convolutional layers, CNNs can learn hierarchical features.

The number of MACs in a standard convolutional layer is given by:

$$D_k \times D_k \times C \times N \times W_o \times H_o \tag{2.1}$$

where C and N are the number of input and output channels and  $D_k$  is the dimension of the convolutional filter.

Depthwise Separable Convolutions work by separating the standard convolutional filter into a depthwise convolutional operation and a pointwise convolutional operation.

Filters in the depthwise convolution are applied only to a single channel. This means that the number of filters in a depthwise convolution will be equal to the depth of the input feature map. Furthermore, in a depthwise convolution, the output depth will not change, but the height and width will change.

Pointwise filters are applied across the depth of the image like a standard convolution, and like the name suggests, these filters have a height and width of 1. This means that the output depth after applying this filter will be 1, but the output height and width will remain the same. By applying multiple such pointwise filters on the image, we can get an output feature map with the same shape as a standard convolutional layer.

The number of MACs in a depthwise filter can be calculated by:

$$D_k \times D_k \times C \times W_o \times H_o \tag{2.2}$$

and the number of MACs in a pointwise filter is given by:

$$C \times N \times W_o \times H_o$$

(2.3)

This shows that even though a depthwise filter can have the same input and output feature map shapes as a standard convolution, it has fewer MACs by a factor of:

$$\frac{1}{C} + \frac{1}{D_k^2} \tag{2.4}$$

This makes depthwise separable convolutions very attractive for use in resourceconstrained edge devices.

Depthwise Convolutions were first introduced in the Xception model [27]. They were most notably used in the MobileNet model where it was shown to have significantly fewer parameters and MAC operations as compared to comparable models while still maintaining accuracy [3].

#### 2.2.2 Pruning

Trained networks usually have more weights and trainable parameters than what is required to learn a particular task. Such networks are called overparameterized, and many weights or connections in these networks can be removed with very little loss in accuracy, but a drastic drop in computational cost. This is known as network pruning.

Pruning was first proposed in [31], where weight saliency was used to calculate the importance of each weight. Modern pruning, introduced in [24] uses the magnitude of each weight as a measure of the importance of each weight. By doing so, the authors showed that AlexNet weights [32] can be pruned by  $9\times$ , corresponding to a  $3\times$  drop in MACs, with minimal drop in accuracy. Pruning also involves a finetuning step where the network is retrained after weights are pruned to increase the accuracy.

Networks can also be pruned for other metrics. For instance, in [33], the authors show that they can prune a network to reduce the energy required to run the network. Also, a very different computing paradigm of spiking neural networks (SNN) has been introduced as a method to introduce a parameterizable tradeoff between accuracy and classification energy [5], [6].

However, one problem with pruning is the introduction of sparsity in the model weights [34]. Methods have been proposed to store and compress sparse weights

so as to reduce memory access and perform sparse matrix-vector operations [34], [35], [36], [37]. Often custom hardware needs to be used to execute pruned models efficiently. Efficient Inference Engine (EIE) [36] and Sparse Convolutional Neural Network (SCNN) [37] are examples of such implementations.

Due to the challenges in efficiently executing sparse networks, researchers have proposed methods to introduce "structured sparsity" in their models [38]. These techniques try to prune groups of weights instead of individual weights. For instance, pruning an entire neuron in a fully connected layer, or an entire filter in a convolutional layer [39] [40]. However, such pruning methods tend to lead to a more significant loss in accuracy [41]

#### 2.2.3 Quantization

Neural Networks are initialized and trained with high precision floating point weight values. The training process involves making tiny adjustments over these values to nudge the network to a minima. After the training process, the same floating-point weight values are stored and need to be loaded to run inference.

Using low precision weights for inference instead can reduce the storage requirements as well as computational cost. This process of reducing the precision of weights is called quantization. One of the simplest forms of quantization is to map the high precision weights linearly to a low precision value like INT8. Another simple quantization technique is to use k-means clustering to map multiple weight values to a single value.

Quantization can be broadly classified into two types: Weight Quantization and, Weight and Activation Quantization. In general, weight quantization methods are concerned only with accurately representing high precision weights in low precision values. This helps to reduce the on-device storage requirements, but not the computational requirements as weights are up-converted to run inference [2]. Some exceptions are binary and ternary neural networks where the weights are converted to two and three values respectively and then used for inference [42], [43]. Finally, while low precision can be used for training networks, they are usually not done due to the sensitivity of the gradients during training [44], [45], [46].

Figure 2.1: Various methods of number representations. Taken from [2]

Weight and Activation quantization quantizes both the weights as well as the activations in the network. This not only helps reduce the memory requirements of the network, but it also uses the quantized values to execute the network. The most common technique for this method of quantization is INT8 quantization [26]. By using Integer only arithmetic, the authors were able to quantize ResNet-50 [47] with less than a 2% drop in accuracy.

Neural networks can also be quantized partly. In this case, only the most computationally expensive layers are quantized, or the layers which affect the accuracy the least are quantized [48]. Moreover, it is not necessary that all layers in the network be quantized to the same quantization level. For instance, in Dynamic Fixed Point (DFP) [7] quantization, different layers in the network can have different quantization levels. This technique uses the fact that different layers have different ranges of weights to quantize their weights. Moreover, activations will have a far different distribution of values than weights, and it makes sense to quantize them separately. This helps better cover the range of values in weights and activations.

In DFP quantization, numbers are quantized to the form  $(-1)^s \cdot 2^{-fl} \cdot \sum_{i=0}^{B-2} 2^i \cdot x_i$  where B is the bitwidth, s is the sign bit, fl is the fractional length and x is the mantissa bits. The value of fl can be adjusted for each layer and its activations. Earlier layers can use larger values of DFP to take advantage of the increased precision, and later layers can use a smaller value of DFP to accommodate a larger range of values. Using this quantization scheme, the authors were able to quantize LeNet to 4 bits with only a 0.1% decrease in accuracy.

FIGURE 2.2: Data path of quantized convolutional and fully connected layers. Taken from [7]

#### 2.2.4 Knowledge Distillation

Knowledge Distillation (KD) is a model compression technique that uses a teacherstudent training paradigm to teach a smaller student model to emulate the performance of a larger teacher model. Knowledge Distillation was first introduced by in [49] and improved by Hinton et al. in [50].

To transfer knowledge to a student, the teacher model first outputs predictions for a set of training images. The input image and the softmax outputs of the teacher model are used as the input-output pairs to train the student model. The hard labels are not used since they do not contain enough information for the student to learn. However, for a well trained teacher model, even the soft outputs can have a probability distribution with the correct class with a very high probability. This is why, in addition to using soft labels, Hinton et al. also proposed using softer outputs by using a Temperature Factor T. This was called Softmax Temperature, and the probability  $p_i$  of a class i is calculated by

$$p_i = \frac{e^{\frac{z_i}{T}}}{\sum_i e^{\frac{z_i}{T}}} \tag{2.5}$$

By setting T=1, the standard softmax distribution is gotten. However, with larger values of T, the output probability distribution can be made softer. By providing softer inputs, the student model can get more knowledge about which classes are similar to each other and help the student learn the teacher model's internal representation better.

Knowledge in a neural network can be represented in multiple ways. The output of a model given an input is known as the response-based knowledge of the neural network. This is the type of knowledge that was being distilled into the student using the technique being proposed by Hinton et al [50]. However, neural network can also have other types of knowledge embedded in them. For instance, deep neural networks are good at learning multiple levels of features in each layer. This is known as feature-based knowledge distillation and techniques to teach student networks this kind of knowledge has also been proposed.

Bengio et al.[51] proposed using the outputs of the final layer as well as the feature maps of intermediate layers from the teacher model to supervise the training of the student model. In FitNets [52] the authors propose using intermediate representation or 'hints' from the teacher model to train the student model. The student model learns by trying to match the feature activations of the teacher.

Further, since the student model learns from the soft outputs of the teacher, unlabelled data can also be used to train the student model. In [53], the authors use KD has been used as a method to increase the accuracy of the student network by using a trained teacher model to generate pseudo labels for a large unlabelled image dataset. This kind of semi-supervised training has been shown to improve the accuracy of the student model on ImageNet by 2%.

Finally, KD can also be combined with some of the previous model optimization techniques to further compress the student model. For instance, KD can be combined with pruning [54] [55] as well as quantization [56] [57] [58] to improve the performance of the model on edge devices.

#### 2.3 Neural Network Accelerators

Along with deploying efficient models, efforts have also been made to create custom hardware and accelerators that can efficiently run networks on hardware. Some of these hardwares are built, keeping in mind a specific network architecture or quantization method [59], [60]. On the other hand, some hardware like the Neural Compute Stick [28] and the EdgeTPU board [29] can run any neural network architecture.

#### 2.3.1 Neural Compute Stick

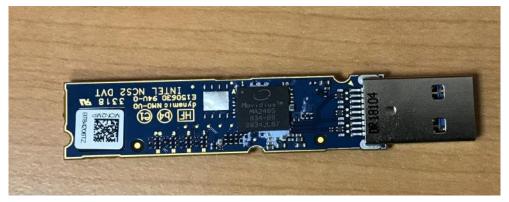

The Neural Compute Stick (NCS) is a neural network accelerator that contains a Vision Processing Unit (VPU) [61]. The device has the form factor of a pen drive and consumes a power of only 1W. The advantage of using a neural compute stick is that it can be attached to any microcontroller (running either Windows or a Linux based OS) with a USB-A type connection.

The VPU inside the NCS is called the Myriad X VPU. It contains a Neural Compute Engine that can perform 1 trillion operations per second (TOPS). It also contains 16 vector processors that can run inference parallelly on multiple data points. Combined, the vector processors and the neural compute engine can provide 4 TOPS of computing performance.

The NCS uses the OpenVINO toolkit [62] as an interface between itself and the hardware it is connected to. The model is first loaded onto the device. Once loaded, it is not cleared until the device powers off, or a new model is loaded. Data can be then sent to the device to perform inference. Moreover, data from multiple sources can be batched together and sent to the device for inference. Another advantage of using NCS is that multiple devices can be interfaced and the inference load can be shared across the multiple devices.

#### 2.3.2 EdgeTPU Board

Another popular edge computing hardware is the EdgeTPU dev board and the EdgeTPU accelerator by Google. The dev board contains an EdgeTPU System

FIGURE 2.3: Intel Neural Compute Stick 2. Taken from [14]

on Model that contains a Quad-core Arm Cortex-A53 as well as an EdgeTPU accelerator co-processor [63]. Since the device contains multiple I/O as well as its own processor, it can be deployed as-is with a working model.

FIGURE 2.4: EdgeTPU DevBoard. Taken from [15]

The accelerator is similar to the NCS and has a USB form factor. It contains only the EdgeTPU accelerator co-processor and needs to be interfaced with a microcontroller to run neural networks [64].

FIGURE 2.5: EdgeTPU Accelerator. Taken from [14]

Both the dev board and accelerator can run TFLite models [65]. Models are first loaded on to the device, and then data can be sent to the device for inference. While TFLite is a more developed framework, it has a few disadvantages. Firstly, it cannot perform inference on batches of data, and multiple EdgeTPU boards cannot be interfaced to improve inference speeds.

#### 2.4 Neuromorphic Vision Sensors

Along with efficient neural networks and hardware, efforts are also being made to make efficient sensors. RGB cameras are commonly used cameras in edge computing systems. The high frame rates in RGB cameras, as well as increased memory and bandwidth transmission requirements, make them have high power requirements and unsuitable for remote edge computing applications [66]. Moreover, when performing tasks like object tracking and identification, proposing RoIs involves computationally intensive steps which leads to a further increase in power

consumption [67]. Due to these reasons, an alternative to standard RBG cameras is to use Neuromorphic Vision Sensors (NVS).

NVS use a retina-inspired principle and capture changes asynchronously on a pixel level. Each pixel capture intensity changes independently hence giving NVS low data rates, high effective frame rates, high dynamic range and low power [68], [69], [70].

Furthermore, since NVS capture only dynamic events, backgrounds being static are automatically removed. This makes NVS suitable for remote surveillance using a static camera, where the background does not change relative to the objects being tracked. However, using NVS as the primary camera sensor requires the use of algorithms that can learn and predict from asynchronous events, or requires the conversion of these events into frames that can be fed into a standard neural network architecture for inference.

One of the ways to detect and track an object using NVS is to dynamically update the representation of the object as and when new events are generated [71], [72], [73]. However, these methods fail when trying to track multiple objects, and they work better for certain specific applications [73].

Another method of processing events is to aggregate events over a certain period of time and then processing all the aggregated events [74], [75], [76]. This is a much better approach since the output frames are similar to those produced by an RGB camera, and traditional classification techniques can be used. For instance, in [74], events were aggregated at intervals of 10ms and 20ms, and then clustering algorithms, as well as Kalmann filters, were applied for object detection and tracking.

To further reduce the power consumption, a low power tracking algorithm using stationary NVS was proposed in [77]. This work used a combination of frame-based as well as event-based approaches to perform tracking and classification. Aggregating events first generated frames. These were fed into a tracker to get the location of the objects. Finally, the frames were converted back to spikes for classification on IBM's TrueNorth neuromorphic chip [78].

In [17], the authors propose using a connected component labelling (CCL) based approach to track objects. The generated frames were then fed into a convolutional

neural network for classification. Finally, in [20], the authors show how to combine detector and classifier into the same network to improve the performance of the overall pipeline.

### 2.5 Security and Privacy of Edge Computing Hardware

An increasing concern in the deep learning field is the protection of model data in their deployed models as well as protection of the model from adversarial attacks [25]. It has been shown that private and sensitive information, are stored in the weights of trained neural networks, and can be retrieved by an attacker [79]. Moreover, just getting access to the weights and architecture of a trained neural network can motivate attackers who might not have access to the same dataset or compute power to train a network from scratch. This is an increasing concern since more companies and entities are using deep learning models for sensitive applications at the edge [80], [81]. An overview of such attacks is given in [82]. However, most of these attacks are software-based, and few works focus on the security of networks from attackers trying to extract models and gain information through vulnerabilities and leakages from hardware where models are deployed.

One of the first attacks demonstrating model extraction was done by Tramer et al [83], where the authors show that it is possible to get a model with similar performance from a black box API without access to the original dataset or model parameters. Physical access to edge computing hardware can allow attackers to exploit even more attack vectors like side-channel leakages [23] and faults [84]. Side channels like power, electromagnetic and timing can be used to recover model parameters. A review of these attacks can be found in [85].

In [86], the authors propose different levels of model extraction attacks based on the complexity and severity of the attack:

1. **Exact Extraction**: In this case, the extracted model has the same architecture, weights and other parameters as the original model. This is the best possible extraction attack, but at the same time, it is the hardest to perform especially in a limited attack setting.

- 2. Functionally Equivalent Extraction: This is a slightly weaker extraction assumption but a more likely attack. In this case, the output of both the extracted and original model needs to be the same for all inputs in a given domain. This type of extraction is hard to perform if the attack only has access to the input/output pairs from the original model.

- 3. **Fidelity Extraction**: In this type of extraction, the extracted model should have an output which is as similar to the output of the original model. Fidelity extraction is a slightly weaker assumption than Functional Extraction (where the similarity is 1).

- 4. **Task Accuracy Extraction**: This is the weakest assumption where the extracted model is expected to achieve a similar or higher accuracy as compared to the original model. This is the easiest goal since the extracted model does not need to match the mistakes of the original model.

In this section, a review of the security of edge computing hardware from the perspective of side-channel attacks and cold boot attacks will be done.

#### 2.5.1 Electromagnetic Side-Channel Attacks

Side-channel attacks (SCA) is the use of physical leakages from hardware to extract information of the data, or computations being performed in it. To achieve this, side-channels attackers try to observe electromagnetic leakages, timing delays, power consumption and other leakages during the execution of operations inside the device.

SCA was first used in cryptography applications to recover keys [87]. Using SCA, it was possible to recover only small parts of the key at a time, thus reducing the complexity of the attack. However, recent works have shown that SCA can also be used to recover the weights, operations, and architecture of neural networks just from EM leakages [16].

Before looking at how attacks are performed, it is vital to understand the different SCA attack techniques for EM leakages as well as the attack scenario and the attacker capabilities.

There are two main types of attacks performed on EM leakages:

(A) Complete Measurement Setup

(B) Target Microcontroller without covering (C) Probe used for measuring EM leakages

FIGURE 2.6: Experimental Setup for performing side channel attack. Taken from [16]

- 1. Simple Power or EM Analysis (SPA): This uses a few EM traces generated from the hardware to understand the computation that is happening inside the hardware. Since SPA uses only a few traces, it can be used to extract straightforward or simple operations.

- 2. Differential Power or EM Analysis (DPA): Unlike SPA, DPA uses many measurements (sometimes in the order of millions) to apply statistical techniques to extract information. Using correlation, an attacker can find the difference between an actual measurement and hypothetical measurement. By making small variations in the input and seeing the change in the measured signatures, it is possible to get information about the operations and data. Such attacks have been successfully used in ASICs and GPUs [88], [89].

FIGURE 2.7: Traces generated from probe. Different operations generate different leakage patterns. Taken from [16]

To perform these attacks, it is assumed that the attacker has access to the hardware running the model. This is a reasonable assumption since many edge computing hardware can be bought off the shelf, and the attacker can run experiments uninhibited. Once an attacker knows how to attack a particular hardware, then they can use that knowledge to attack a product with sensitive data using the same hardware.

In such a scenario, it is assumed that the attacker does not know the model weights or its architecture; however, they are able to feed in any input to the model. Finally, the attacker should also be able to measure side-channel leakages during their attack.

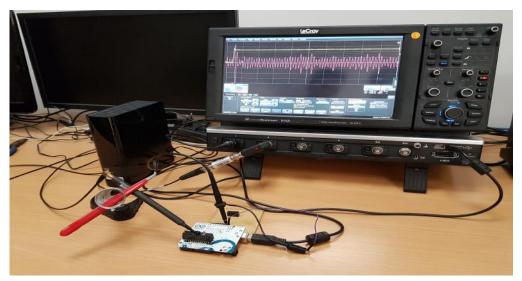

Using these constraints, [16] showed that it is possible to extract information regarding the activation function, model weights and model architecture from an Atmel ATmega328P and on an ARM Cortex-M3. They used a Lecroy WaveRunner 610zi oscilloscope and an RF-U 5-2 near-field electromagnetic probe to collect the EM leakages. The attack was done on a simple Multi-Layer Perceptron model as well as a CNN model.

FIGURE 2.8: EdgeTPU Accelerator with its housing and heat sink removed. Attacks are done after removing the housing of the board. This helps to get better reading of the leakages.

However, these attacks assume that the network execution calculations are done sequentially, which makes the attack much more straightforward. In such a case, shuffling the order of execution of the different computes in a layer can help prevent (or at least slow down) these attacks [90].

Another countermeasure to weight recovery is to use masking [91] [92]. In such a case, calculations are done with random values instead of actual data to remove the dependence on actual values when performing an attack. In [8], the authors propose MaskedNet which uses masked ReLU units as well as masked adder trees for FC layers to prevent side-channel attacks. However, these masked approaches can be accompanied by an increase in the execution time of the network.

#### 2.5.2 Timing Side-Channel Attacks

Unlike electromagnetic leakages, timing side-channels utilizes timing leakages from hardware to infer information about the type of operations and parameters inside a neural network.

One of the first works showing the use of timing side-channels was by Hua et al.[93]. They show that it is possible to find the type of layers used in a CNN model running on an Intel SGX device[93]. Using a combination of timing and memory leakages, the authors are able to extract information about the model

architecture and weights. Similarly, in [16], the authors use timing leakages to infer the type of activation function in models running on ARM devices.

Another timing side-channel model extraction attack was proposed by Duddu et al. in [94]. They feed the timing leakages to a regressor model that predicts the depth of the victim neural network. Once the depth of the network is extracted, they perform task accuracy extraction by using reinforcement learning to create an optimal neural network with a similar accuracy using Architecture Search. In Dong et al.[95], the authors use timing information from power consumption trace during Floating Point operations to infer input pixel values to the neural network.

All the previous attacks were performed on custom implementations on general purpose hardware like CPUs, microcontrollers and FPGAs. However, with the recent popularity of edge computing, commercially available high performance deep learning accelerators are being increasingly used to deploy models. The vulnerability of deep learning models in such accelerators to timing side-channels is still an open question and is investigated in this work.

#### 2.5.3 Cold Boot Attacks

SRAM, SDRAM and other volatile memory are integral to any computing systems. They are called volatile because they lose their data upon power off. Since RAM data is volatile, it is used to store information like passwords, PINs, keys and other private and sensitive data. However, it has been shown that by cooling the RAM to below freezing temperatures, it is possible to delay the deterioration of the data in the RAM. This property of data remanence of RAM data is what is exploited in cold boot attacks (CBA).

CBAs were first proposed in 2008 by Halderman et al. in [22]. They show that by freezing the RAM to  $-50^{\circ}C$ , it is possible to recover RAM data from multiple laptops. In addition to that, they also showed that it is possible to recover secret AES and RSA keys from the dumped RAM data. Later, in 2013, it was shown that it is possible to recover RAM data from mobile phone devices and recover PINs, secret keys and decrypted mount data from the RAM dump [96]. It has also been shown that CBAs can be effective against newer generation of memories with memory scrambler countermeasures (like those in DDR3 and DDR4 RAM) [97].

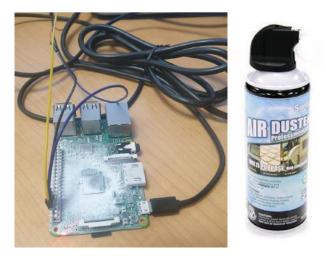

FIGURE 2.9: Raspberry Pi model B+ (Left) frozen using an air duster (Right). Taken from [9]

However, in the previous examples, the RAM is present as a standalone device. In case of IoT devices like Raspberry Pi's, RAM is usually present on-chip or as a stacked package. This makes CBAs more challenging since the boot sequence of the main board needs to be bypassed[9]. In Won et al. [9], the authors show that it is possible to recover RAM data from a Raspberry Pi with more than 99% recovery rate by freezing the RAM to  $-30^{\circ}C$ . Further, they also show that at that temperature, even with a decay time of 10 seconds, their recovery ratio is still more than 99%. They do this attack with an air duster and the whole attack costs less than \$10 which makes it even more serious.

FIGURE 2.10: CBA recovery results for different decay times and freezing temperatures. Recovery is better the higher the temperature and lower the decay time. Taken from [9]

While cold boot attacks have been shown to be successful with recovering secret keys and passwords, they are still prone to many errors. When it comes to performing model extraction with CBA, these errors can significantly affect the accuracy of the model. It has been shown that even with a single bit flip, the accuracy of neural networks can drop by more than 99% in the worst case and up to 40% in the best case scenario. This means that even with a recovery rate of more than 99%, even performing task accuracy extraction using CBA can be a challenge. To the best of our knowledge, using cold boot attack for model recovery has not been investigated before.

#### 2.6 Conclusion

Edge computing involves running neural networks on IoT devices. These devices generally have low computational power, low memory and are often battery operated. This makes it challenging to run neural networks as they often have large weights and complex architectures with many computes.

In this chapter, a review of the challenges of running neural networks at the edge has been covered. The first was how to change the layers and weights of neural networks to make computes lesser. These included techniques like pruning, quantization and changing convolutional layers with depthwise separable convolutions. Secondly, from the hardware aspect, it was seen how using neural network accelerators can help speed up computation at the edge. Another aspect is to use more efficient sensors at the edge. Neuromorphic Vision Sensors which capture only intensity changes are one such device. Using NVS instead of RGB cameras can reduce the power consumption of your overall edge system. Finally, different methods of attacking and protecting neural networks running on edge devices from side-channel attacks were reviewed.

## Chapter 3

# Neuromorphic Traffic Data Classification

In this work, a "what" and "where" pathway approach, similar to that of our brain's visual cortex [98] is used to locate and predict objects in images generated by a Neuromorphic Vision Sensor (NVS) [19] [99]. Furthermore, the neural network trained is such that it can be deployed to a memory and compute constrained edge device. To further reduce the complexity of the network, Dynamic Fixed Point (DFP) based quantization [7] is also applied on the network.

First, an overview of the NVS dataset is presented. After that, the process of generating frames or Event Based Binary Image (EBBI) from a DAVIS NVS [19]

FIGURE 3.1: what-where pathway approach with a DAVIS NVS. Taken from [17]

is explained. This is followed by an overview of the region proposal algorithms used to extract regions of interest from the EBBI images. Moving on, the model architecture, training methodology and training results are presented. Finally, the DFP quantization method and the quantized model accuracy is shown.

#### 3.1 Dataset Overview

The dataset used in this work is the same as the one used in [77]. The data was collected by recording traffic on roads during the daytime. Recordings were done at multiple locations with different characteristics like angle of road, presence of trees, buildings and other objects and distance of road from the recording location. This gave us a wide range of scenarios to study the efficacy of data capture as well as neural network training and classification. The data was annotated manually and contained five classes: car, bus, truck, van, human and bike. Along with the class, these Ground Truth (GT) annotations also contained a unique track id for each object in the frame as well as their bounding boxes.

The data was divided into a training and testing set, where the testing set contained recordings from sites not present in the training set. The same training-testing split was used while training all the different kinds of models. An overview of the data can be found in Table 3.1

|           | Trair           | n/Valida                | $\overline{	ext{tion}}$ | Test            |                |             |  |

|-----------|-----------------|-------------------------|-------------------------|-----------------|----------------|-------------|--|

|           | Sample<br>Count | Track Size<br>Count WxH |                         | Sample<br>Count | Track<br>Count | Size<br>WxH |  |

| Car       | 17342           | 460                     | 44x19                   | 2984            | 84             | 44x19       |  |

| Bus       | 6954            | 246                     | 101x41                  | 1544            | 58             | 101x41      |  |

| Truck/Van | 7272            | 205                     | 50x25                   | 1216            | 32             | 50x25       |  |

| Bike      | 1737            | 58                      | 21x16                   | 183             | 6              | 21x16       |  |

| Sum       | 33305           | 969                     |                         | 5927            | 180            |             |  |

Table 3.1: Class-wise distribution of data

FIGURE 3.2: Camera setup with ZED [18] RGB cameras and DAVIS [19] NVS. Taken from [20]

#### 3.2 Data Collection and Preparation

A DAVIS [19] Neuromorphic Vision Sensor (NVS) was used to capture the data used in this work. Traffic data was collected from multiple different sites during daytime. The NVS sensor was placed perpendicular to the road at a height to create the recordings. A standard RGB camera was also used to simultaneously capture the same scene for comparison with the NVS captured data. While humans were also captured in the data, they generated few events and had very few features. Therefore they were not used in this work.

#### 3.2.1 Event Based Image Generation

To create images from the events recorded by the NVS, all events happening during a fixed time interval,  $t_f = 66 \text{ms}$ , were aggregated. These events could have two types of polarities: an ON polarity represented by 1 or an OFF polarity represented by 0. These polarities correspond to an increase or decrease in the activation of the sensor at that pixel. Since NVS cameras generate events when there is either an ON event or an OFF event, images generated can either have 1 channel, or 2 channels. By making different combinations of polarities and aggregations, four types of images were created:

• 1 Bit, 1 Channel (1B1C): These images were created by recording any event during  $t_f$  as a 1, and no events as a 0. These events were recorded without considering the polarity of the event.

FIGURE 3.3: Examples of EBBI (Left) and RGB Image (Right), recorded at different sites. Taken from [20]

- 1 Bit, 2 Channel (1B2C): To get two channels, events occurring in the different polarities were recorded separately as different channels in the image. Any activity in each channel during  $t_f$  is recorded as a 1, and a lack of activity is recorded as a 0. 1B2C images can be converted to a 1B1C images by taking a logical OR of the two channels.

- Multi-Bit, 1 Channel (MB1C): In this case, multiple events, regardless of their polarity, are aggregated pixel-wise. These aggregations are clipped at 15 to limit spurious events.

- Multi-Bit, 2 Channel (MB2C): These images were obtained by aggregating the events in the two channels separately. Just like in MB1C, more than 15 events were clipped.

The "where" pathway uses low-resolution images to track objects. On the other hand, the "what" pathway uses the high-resolution images to identify the objects in the image. More details about the implementation of the "what" and "where" pathways are given in the next sections.

#### 3.2.2 Region Proposal Algorithms

The "where" pathway in the what-where pathway approach is responsible for identifying regions in the image where objects are present. While many region proposal algorithms like YOLO [100], Mask-RCNN [101] and MobileNet-SSD [102] exist, they require a lot of computes to execute. Moreover, such networks would be excessively complex for finding objects in 1-bit images. For this work, more straightforward and low complexity methods were explored.

In [77], 1D histograms of the events were summed and projected along the X and Y-axis of the 1B1C images. This approach is referred to as the "HIST RP" method. While this is simple and fast to implement, it has some significant flaws. Firstly, since the projections use a side view to generate histograms, proposals for smaller vehicles can appear to be larger, especially if they are present near bigger vehicles. Furthermore, since the projections are 1D, much of the information in the image is lost. Additionally, in case the road is present in an angle in the frame, this technique will lead to the creation of multiple false region proposals. Finally, since many of the objects appear as distinct fragments of pixels (caused due to the presence of windows which do not generate any events), the same object can be proposed as multiple close by objects.

To overcome these drawbacks, a Connected Component Labelling (CCL) approach was used [103]. To apply CCL, the original 240x180 pixel frame was downsized to a 40x60 pixel frame by applying a 6x3 logical-OR patch on the frame. Downsizing helps merge all the fragmented objects and also reduces the computes required. CCL was applied in two passes [104], and the tight bounding boxes generated were then scaled up and mapped back to the original image.

To test the efficacy of the proposed regions, it was compared with the GT bounding box annotations. A proposed region was considered valid only if it had an Intersection over Union (IoU) greater than 0.1. To create images of a fixed size

FIGURE 3.4: X and Y histogram projection based region proposals. Taken from [21]

FIGURE 3.5: Disadvantages of HIST RP based region proposal: (a) Normal Region Proposal; (b) (c) Large bounding box due to bigger object; (d) False region proposal. Taken from [21]

for the CNN training algorithm, a 42x42 crop was taken from the centroid of each bounding box. Bounding boxes of size less than 42x42 were padded with zero. For larger objects (whose size exceeded 42x42), four similar patches were taken from the four bounding box corners.

The results of training the model on both these region proposal algorithms are highlighted in the next sections.

#### 3.3 Model Overview

The "what" pathway in the "what-where" pathway approach was implemented by using a Convolutional Neural Network (CNN). Most popular CNN architectures used for object classification cannot be used in Edge Computing applications, due to their large size, and computational complexity [1]. In this work, low complexity neural network architectures were explored for classifying the NVS frames.

Architecture exploration was first started with a LeNet-5 based architecture [105]. This architecture is called the Base LeNet5. However, with the large number of convolutions in the LeNet-5 architecture, the number of computes also increases. To reduce the number of computation, the convolutional operation is decoupled by using depthwise separable convolutions [27].

First, all the convolutional layers in the LeNet-5 architecture was replaced with separable convolutions. This architecture is referred to as Base SepNet. However, this architecture does not perform as well because there is no sharing of feature maps across the channels. To overcome this, a mixed architecture model was used where the first convolutional layer was not changed, and subsequent convolutional layers were replaced by separable convolutions. This architecture is inspired by the idea that most features can be learned in a CNN in the first few convolutional layers in the model. Since the features in our dataset are simple, fewer layers should be required to learn those features. This is referred to as the Mixed Architecture Model.

However, a major bottleneck in all CNN architectures is the first feed-forward layer which performs a large matrix multiplication using the flattened features of

| Label | Architecture                | Hyperparameters                       |  |  |  |

|-------|-----------------------------|---------------------------------------|--|--|--|

|       |                             | Base LeNet5 architecture with two     |  |  |  |

| BL    | Base LeNet5                 | CONV layers with average pooling      |  |  |  |

|       |                             | after each layer and three FC layers. |  |  |  |

| BS    | Base SepNet                 | LeNet Architecture with SEPCONV       |  |  |  |

| DЗ    | Dase Sepivet                | instead of 2D CONV layers             |  |  |  |

| MA    | Mixed Architecture          | LeNet Architecture with second layer  |  |  |  |

|       | Mixed Architecture          | as SEPCONV instead of 2D CONV         |  |  |  |

|       |                             | Mixed architecture                    |  |  |  |

| TN    | TinyNet                     | with 5 filters in second layer        |  |  |  |

|       |                             | and only one softmax dense layer      |  |  |  |

| LG    | LeNet With Global Pooling   | Base LeNet with Global Average        |  |  |  |

| LG    | Lenet With Global I doining | Pooling instead of Flatten layer      |  |  |  |

| LK    | LeNet Large Kernel          | Base LeNet with 7x7 kernels in        |  |  |  |

| ΠΙ    | Lenet Large Kerner          | all 2D CONV layers                    |  |  |  |

| SN    | Small LeNet                 | Base LeNet with only one              |  |  |  |

|       | Sman Lervet                 | Softmax dense layer                   |  |  |  |

Table 3.2: Description of CNN architectures

the last convolutional layer. Executing this layer on hardware becomes both a computational and memory bottleneck.

To overcome this bottleneck, two models without any fully-connected layers and only a softmax layer was trained. The first model was the Base LeNet5 model, called Small LeNet, and the second was the Mixed Architecture model called TinyNet. Finally, some simple hyperparameter search was done, by changing the kernel sizes (LeNet Large Kernel), and adding a global pooling layer before the first fully connected layer (LeNet with Global Pooling). An overview of the different architectures trained can be found in Table 3.2.

#### 3.4 Model Training

All the models mentioned were trained on three types of data: 1B1C, 1B2C, MB2C. In the case of multibit images, they were first normalized by dividing with the max pixel value (which in this case was 15). 1-bit images were used as is without any extra preprocessing steps.

The models were trained with minibatch stochastic gradient descent with a batch size of 128 and an Adam Optimizer [106]. The data was shuffled before feeding

it into the network for training on an NVIDIA TITANX GPU. The models were trained for 20 epochs, and the model with the best validation accuracy was selected.

To fairly evaluate the performance of the models, the class imbalance in our dataset had to be taken into account. Therefore, our results were calculated as balanced accuracy on a per-sample and per-track basis. The per-sample accuracy is the average of class-wise sample accuracies, whereas the per-track accuracy is the average of class-wise track accuracies. The per-track accuracy is calculated by taking the mode of the predicted labels for all the samples in the track.

#### 3.5 Results and Discussion