## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Model Predictive Control of Cascaded Multi-Output Multilevel Converter

Jayan, Vijesh; Ahmed S. Hussein; Amer Mohammad Yusuf Mohammad Ghias

2019

Jayan, V., Ahmed S. Hussein & Amer Mohammad Yusuf Mohammad Ghias (2019). Model Predictive Control of Cascaded Multi-Output Multilevel Converter. 2019 IEEE International Conference on Industrial Technology (ICIT), 1247-1251. https://dx.doi.org/10.1109/ICIT.2019.8755162

https://hdl.handle.net/10356/156678

https://doi.org/10.1109/ICIT.2019.8755162

© 2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. The published version is available at: https://doi.org/10.1109/ICIT.2019.8755162.

Downloaded on 09 Apr 2024 15:24:03 SGT

### Model Predictive Control of Cascaded Multi-Output Multilevel Converter

Vijesh Jayan\*, Ahmed S. Hussein\*, Amer Ghias\*

\*School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore,

Email: vijeshja001@e.ntu.edu.sg

Abstract—The paper presents a novel cascaded multi-output multilevel (CMOM) converter topology. The structure is composed of m converters that contain multiple n output voltage terminals. The proposed cascaded multilevel converter can provide multiple independent output voltages, and each output voltage can generate 2m+1 voltage levels. The output voltages are controlled in-terms of amplitude, frequency and phase angle independently. The mathematical model is developed for m=2 converters with n=2 output voltage terminals and is used in model predictive control (MPC) algorithm to optimize the control objectives. Thus the model can provide two different output voltages, each of which can generate up to five voltage levels. The performance is evaluated and demonstrated using MATLAB simulation results.

Index Terms—Multi-output port converter, multilevel converter, model predictive control.

#### I. INTRODUCTION

Multilevel converters have recently become widely adopted in medium- and high-voltage power applications, because they can provide lower power losses and total harmonic distortion (THD) [1]-[4]. The most common types of multilevel converters are the: neutral point clamped (NPC) converter [5], flying capacitors (FCs) converter [6], and cascaded multimodular converter [7]-[13]. Several other designs have also been introduced based on these converters, including Marx multilevel converter [14], modular multilevel converter [8], [9], and multilevel matrix converter [15], [16]. Cascaded multi-modular converter can also provide additional features like modularity and scalability [10], [11]. Additionally, by cascading two similar converter circuits, two additional voltage levels can be synthesized on the output port. Moreover, it also allows for seamless operation in case of failure in any of the cascaded cells [12].

Dual-output converters are another development in the domain of enhanced voltage source converters. Designs like multi-phase, the five-leg converter [17] and the subsequent nine-switch (three phase) [18], [19] and six-switch (single phase) [20] converters provided the capability to drive multiple outputs with either similar or variable frequencies. Since the output voltage of such topologies provides only two-levels, therefore improved topologies emerged to enhance the quality of such dual/multi-output converters. This was done by allowing an additional path from the output terminals to the neutral point either using diodes [21] or bidirectional switches [22]. In both [21] and [22], researchers were able to obtain

multilevel outputs ranging from three to nine levels. However, the designs have a higher chance of having unbalanced dc-bus capacitors, which if not managed properly, can severely affect the quality and operation of the converter [23].

The primary objective of this paper is to present a novel cascaded multi-output multilevel (CMOM) converter topology. The proposed topology is composed of m converters that contain multiple n outputs voltage terminals. It can provide multiple independent output voltages, and each output terminal can generate 2m+1 voltage levels. The output voltages can be controlled regarding amplitude, frequency and phase angle independently. The mathematical model of the proposed converter is developed for m=2 converters with n=2 output voltage terminals and is used in model predictive control (MPC) algorithm to optimize the control objectives. In comparison to the design in [13], the proposed design achieves an additional independent output port by just using two additional power switches per cell. Thus, it further reduces the power switch count for multi-output port applications.

The paper is organized as follows. Section II describes the fundamentals principle of the proposed CMOM converter and the mathematical model of the converter. The model is used to develop MPC strategy. Section III presents simulation results of the proposed CMOM converter. Finally, the conclusions of this work are summarized in Section IV.

#### II. THE PROPOSED CMOM CONVERTER

#### A. Topology and Fundamental

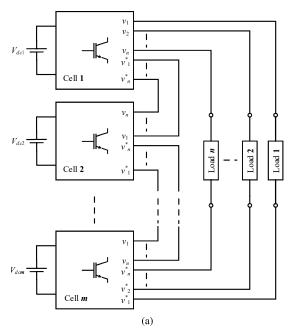

The cascaded structure of m converters with n output voltage terminals is shown in Fig. 1. The converter cells, shown in Fig. 1b contains two legs, in which each leg consist of n+1 power switches. cascading m such converters as shown in Fig. 1 can increase the output voltage up to 2m+1 level across its n terminals.

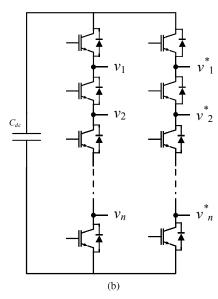

For the sake of simplicity, the cascaded structure with m=2 converters and n=2 output ports is considered (see Fig. 2). Each converter houses six power switches and has nine possible switching combinations with three voltage levels  $(-V_{dc},0,+V_{dc})$ . Cascaded structure of two similar converters can generate five voltage levels  $(-2V_{dc},-V_{dc},0,+V_{dc},+2V_{dc})$ .

#### B. Continuous-Time Model

The continuous-time model of the cascaded converter is modeled using simple circuit analysis given in Fig. 2. The two

Fig. 1. CMOM converter topology, a) connection diagram, b) single cell configuration.

output current equations in continuous time form are given as:

$$\frac{di_u}{dt} = \frac{1}{L}(\overline{v}_{ua} + \overline{v}_{ub} - Ri_u) \tag{1a}$$

$$\frac{di_v}{dt} = \frac{1}{L}(\overline{v}_{va} + \overline{v}_{vb} - Ri_v)$$

(1b)

where  $\bar{v}_{ua}$ ,  $\bar{v}_{ub}$ ,  $\bar{v}_{va}$ , and  $\bar{v}_{vb}$  are the converter output voltages at each terminal and are given as:

$$\overline{v}_{ua} = (S_{1a} - S_{4a})V_{dc1}$$

(2a)

$$\overline{v}_{ub} = (S_{1b} - S_{4b})V_{dc2}$$

(2b)

$$\overline{v}_{va} = (S_{1a}S_{2a} - S_{4a}S_{5a})V_{dc1} \tag{2c}$$

$$\overline{v}_{vb} = (S_{1b}S_{2b} - S_{4b}S_{5b})V_{dc2} \tag{2d}$$

where,

$$\overline{v}_{ux} = v_{ux} - v_{ux}^*

\overline{v}_{vx} = v_{vx} - v_{vx}^*

x \in \{a, b\}$$

(3)

#### C. Discrete-Time Model

The continuous time model of two output currents are transformed into discrete-time by using classical forward Euler method and is given as:

$$i_u(k+1) = \gamma_1 i_u(k) + \gamma_2 (\bar{v}_{ua}(k) + \bar{v}_{ub}(k))$$

(4a)

$$i_v(k+1) = \gamma_1 i_v(k) + \gamma_2 (\bar{v}_{va}(k) + \bar{v}_{vb}(k))$$

(4b)

where,

$$\gamma_1 = 1 - \frac{RT_s}{L} \tag{5a}$$

$$\gamma_2 = \frac{1 - \gamma_1}{R} \tag{5b}$$

considering,

$$x(k) = \begin{bmatrix} i_u(k) \\ i_v(k) \end{bmatrix} \tag{6}$$

as the system state, a discrete-time state-space model of the converter can be represented as:

$$x(k+1) = Ax(k) + Bu(k) \tag{7}$$

where,

$$A = \begin{bmatrix} 0 & \gamma_1 \\ 0 & \gamma_1 \end{bmatrix}, B = \begin{bmatrix} \gamma_2 & 0 \\ 0 & \gamma_2 \end{bmatrix}, u(k) = \begin{bmatrix} \overline{v}_{ua} + \overline{v}_{ub} \\ \overline{v}_{va} + \overline{v}_{vb} \end{bmatrix}$$

(8)

#### D. Control Targets

For the CMOM converter, it is desired to control the output currents of terminal u and v represented as  $i_u$  and  $i_v$  respectively. These control targets are the reference sinusoidal currents expressed as:

$$i_u^*(t) = I_u \sin(\omega_u t + \phi_u) \tag{9a}$$

$$i_v^*(t) = I_v \sin(\omega_v t + \phi_v) \tag{9b}$$

where  $I_n$ ,  $\omega_n$  and  $\phi_n$  are the amplitude, frequency and phase angle of the reference current required to be generated at output terminal  $n \in \{u, v\}$  of the converter. In order to obtain predictions of the system state, the non-linear system can be directly evaluated for the switching combinations. Each system state prediction is evaluated using the quadratic cost function:

$$J_r(k) = e_r(k+1)^T Q_r e_r(k+1)$$

(10)

where the next-step system state tracking error is:

$$e_x(k+1) = x^*(k+1) - x(k+1)$$

(11)

Fig. 2. Cascaded five-level dual-output converter, a) connection diagram, b) single cell configuration (x: a, b).

TABLE I SYSTEM PARAMETERS FOR SIMULATION.

| Parameter          | Value |

|--------------------|-------|

| $V_{dc1}, V_{dc2}$ | 100 V |

| R                  | 5 Ω   |

| L                  | 5 mH  |

| $C_{dc}$           | 1 mF  |

moreover, the system state weighing matrix is:

$$Q_x = diag(\lambda_1, \lambda_2) \tag{12}$$

where  $\lambda_1$  and  $\lambda_2$  are a weighing factor that trades between the current tracking errors. In this paper,  $\lambda_1$  and  $\lambda_2$  are taken as one to achieve equal current tracking performance.

Finally, the optimal switch combination is calculated by minimizing the cost function and is given as:

$$S^{opt}(k) = \arg\left\{\min J_x(k)\right\} \tag{13}$$

#### III. SIMULATION RESULTS

The proposed model is simulated by using MATLAB simulations. The MPC is programmed using a function block with a sampling time of 100  $\mu$ s. The system parameters considered for the simulations are given in Table I. Three case studies are simulated and presented in the following section. The converter terminals u and v operate with an initial reference parameter - amplitude, frequency and phase angle as 25 A, 50 Hz and  $0^{\circ}$  respectively.

The frequency and phase of the reference currents are fixed, i.e 50 Hz and  $0^{\circ}$  respectively for both the output terminals respectively.

#### A. Case I (Variable amplitude mode)

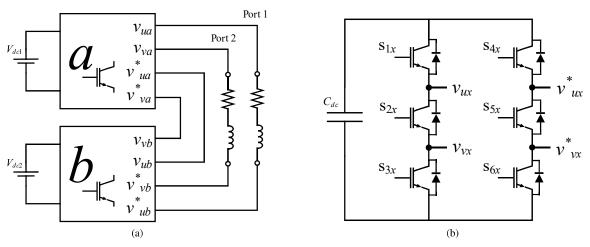

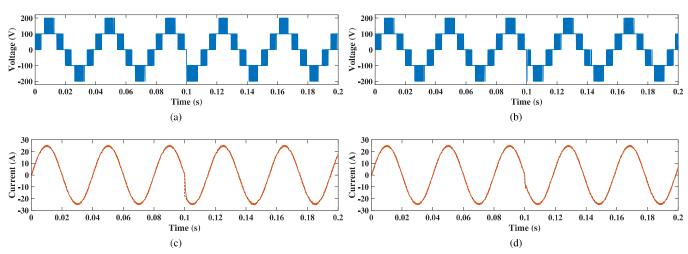

In this study, the converter terminals u and v generate different current amplitudes of fixed frequency (50 Hz) and phase (0°). The behavior of the output voltage and current

are shown in Fig. 3. Initially, the reference current amplitude for both the outputs are at 25 A, at t=0.1 s the reference current amplitudes for the converter output terminals u and v are changed to 30 A and 20 A respectively. It can be seen during this step change; the converter can operate both the output currents independently (see Fig 3c and 3d).

Also, noted that the CMOM converter is capable of generating multilevel output voltages across the terminal u and v independently (see Fig. 3a and 3b). A reduction in the output voltage level of terminal v (from 5 to 3 level) is observed, which is due to the decrease in the amplitude of the current reference [24]. The MPC control algorithm enhances dynamic performance of the converter by reflecting the sudden change in current reference in its output terminals without introducing any delay in the converter. It is also able to control the voltage and current independently.

#### B. Case II (Variable phase angle mode)

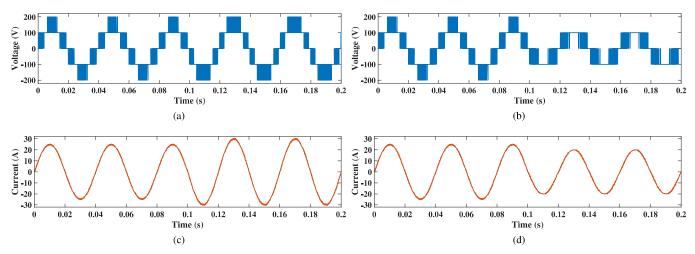

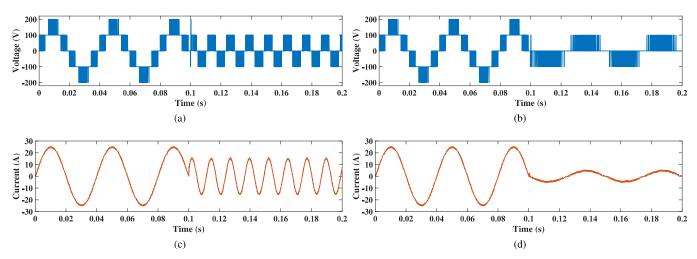

In this study, the converter output voltage terminals u and v generate different current phase angles at fixed amplitude (25 A) and frequency (50 Hz). The dynamic behavior of the voltage and current are shown in Fig. 4. At t=0.1 s, the reference current phase angles for the output converter terminal u and v is changed from an initial state of  $0^{\circ}$  to  $45^{\circ}$  and  $15^{\circ}$  respectively (see Fig. 4c and 4d). It can be noted that the CMOM converter can operate two loads independently with different phase angles.

#### C. Case III (Variable output mode)

In this study, the converter terminals u and v generate different outputs (variable amplitude, frequency, and phase angle) independently. In Fig. 5, the output voltage and current waveforms are shown for both the terminals. Initially, the current on both the output terminals is observed at 25 A, 50 Hz,  $0^{\circ}$ . At t=0.1 s, the reference current parameters for converter output terminals u and v are changed to 15 A, 80 Hz,  $30^{\circ}$  and 5 A, 20 Hz,  $180^{\circ}$  respectively.

Observe that the operation of the CMOM converter is in three-level, implies the usage of a single converter cell with

Fig. 3. Simulation results of Case I (Variable amplitude mode): (a) Output voltage of terminal u, (b) Output voltage of terminal v, (c) Output current of terminal u, (d) Output current of terminal v.

Fig. 4. Simulation results of Case II (Variable phase angle mode): (a) Output voltage of terminal u, (b) Output voltage of terminal v, (c) Output current of terminal u, (d) Output current of terminal v.

Fig. 5. Simulation results of Case III (Variable output mode): (a) Output voltage of terminal u, (b) Output voltage of terminal v, (c) Output current of terminal u, (d) Output current of terminal v.

other by-passed during the operation. Such operations are inherently achievable by MPC control algorithm as they operate through minimizing current error using switching states. The output current waveforms of terminal u and v are shown in Fig. 5c and 5d.

In brief, the MPC algorithm can control the two output terminals independently, and the two output can operate with different amplitude, frequency, and phase angle.

#### IV. CONCLUSION

In this paper, a novel CMOM converter topology is presented. The proposed topology provides multiple output voltages with a reduced number of power switches. The output voltages are controlled in-terms of amplitude, frequency and phase angle independently. MPC algorithm is devised to optimise the control objective. The algorithm also enhances the performance of CMOM converter without introducing a delay in the system during a load change. The simulation results prove the effectiveness of the proposed converter outputs terminal to operate at any voltage independently.

#### ACKNOWLEDGMENTS

The Nanyang Technological University has supported this work under project M4082236.040.

#### REFERENCES

- J. Rodríguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Transactions on Industrial Electronics*, 2002.

- [2] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-voltage multilevel converters State of the art, challenges, and requirements in Industrial applications," *IEEE Transactions on Industrial Electronics*, 2010.

- [3] F. Z. Peng, W. Qian, and D. Cao, "Recent advances in multilevel converter/inverter topologies and applications," in 2010 International Power Electronics Conference - ECCE Asia -, IPEC 2010, 2010.

- [4] I. Colak, E. Kabalci, and R. Bayindir, "Review of multilevel voltage source inverter topologies and control schemes," 2011.

- [5] A. Nabae, I. Takahashi, and H. Akagi, "A New Neutral-Point-Clamped PWM Inverter," *IEEE Transactions on Industry Applications*, 1981.

- [6] T. A. Meynard, H. Foch, P. Thomas, J. Courault, R. Jakob, and M. Nahrstaedt, "Multicell converters: Basic concepts and industry applications," *IEEE Transactions on Industrial Electronics*, 2002.

- [7] P. W. Hammond, "A new approach to enhance power quality for medium voltage AC drives," *IEEE Transactions on Industrical Electronics*, 1997.

- [8] A. Lesnicar and R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range," in 2003 IEEE Bologna PowerTech - Conference Proceedings, 2003.

- [9] G. P. Adam, K. H. Ahmed, S. J. Finney, and B. W. Williams, "Modular multilevel converter for medium-voltage applications," in 2011 IEEE International Electric Machines and Drives Conference, IEMDC 2011, 2011.

- [10] J. Wen and K. Ma Smedley, "Synthesis of multilevel converters based on single- and/or three-phase converter building blocks," *IEEE Transactions* on *Power Electronics*, 2008.

- [11] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," 2010.

- [12] P. Lezana and G. Ortiz, "Extended operation of cascade multicell converters under fault condition," *IEEE Transactions on Industrial Electronics*, 2009.

- [13] E. Babaei, S. Laali, and Z. Bayat, "A Single-Phase Cascaded Multi-level Inverter Based on a New Basic Unit With Reduced Number of Power Switches," *IEEE Transactions on Industrial Electronics*, vol. 62, pp. 922–929. feb 2015.

- pp. 922–929, feb 2015.

[14] J. I. Rodriguez and S. B. Leeb, "A multilevel inverter topology for inductively coupled power transfer," *IEEE Transactions on Power Electronics*, 2006.

- [15] A. Alesina and M. G. B. Venturini, "Analysis and Design of Optimum-Amplitude Nine-Switch Direct AC–AC Converters," *IEEE Transactions* on Power Electronics, 1989.

- [16] P. Wheeler, L. Xu, L. Meng Yeong, L. Empringham, C. Klumpner, and J. Clare, "A review of Multi-level Matrix Converter topologies," Power Electronics, Machines and Drives, 2008. PEMD 2008. 4th IET Conference on, 2008.

- [17] A. Bouscayrol, B. Francois, P. Delarue, and J. Niiranen, "Control implementation of a five-leg ac-ac converter to supply a three-phase induction machine," *IEEE Transactions on Power Electronics*, 2005.

- [18] K. Oka and K. Matsuse, "A nine-switch inverter for driving two AC motors independently," *IEEJ Transactions on Electrical and Electronic Engineering*, 2007.

- [19] T. Kominami and Y. Fujimoto, "A novel nine-switch inverter for independent control of two three-phase loads," in *Conference Record* - IAS Annual Meeting (IEEE Industry Applications Society), 2007.

- [20] A. Fatemi, M. Azizi, M. Mohamadian, A. Yazdian Varjani, and M. Shah-parasti, "Single-phase dual-output inverters with three-switch legs," *IEEE Transactions on Industrial Electronics*, 2013.

- [21] S. M. Dehghan, M. Mohamadian, A. Yazdian, and F. Ashrafzadeh, "Dual-input dual-output z-source inverter," in 2009 IEEE Energy Conversion Congress and Exposition, ECCE 2009, 2009.

- [22] N. Deshmukh, R. Thombare, M. Waware, and D. More, "An extended dual input dual output three level Z source inverter with improved switch loss reduction technique," *Journal of Electrical Systems and Information Technology*, 2016.

- [23] P. Enjeti and W. Shireen, "Advanced programmed PWM modulator for inverters which simultaneously eliminates harmonics and rejects DC link voltage ripple," Conference Proceedings - IEEE Applied Power Electronics Conference and Exhibition - APEC, 1990.

- [24] J. Haruna, "A novel three-level inverter which can drive two pmsms," IET Conference Proceedings, pp. 0273–0273(1), January 2014.