### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

## Development of advanced PWM inverter with soft switching technique for brushless DC motor variable speed drives systems

Pan, Zhi Yang

2006

Pan, Z. Y. (2006). Development of advanced PWM inverter with soft switching technique for brushless DC motor variable speed drives systems. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/3453

https://doi.org/10.32657/10356/3453

Nanyang Technological University

Downloaded on 09 Mar 2024 09:33:50 SGT

# DEVELOPMENT OF ADVANCED PWM INVERTER WITH SOFT SWITCHING TECHNIQUE FOR BRUSHLESS DC MOTOR VARIABLE SPEED DRIVES SYSTEMS

**PAN ZHI YANG**

SCHOOL OF ELECTRICAL & ELECTRONIC ENGINEERING

NANYANG TECHNOLOGICAL UNIVERSITY

## Development of Advanced PWM Inverter with Soft Switching Technique for Brushless DC Motor Variable Speed Drives Systems

#### Pan Zhi Yang

#### School of Electrical & Electronic Engineering

A Thesis submitted to Nanyang Technological University in fulfillment of the requirement for the degree of Doctor of Philosophy

#### **Acknowledgements**

I wish to express my sincere gratitude to Nanyang Technological University (NTU) for giving me scholarship to pursue Ph. D degree. I will also express the sincere appreciation to my supervisor, Associate Professor Luo Fang Lin (DR), for his invaluable guidance, help and encouragement throughout my research work.

Thanks are also due to all research students in Electric Power Research Lab (EPRL), for their helpful advice and stimulative discussions. My gratitude is extended to the technicians in EPRL, Mr. Yeoh Tiow Koon, Mrs. Chew-Sim Annie and Mr. Lee Ting Yeng, for giving me effective technical support during the experiment.

Finally, I would like to give special thanks to my parents, who provide unceasing understanding, support and encouragement. To them I dedicate my work.

#### **Contents**

| Contents        |                                                | i   |

|-----------------|------------------------------------------------|-----|

| Summary         |                                                | iv  |

| List of Figures |                                                | vi  |

| List of Tables  |                                                | ix  |

| List of Abbrev  | iations                                        | X   |

| List of Princip | le Symbols                                     | xii |

| Chapter 1       | Introduction                                   | 1   |

| 1.1 Backg       | round                                          | 1   |

| 1.2 Conve       | entional Voltage Source Inverter               | 2   |

| 1.3 Introd      | uction to Soft-switching Inverter              | 5   |

| 1.4 Contro      | oller                                          | 7   |

| 1.5 Objec       | tives and Major Contributions                  | 8   |

| 1.6 Organ       | ization of this thesis                         | 10  |

| Chapter 2       | Brushless DC Motor                             | 12  |

| 2.1 Opera       | tion Principle                                 | 12  |

| 2.2 Contro      | oller                                          | 16  |

| 2.2.1 (         | Controller                                     | 16  |

| 2.2.2 \$        | Speed sensor                                   | 18  |

| 2.2.3 (         | Gate drive for IGBT                            | 23  |

| 2.3 12-sw       | itches Inverter to Reduce Torque Ripple        | 26  |

| 2.3.1 (         | Commutation process with conventional inverter | 26  |

| 2.3.2 (         | Commutation process with 12-switches inverter  | 29  |

|                 | Simulation and experimental results            |     |

| 2.4 Summ        | nary                                           |     |

| Chapter 3       | Resonant DC Link Inverter                      |     |

| 3.1 Litera      | ture Review                                    | 34  |

| 3.1.1 F         | Prototype of resonant DC link inverter         | 34  |

| 3.1.2 I         | mproved resonant DC link inverter              | 37  |

| 3.1.3 (         | Quasi resonant DC link inverter                | 40  |

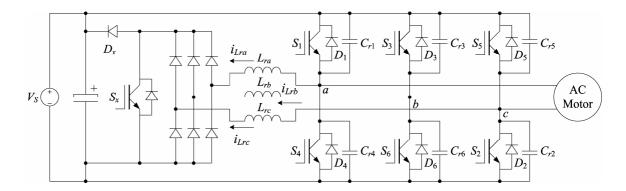

| 3.2 Transf      | former Based Resonant DC Link Inverter         | 43  |

|        | 3.2.1 The structure of the transformer based resonant DC link inverter | 43  |

|--------|------------------------------------------------------------------------|-----|

|        | 3.2.2 Resonant circuit                                                 | 44  |

|        | 3.2.3 Design consideration                                             | 52  |

|        | 3.2.4 Control scheme                                                   | 54  |

|        | 3.2.5 Simulation and experiment                                        | 57  |

| 3      | .3 Summary                                                             | 61  |

| Chapte | er 4 Resonant Pole Inverter                                            | 63  |

| 4      | .1 Literature Review                                                   | 63  |

|        | 4.1.1. Auxiliary resonant commutated pole inverter                     | 63  |

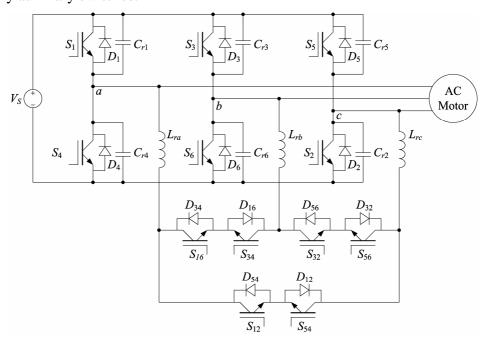

|        | 4.1.2 Y-configured auxiliary resonant snubber inverter                 | 66  |

|        | 4.1.3 Delta-configured auxiliary resonant snubber inverter             | 69  |

|        | 4.1.4 Zero voltage transition resonant pole inverter                   | 71  |

| 4      | .2 Special Design Resonant Pole Inverter for BDCM                      | 72  |

|        | 4.2.1 Topology of the resonant pole inverter                           | 72  |

|        | 4.2.2 Operation principle                                              | 74  |

|        | 4.2.3 Design considerations                                            | 81  |

|        | 4.2.4 Simulation and experimental results                              | 85  |

| 4      | .3 Summary                                                             | 89  |

| Chapte | er 5 Hybrid Control                                                    | 91  |

| 5      | .1 Introduction                                                        | 91  |

| 5      | .2 Model of Drive System                                               | 93  |

| 5      | .3 Current Controller                                                  | 95  |

| 5      | .4 Speed Controller                                                    | 97  |

|        | 5.4.1 PI controller for the speed loop                                 | 97  |

|        | 5.4.2 Fuzzy logic controller for the speed loop                        |     |

|        | 5.4.3 Switching controller                                             | 103 |

| 5      | .5 Implementation and Experimental Results                             | 105 |

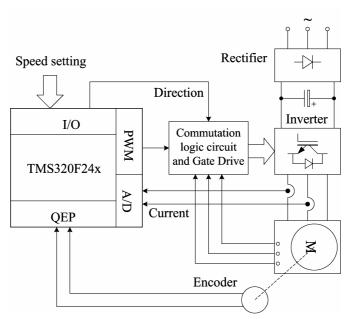

|        | 5.5.1 Structure of the experimental system                             | 105 |

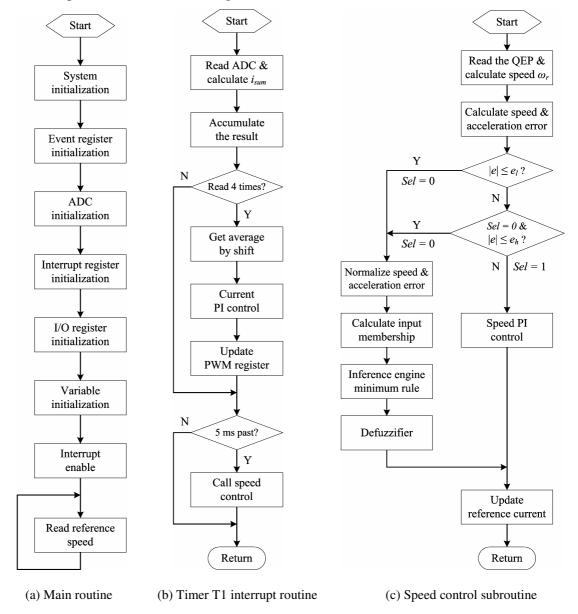

|        | 5.5.2 Software introduction                                            | 106 |

|        | 5.5.3 Experimental results                                             | 110 |

| 5      | .6 Summary                                                             | 113 |

| Chapte | er 6 SSRC Prediction Technique                                         | 114 |

| 6      | .1 Introduction                                                        | 114 |

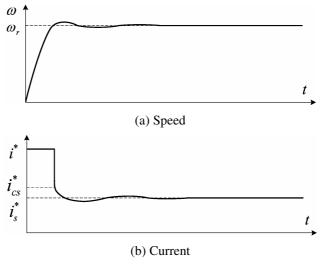

|        | .2 The Structure of the System                                         |     |

|        | 3 Steady State Reference Current Estimator                             | 118 |

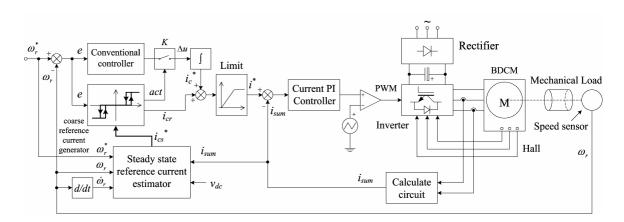

| 6.3.1 The architecture of the SSRC estimator                           | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3.2 Training the neural network                                      | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

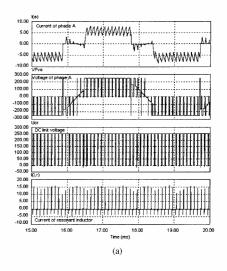

| 6.4 Implementation and Experimental Results                            | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.4.1 Structure of the experimental system                             | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.4.2 Software introduction                                            | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.4.3 Experimental results                                             | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.5 Summary                                                            | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| oter 7 Conclusion and Recommendation                                   | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.1 Conclusion                                                         | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.2 Recommendation                                                     | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| or's Publications                                                      | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ography                                                                | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| endix                                                                  | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A. The ABEL Source Code for Commutation Logical Circuit                | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B. Implementation of QEP Generator Circuit                             | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

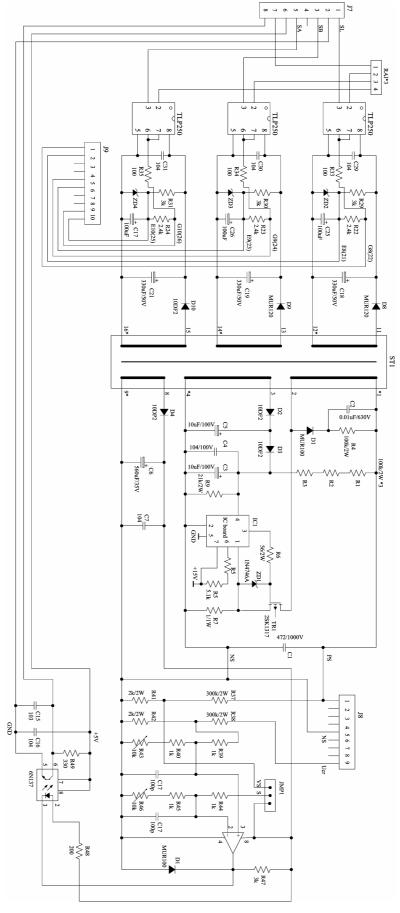

| C. Main Drive Board for the Inverter                                   | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D. Solution of the Equation 3-5                                        | 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| E. Auxiliary Drive Board for Resonant DC Link Inverter                 | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F. Solution of the Equation 4-6                                        | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| G. Source Code of the Hybrid Controller                                | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| H. Novel Soft-Switching Inverter for Brushless DC Motor Variable Speed | d Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| System                                                                 | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| I. Novel Resonant Pole Inverter for Brushless DC Motor Drive System    | 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| J. Transformer Based Resonant DC Link Inverter for Brushless DC Moto   | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Drive System                                                           | 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ]                                                                      | 6.3.2 Training the neural network  6.4 Implementation and Experimental Results  6.4.1 Structure of the experimental system  6.4.2 Software introduction  6.4.3 Experimental results  6.5 Summary  pter 7 Conclusion and Recommendation  7.1 Conclusion  7.2 Recommendation  mor's Publications  iography  endix  A. The ABEL Source Code for Commutation Logical Circuit  B. Implementation of QEP Generator Circuit.  C. Main Drive Board for the Inverter  D. Solution of the Equation 3-5  E. Auxiliary Drive Board for Resonant DC Link Inverter.  F. Solution of the Equation 4-6.  G. Source Code of the Hybrid Controller  H. Novel Soft-Switching Inverter for Brushless DC Motor Variable Speed System  J. Transformer Based Resonant DC Link Inverter for Brushless DC Motor Drive System  J. Transformer Based Resonant DC Link Inverter for Brushless DC Motor Drive System |

#### Summary

Permanent magnet brushless DC motor (BDCM) has been widely used in industrial applications because of its low inertia, fast response, high power density, high reliability and less maintenance. It exhibits the operating characteristics of a conventional commutated DC permanent magnet motor but eliminates the mechanical commutator and brushes. Hence many problems associated with brushes are eliminated such as radiofrequency (RF) interfenence and sparking which is the potential source of ignition in inflammable atmosphere. BDCM is usually supplied by a hard-switching PWM inverter. However switching power losses increase with the increasing of switching frequency. In order to reduce the switching power losses, many soft switching inverters have been designed. Unfortunately, there are many drawbacks, such as high device voltage stress, large DC link voltage ripple, discrete pulse modulation, complex control scheme and so on. On the other hand, the majority of soft-switching inverters proposed in the recent decades have been aimed at the induction motor drive applications. So research on novel topologies of soft-switching inverter and special control circuit for BDCM drive systems is very important.

Soft switching operation of power inverter has attracted much attention in recent decades. In electric motor drive applications, soft-switching inverters are usually classified in three categories, namely resonant pole inverters, resonant DC link inverters and resonant AC link inverters. Resonant AC link inverter is not suitable to BDCM drives. Resonant DC link inverter and resonant pole inverter are all applicable to BDCM. In medium power applications, the resonant DC link concept offered a practical and reliable way to reduce commutation losses and to eliminate individual snubbers. Resonant pole inverter has the disadvantage containing more number of additional components than that of resonant DC link inverter, however there is no conduction path auxiliary switches and its normal operation is totally the same as hard switching inverter. In this thesis, two novel topologies of resonant DC link inverter and resonant pole inverter for BDCM drive system are proposed. These inverters possess the advantage of low switching power loss, low inductor power loss, low DC link voltage ripple, small device voltage stress, simple control scheme, eliminating a stiff DC link capacitor bank that is center-tapped.

The main idea of fuzzy logic control is to use the control ability of human being which includes experience and intuition so the nature of the controller has adaptive characteristics that can achieve robust response to a system with uncertainty, parameter variation, and load disturbance. PI controller has the advantage of fast response especially in motor starting but it will introduce overshoot and oscillation. The fuzzy logic controller can solve these problems while it is slower response than that of PI controller. To utilize the advantages of both PI and fuzzy logic controllers to provide better response than any one controller only, one hybrid controller with fuzzy logic and PI will be introduced in this thesis.

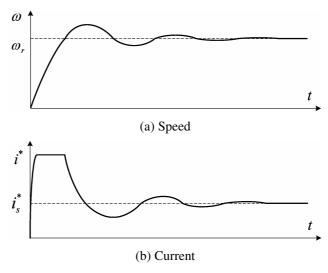

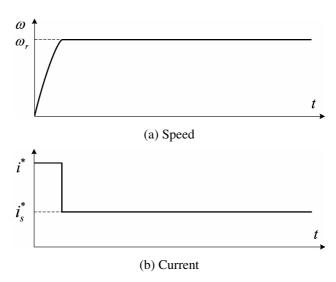

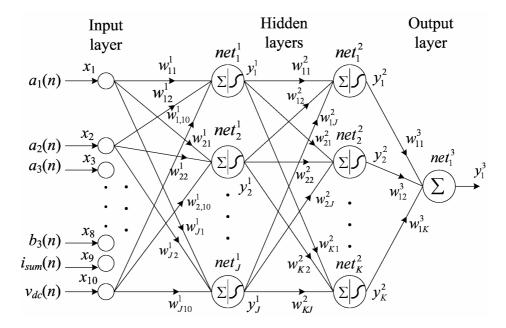

A variable speed electric drive system is normally controlled by a speed/current double closed-loop control system. In conventional control system, during starting, the current reaches its maximum value quickly which contributes to the fast response of the system as the motor runs with maximum acceleration. When the motor reaches the desired speed, the current can not be reduced to its steady state value immediately; it needs time to settle. Normally overshoot and oscillation are inevitable, settling time are multiple that of the starting time. If current reaches its maximum value immediately during starting and when the motor reaches desired speed, the current skips to its steady state value at the same time and the motor runs at the desired speed, the starting time is shortest and the settling time is only the starting time. If the motor reaches desired speed while the current can only skip to around the steady state value, there is oscillation too, but the oscillation is smaller than that of conventional control system and the settling time can be reduced greatly, too. To achieve fast starting, the key is to determine (predict) the steady state reference current (SSRC) during starting. An artificial neural network (ANN) is a computational network, consisting of a number of interconnected processing units (neurons), which is able to learn and represent the unknown dependency relationship between a set of input variables and a set of output variables of a system. By selecting the training patterns (acceleration, speed, current, DC link voltage, reference speed) which cover all conditions (i.e. various DC link voltage, various load, various moment of inertia, various reference speed) to train the neural network, the neural network is then possible to predict the SSRC according to the acceleration, speed, current, DC link voltage, reference speed of the drive system, although the predicted value may be not very accurate. Conventional controller combined with this technique holds the advantages of fast response, little overshoot, little oscillation, robust and so on.

#### **List of Figures**

| Fig. 1-1. The structure of conventional voltage source three-phase inverter            | 2    |

|----------------------------------------------------------------------------------------|------|

| Fig. 1-2. The voltage and current waveforms of power semiconductor switch and          |      |

| freewheeling diode                                                                     | 3    |

| Fig. 1-3. Comparison of hard switching with soft switching                             | 5    |

| Fig. 1-4. The structure of resonant DC link inverter                                   | 6    |

| Fig. 1-5. The construction of resonant pole inverter                                   | 7    |

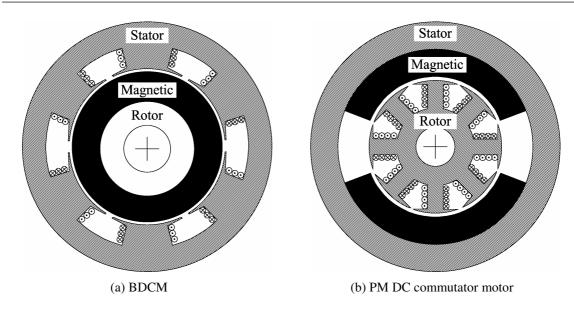

| Fig. 2-1. The structure of brushless DC motor and PM DC commutator motor [78]          | . 13 |

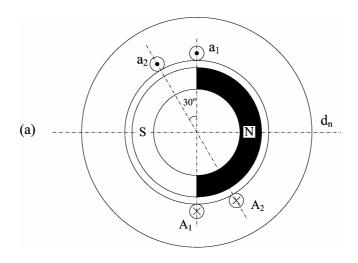

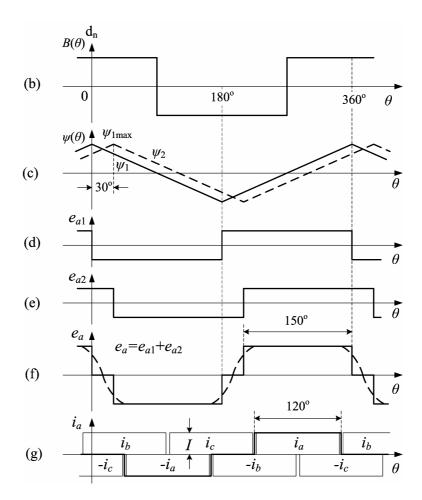

| Fig. 2-2. BDCM with ideal waveforms of flux-density, back EMF and current [78].        | . 15 |

| Fig. 2-3. The structure of controller for BDCM drive                                   | . 17 |

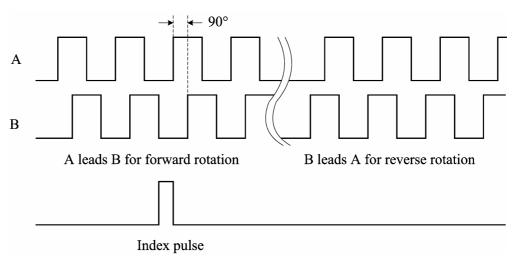

| Fig. 2-4. Quadrature encoder signals                                                   | . 19 |

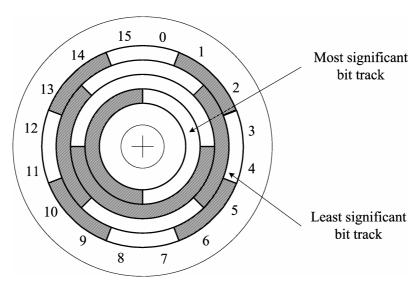

| Fig. 2-5. A 4-bit absolute encoder disk                                                | . 20 |

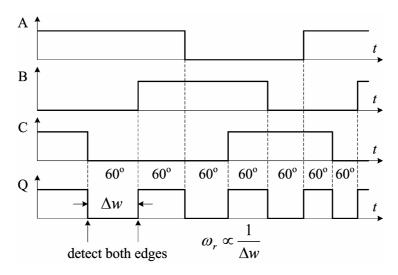

| Fig. 2-6. Hall signal for speed measurement                                            | . 21 |

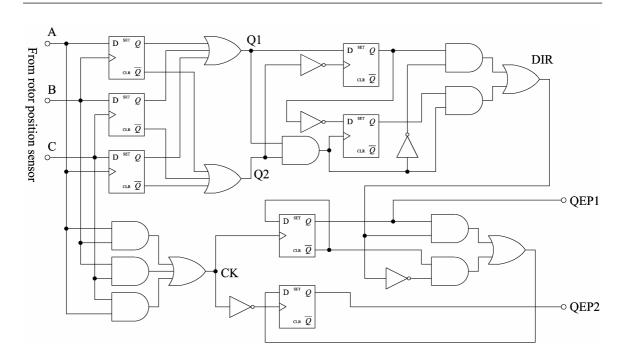

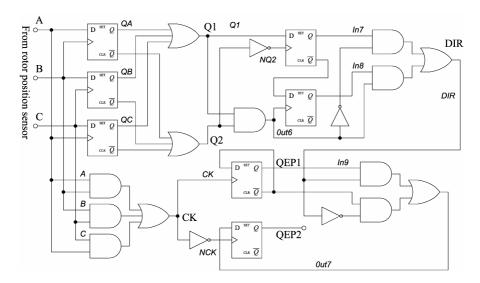

| Fig. 2-7. Circuit for deriving QEP from Hall signal and waveforms                      | . 22 |

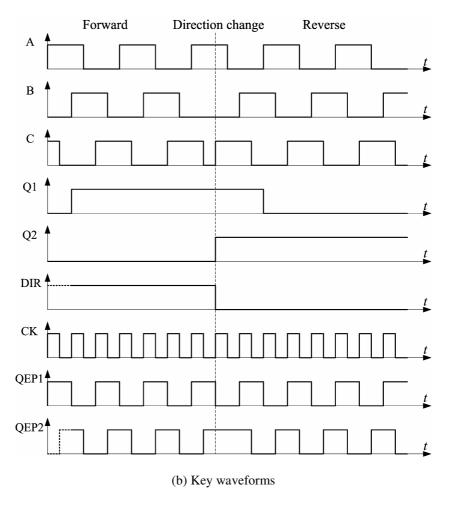

| Fig. 2-8. Gate driver circuit for IGBT                                                 | . 23 |

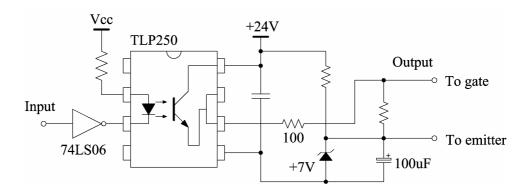

| Fig. 2-9. Gate driver circuit for two switches in one phase leg with bootstrap supply. | . 24 |

| Fig. 2-10. Freewheeling path when switch S1 is turned off                              | . 25 |

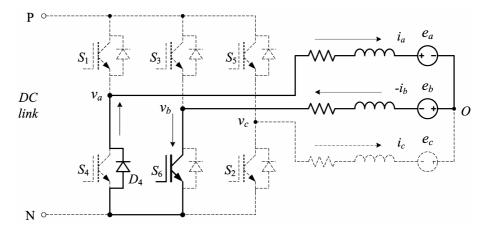

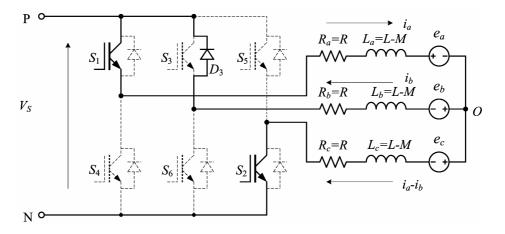

| Fig. 2-11. Equivalent circuit during commutation                                       | . 27 |

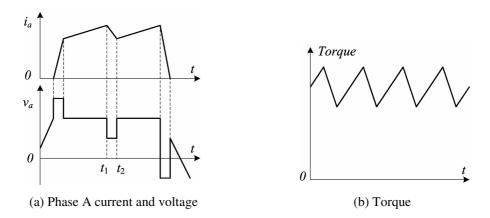

| Fig. 2-12. Waveforms of phase current, phase voltage and torque with conventional      |      |

| inverter                                                                               | . 28 |

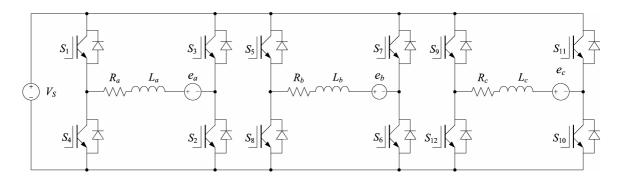

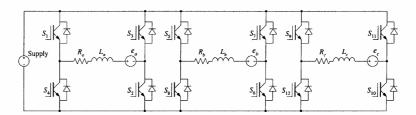

| Fig. 2-13. The topology of 12-switches inverter                                        | . 29 |

| Fig. 2-14. Waveforms of back EMF, phase current and torque with 12-switches            |      |

| inverter                                                                               | . 30 |

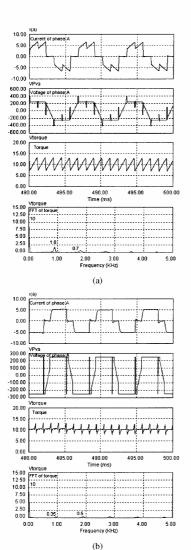

| Fig. 2-15. Simulation result of conventional inverter versus that of 12-switches       |      |

| inverter                                                                               | . 32 |

| Fig. 2-16. Experimental result of conventional inverter versus12-switches inverter     | . 32 |

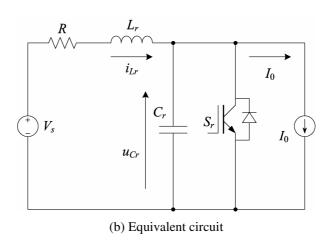

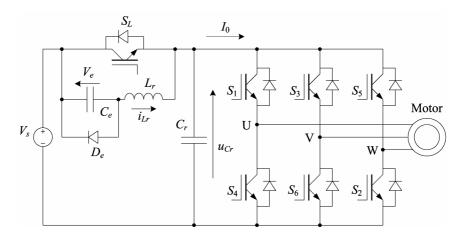

| Fig. 3-1. Topology of resonant DC link inverter and its equivalent circuit             | . 35 |

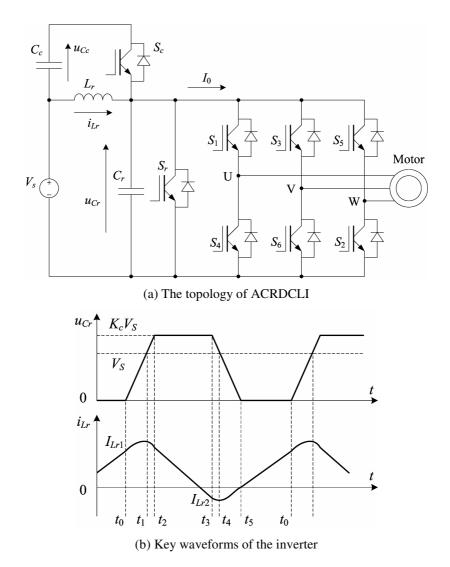

| Fig. 3-2. The topology of ACRDCLI and key waveforms                                    | . 37 |

| Fig. 3-3. The topology of SVCRDCLI                                                     | . 39 |

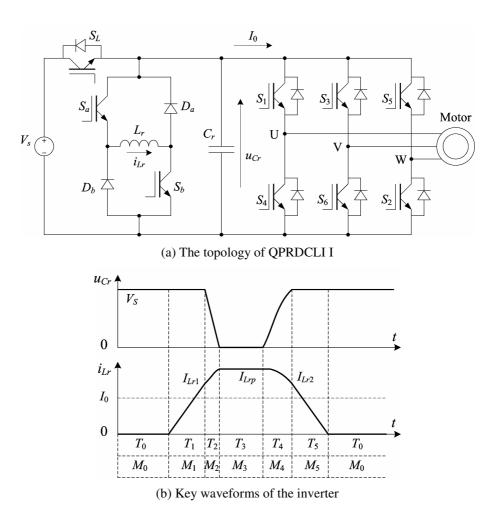

| Fig. 3-4. The topology of QPRDCLI I and its key waveforms                              | . 40 |

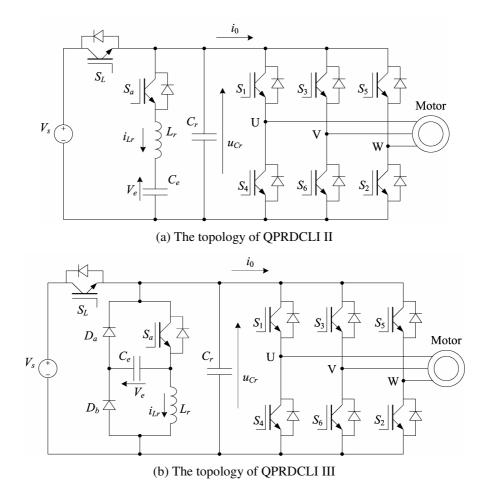

| Fig. 3-5. The topology of QPRDCLI II and III                                           | . 42 |

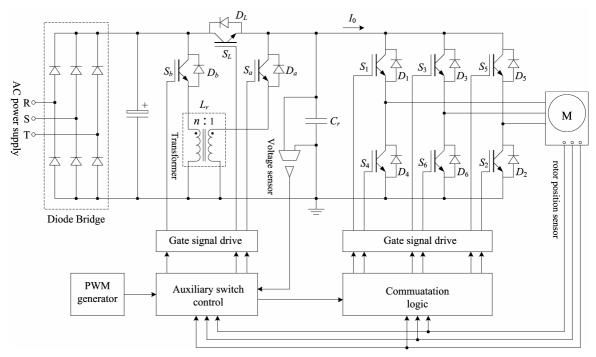

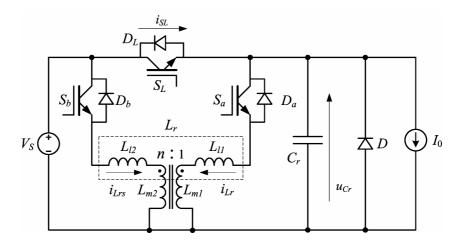

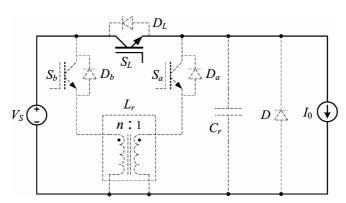

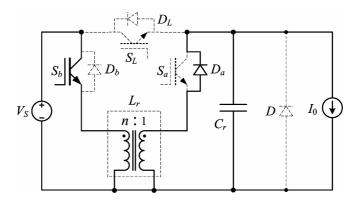

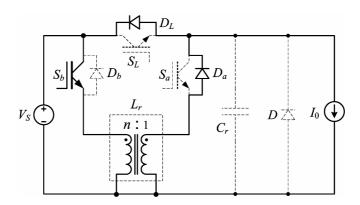

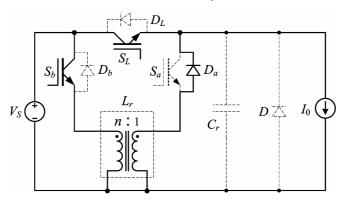

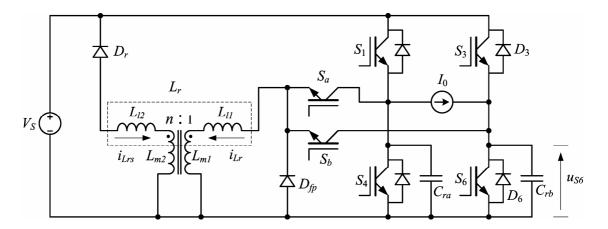

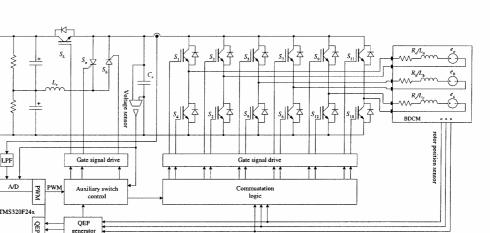

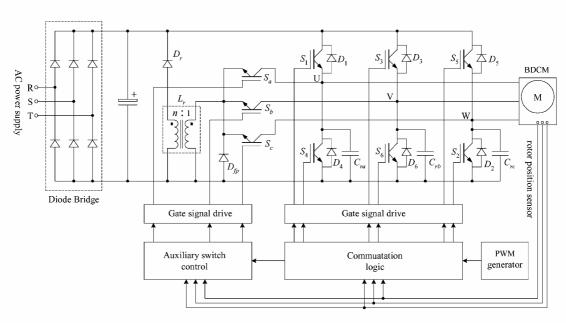

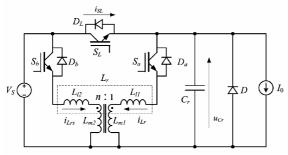

| Fig. 3-6. The structure of the resonant DC link inverter for BDCM drive system                            | 43 |

|-----------------------------------------------------------------------------------------------------------|----|

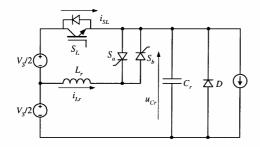

| Fig. 3-7. The equivalent circuit of the inverter                                                          | 44 |

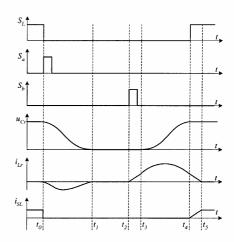

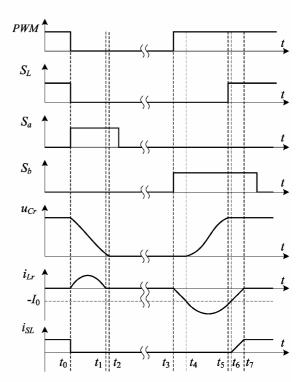

| Fig. 3-8. Key waveforms of the equivalent circuit                                                         | 45 |

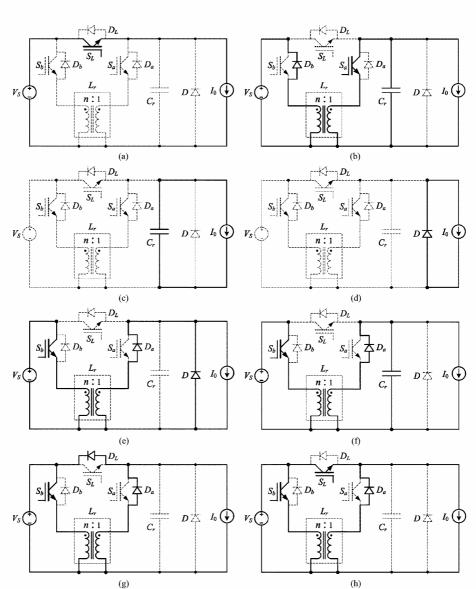

| Fig. 3-9. Equivalent circuit of mode 0                                                                    | 45 |

| Fig. 3-10. Equivalent circuit of mode 1                                                                   | 46 |

| Fig. 3-11. Equivalent circuit of mode 2                                                                   | 47 |

| Fig. 3-12. Equivalent circuit of mode 3                                                                   | 48 |

| Fig. 3-13. Equivalent circuit of mode 4                                                                   | 48 |

| Fig. 3-14. Equivalent circuit of mode 5                                                                   | 49 |

| Fig. 3-15. Equivalent circuit of mode 6                                                                   | 50 |

| Fig. 3-16. Equivalent circuit of mode 7                                                                   | 51 |

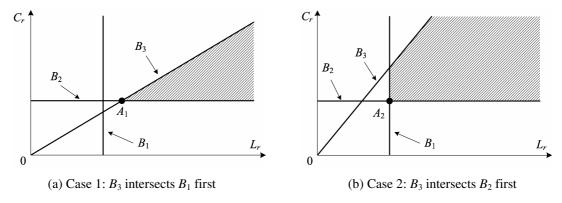

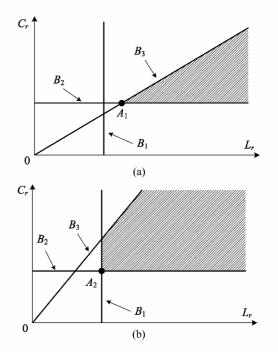

| Fig. 3-17. $L_r$ and $C_r$ selection area                                                                 | 53 |

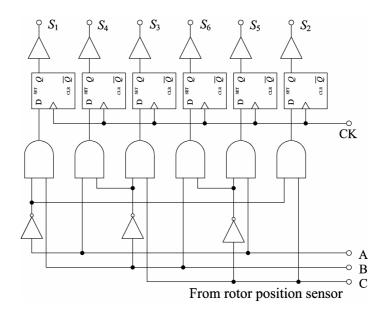

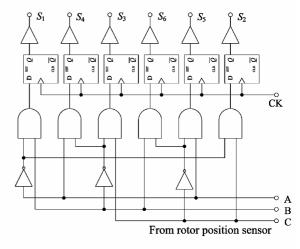

| Fig. 3-18. Commutation logical circuit for main switches                                                  | 55 |

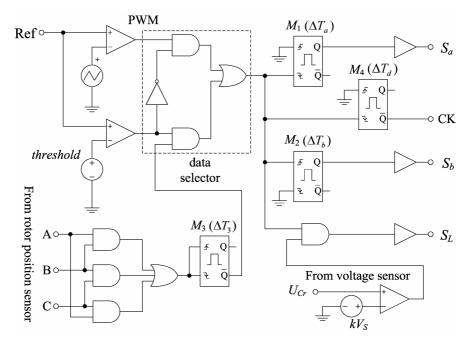

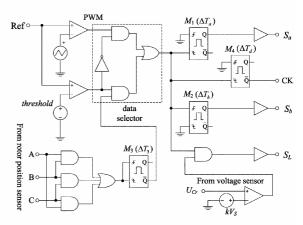

| Fig. 3-19. Control circuit for the auxiliary switches                                                     | 55 |

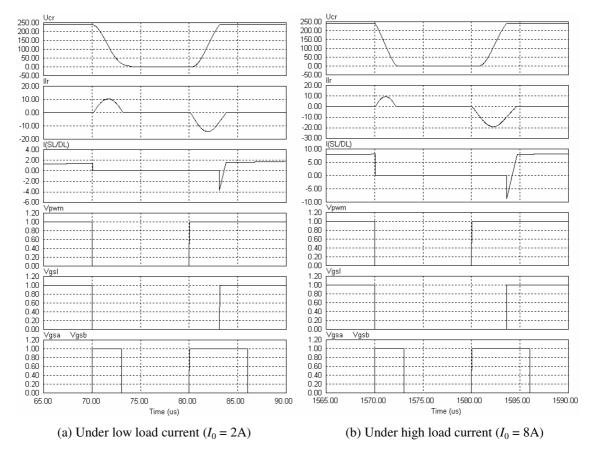

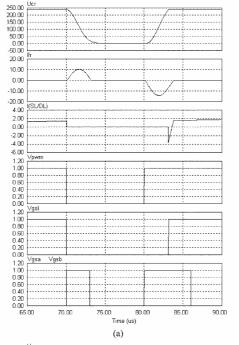

| Fig. 3-20. Waveforms of $u_{Cr}$ , $i_{Lr}$ , $i_{SL}/i_{DL}$ , PWM, auxiliary switches gate signal under |    |

| various load current5                                                                                     | 58 |

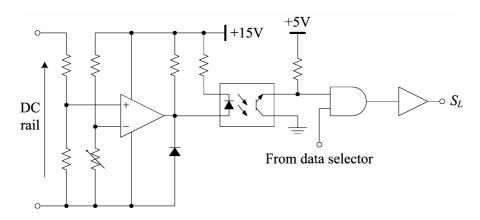

| Fig. 3-21. Auxiliary switch $S_L$ gate signal generator                                                   | 59 |

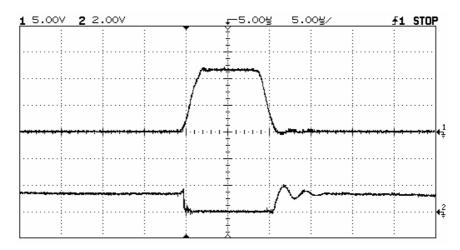

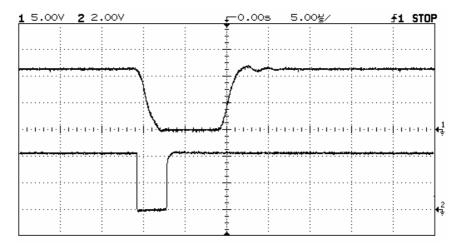

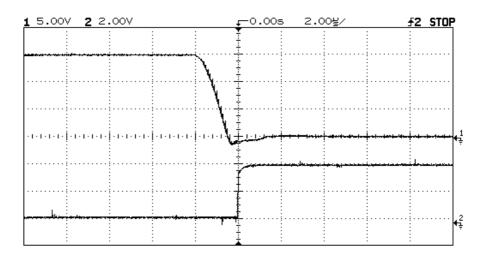

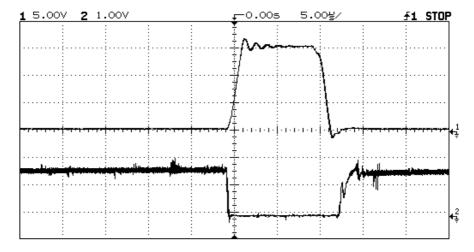

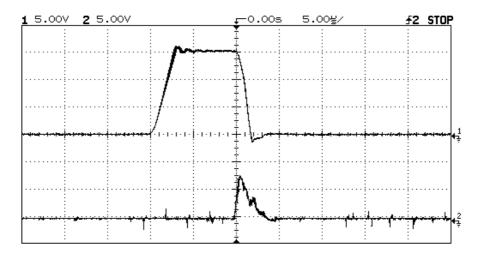

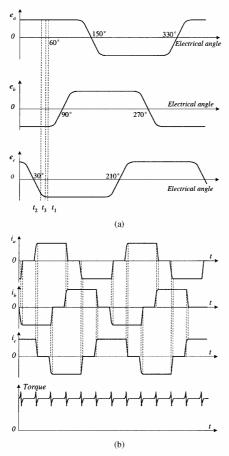

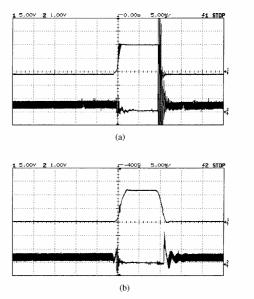

| Fig. 3-22. Experiment results                                                                             | 61 |

| Fig. 4-1. The equivalent circuit of one phase ARCPI                                                       | 64 |

| Fig. 4-2. The key waveform of ARCPI during $S_2 \rightarrow S_1$                                          | 64 |

| Fig. 4-3. The structure of Y-configured auxiliary resonant snubber inverter                               | 66 |

| Fig. 4-4. The single phase version of auxiliary resonant snubber inverter                                 | 67 |

| Fig. 4-5. The key waveform of auxiliary resonant snubber inverter                                         | 68 |

| Fig. 4-6. The structure of $\Delta$ -configured resonant snubber inverter                                 | 70 |

| Fig. 4-7. The structure of resonant snubber inverter with bidirectional auxiliary                         |    |

| switches                                                                                                  | 70 |

| Fig. 4-8. The structure of the ZVT resonant pole inverter                                                 | 71 |

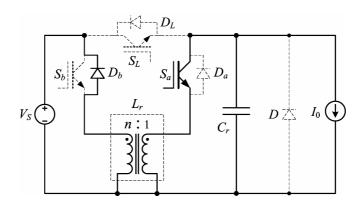

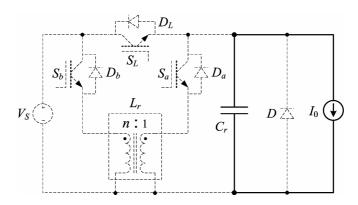

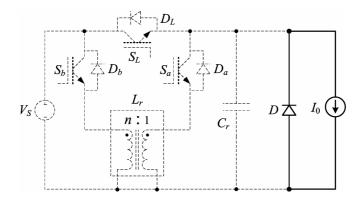

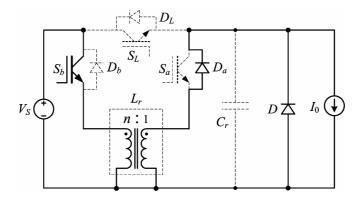

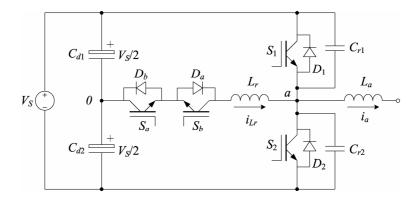

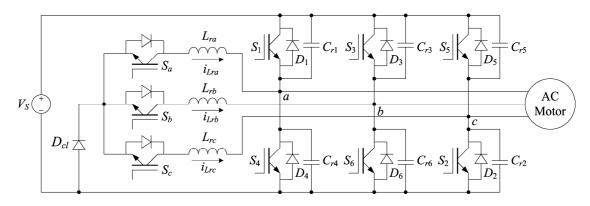

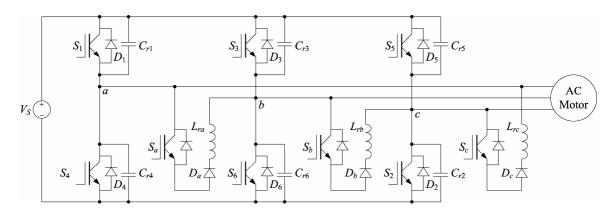

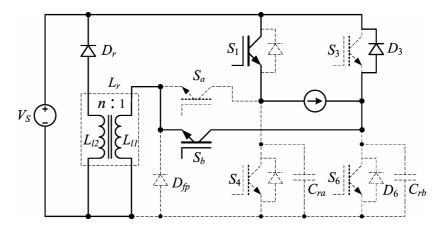

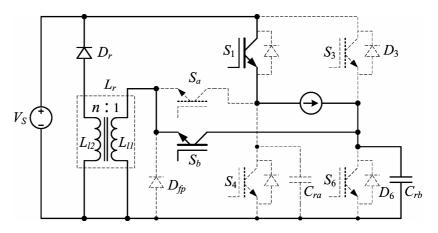

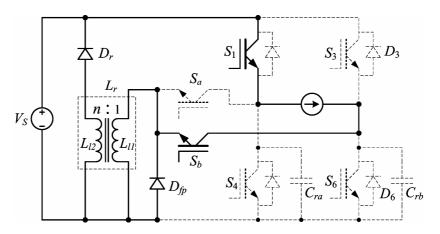

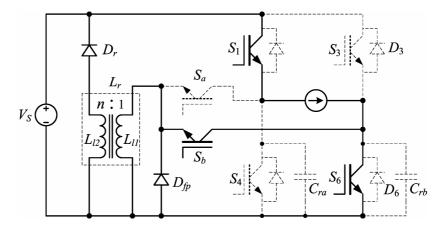

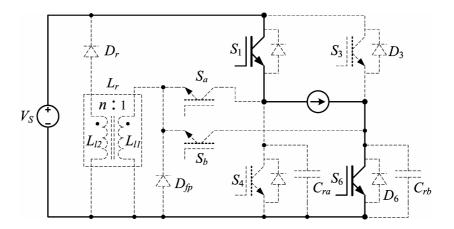

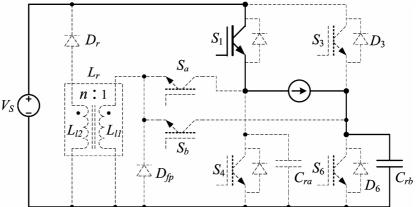

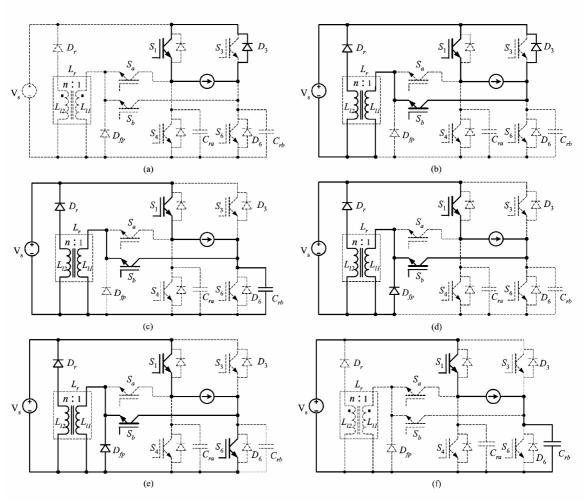

| Fig. 4-9. The resonant pole inverter for BDCM drive system                                                | 73 |

| Fig. 4-10. The equivalent circuit                                                                         | 74 |

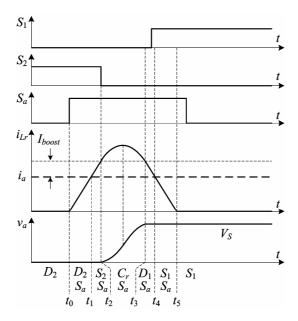

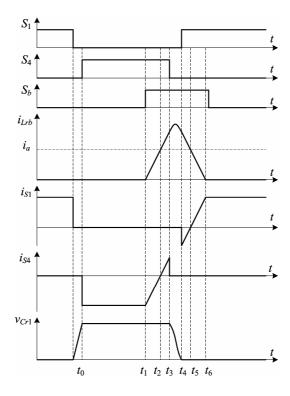

| Fig. 4-11. Key waveforms of the equivalent circuit                                                        | 75 |

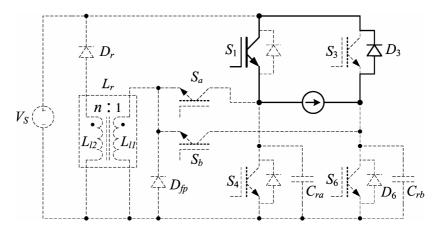

| Fig. 4-12. Equivalent circuit of mode 0                                                                   | 75 |

| Fig. 4-13. Equivalent circuit of mode 1                                                                   | 76 |

| Fig. 4-14. Equivalent circuit of mode 2                                                                   | 77 |

| Fig. 4-15. Equivalent circuit of mode 3                                                                   | 78 |

| Fig. 4-16. Equivalent circuit of mode 4                                                         | 79  |

|-------------------------------------------------------------------------------------------------|-----|

| Fig. 4-17. Equivalent circuit of mode 5                                                         | 80  |

| Fig. 4-18. Equivalent circuit of mode 6                                                         | 80  |

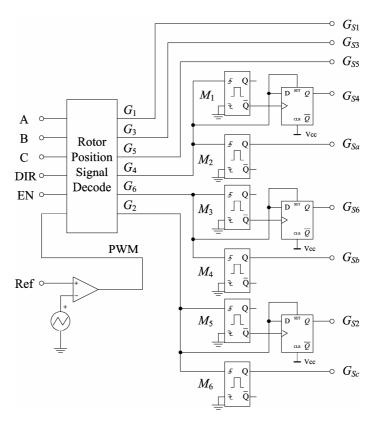

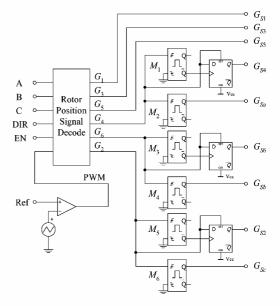

| Fig. 4-19. Gate signal generator circuit                                                        | 83  |

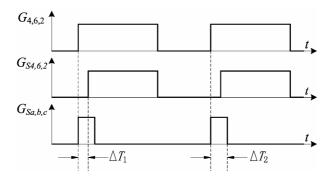

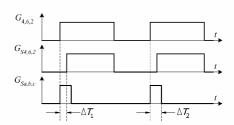

| Fig. 4-20. Gate signals $G_{S4,6,2}$ and $G_{Sa,b,c}$ from $G_{4,6,2}$                          | 84  |

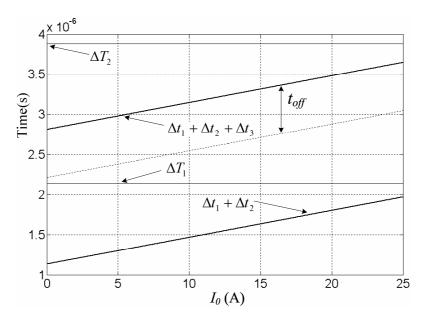

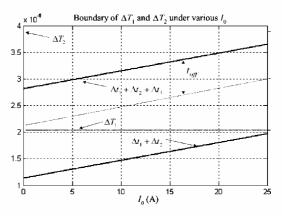

| Fig. 4-21. Boundary of $\Delta T_1$ and $\Delta T_2$ under various load current I0              | 85  |

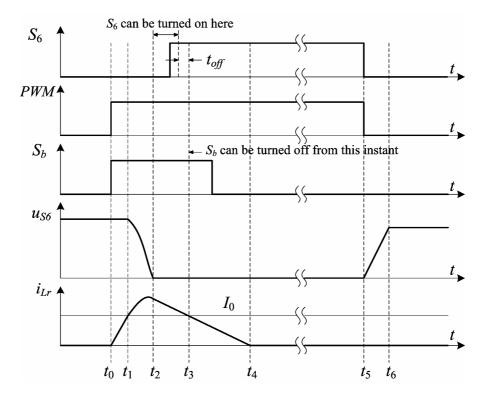

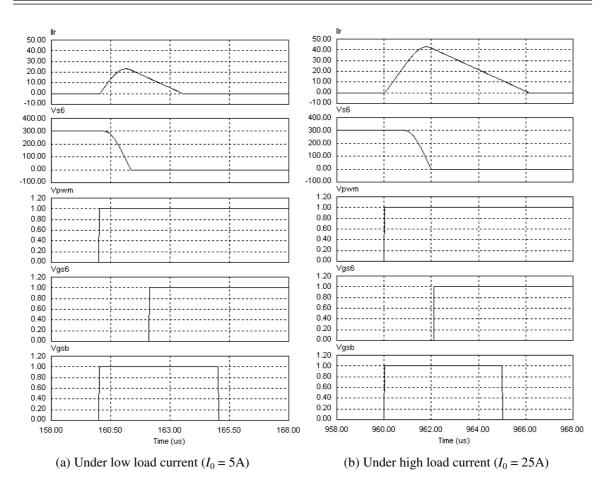

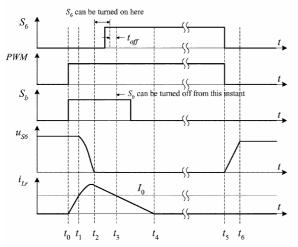

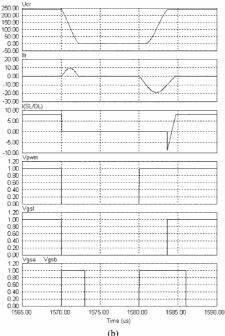

| Fig. 4-22. Simulation waveforms of $i_{Lr}$ , $u_{S6}$ , PWM, $S_6$ and $S_b$ gate signal under |     |

| various load current                                                                            | 86  |

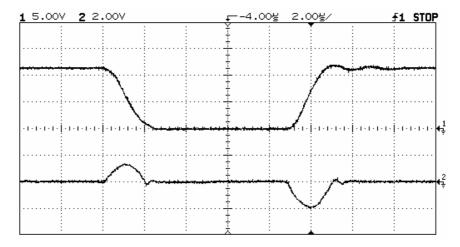

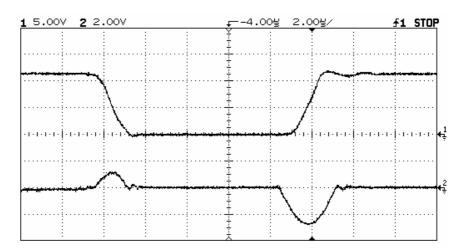

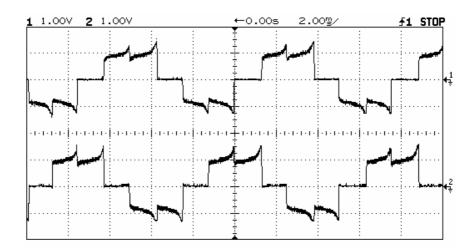

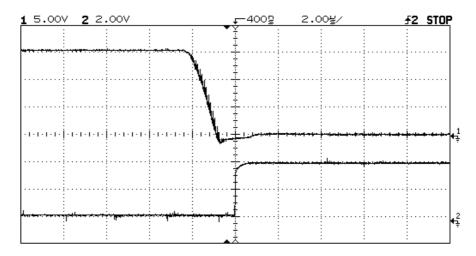

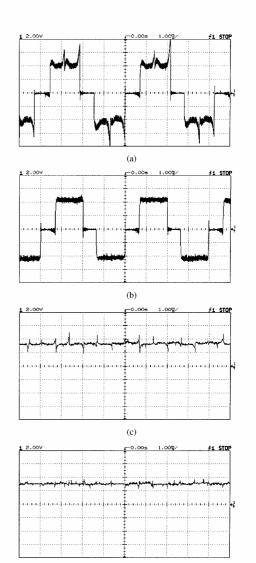

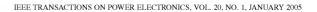

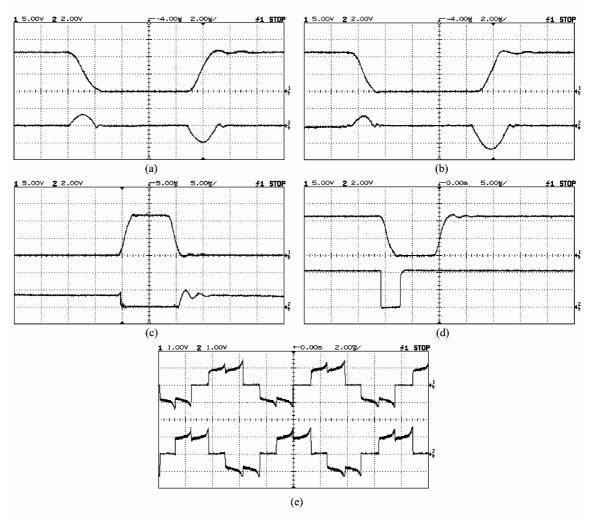

| Fig. 4-23. Experiment waveforms                                                                 | 88  |

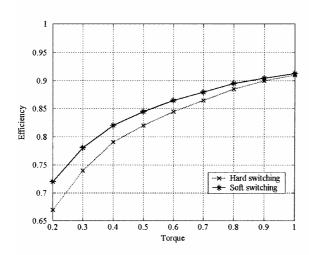

| Fig. 4-24. Efficiency of hard switching and soft switching under various load                   |     |

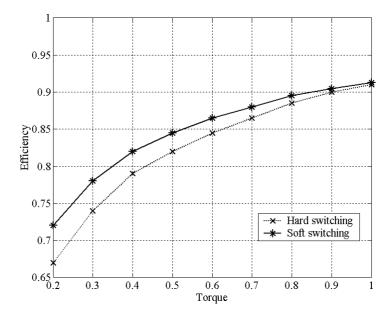

| torque (p.u.)                                                                                   | 89  |

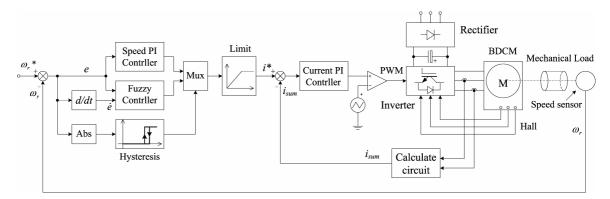

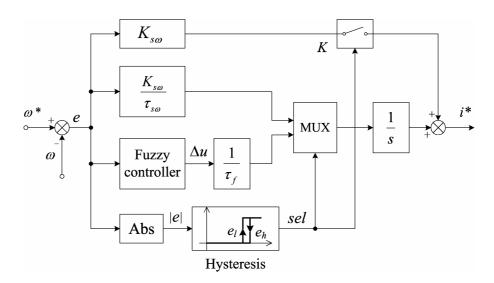

| Fig. 5-1. The structure of control system                                                       | 92  |

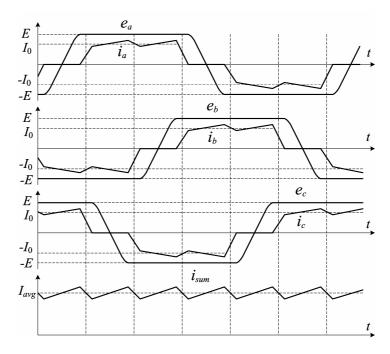

| Fig. 5-2. The waveforms of back EMF and phase currents                                          | 93  |

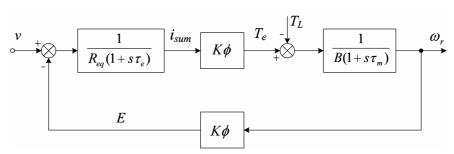

| Fig. 5-3. The block diagram of the PM BDCM                                                      | 94  |

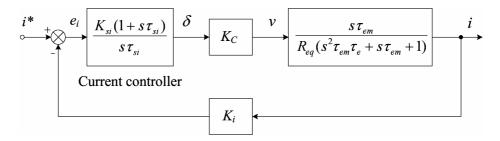

| Fig. 5-4. The current loop for the PM BDCM                                                      | 95  |

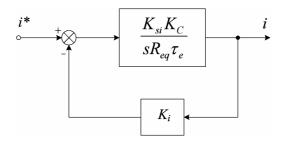

| Fig. 5-5. The simplified current loop for the PM BDCM                                           | 96  |

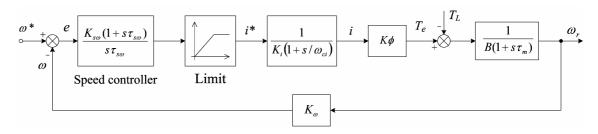

| Fig. 5-6. The speed loop for the PM BDCM                                                        | 97  |

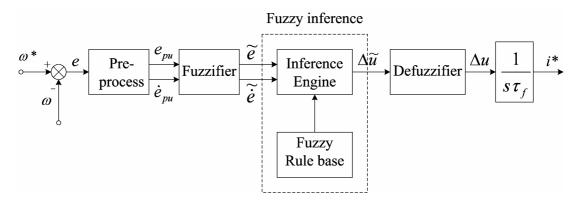

| Fig. 5-7. The structure of fuzzy logic controller                                               | 98  |

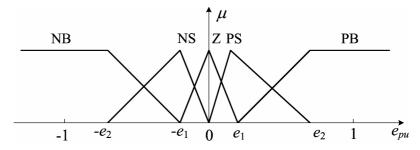

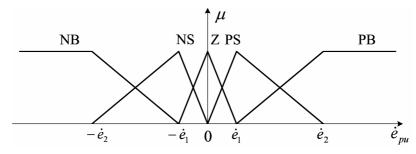

| Fig. 5-8. Membership function of fuzzy input variable                                           | 100 |

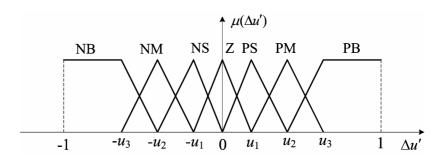

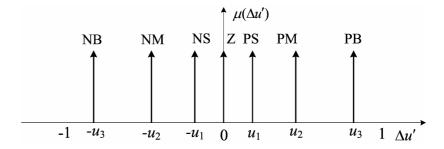

| Fig. 5-9. Membership function of fuzzy output variable $\Delta \tilde{u}$                       | 100 |

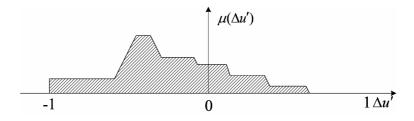

| Fig. 5-10. Output of fuzzy controller $\Delta \tilde{u}$                                        | 102 |

| Fig. 5-11. Output variable $\Delta \tilde{u}$ membership function with crisp value              | 103 |

| Fig. 5-12. Switching speed controller                                                           | 104 |

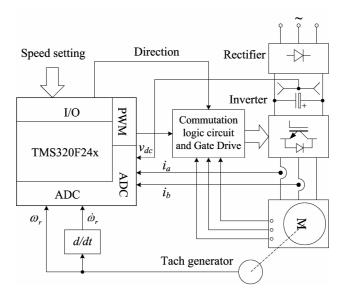

| Fig. 5-13. Structure of the experimental system                                                 | 105 |

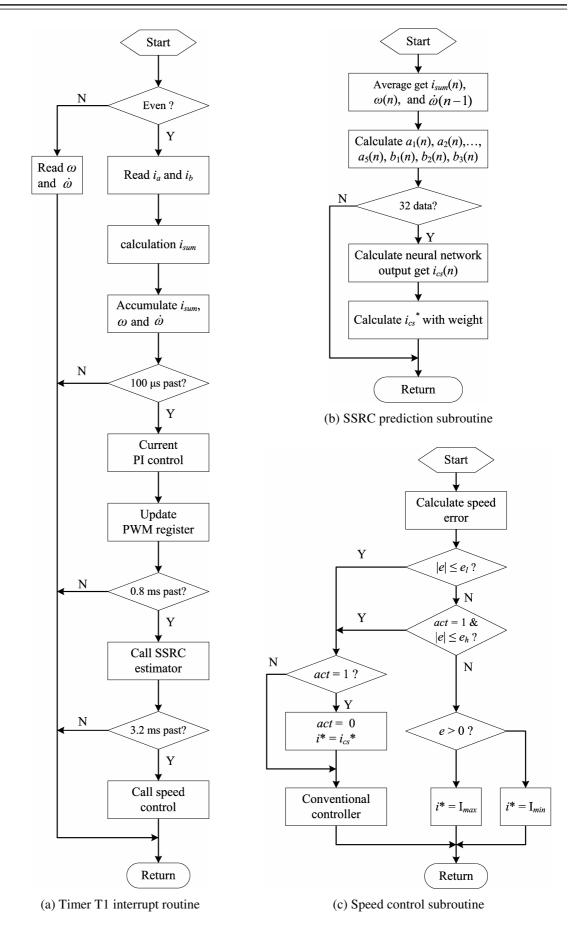

| Fig. 5-14. Flowchart of software                                                                | 107 |

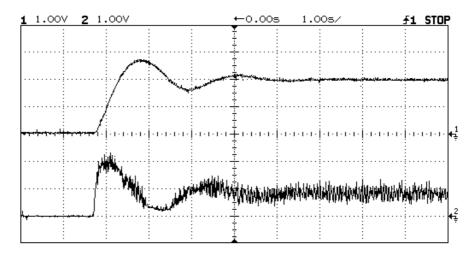

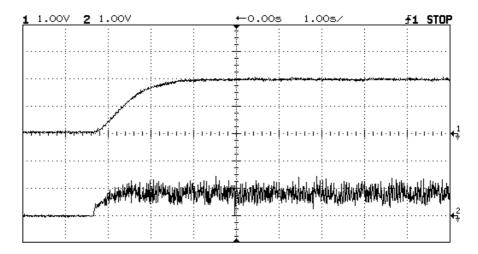

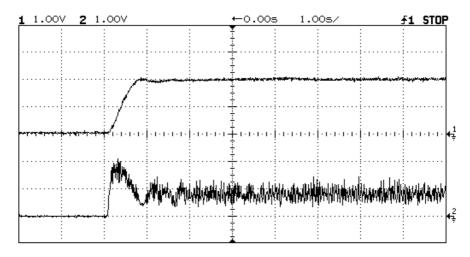

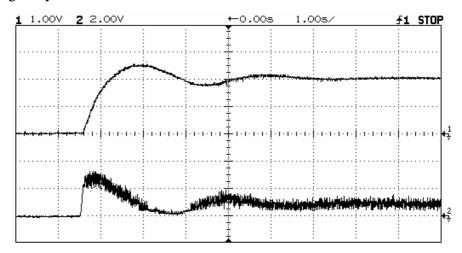

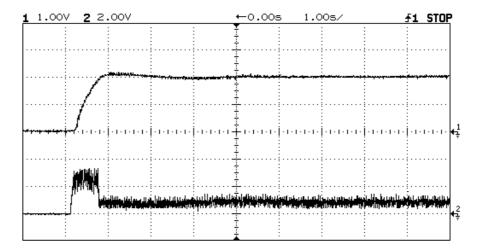

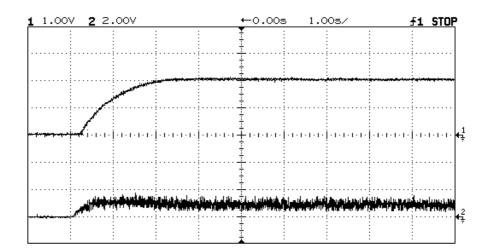

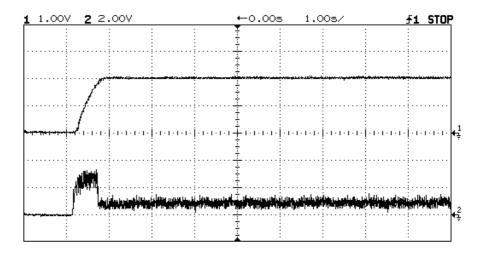

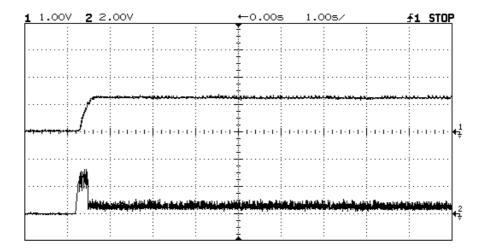

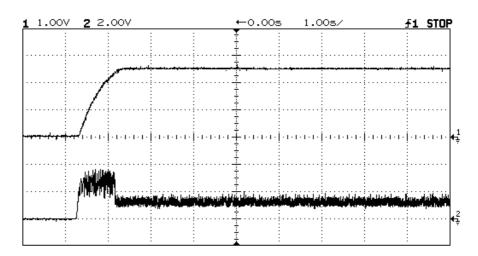

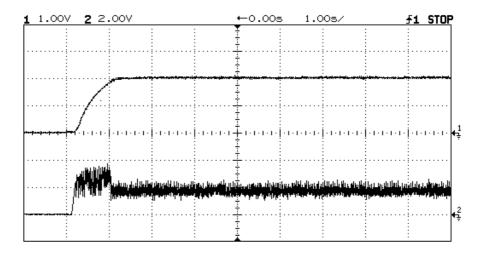

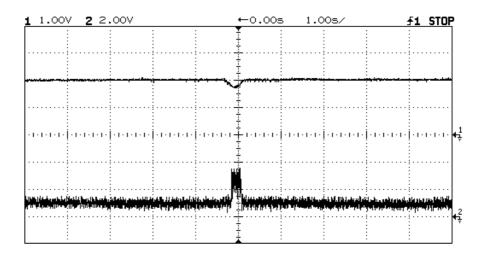

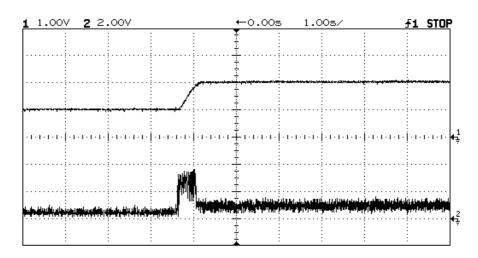

| Fig. 5-15. Experimental waveforms of speed response and DC link current under                   |     |

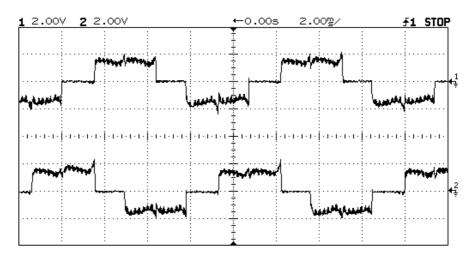

| PI controller only, fuzzy controller only and hybrid controller                                 | 113 |

| Fig. 6-1. Typical speed and current curve of a DC motor drive system                            | 115 |

| Fig. 6-2. Ideal speed and current curve of a DC motor drive system                              | 115 |

| Fig. 6-3. Near ideal speed and current curve of a DC motor drive system                         | 115 |

| Fig. 6-4. The structure of the control system                                                   | 117 |

| Fig. 6-5. The architecture of SSRC estimator                                                    | 119 |

| Fig. 6-6. Structure of the experimental system                                                  | 126 |

| Fig. 6-7. Flowchart of software                                                                 | 128 |

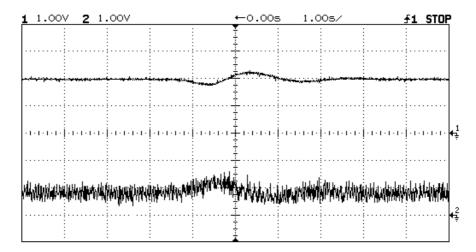

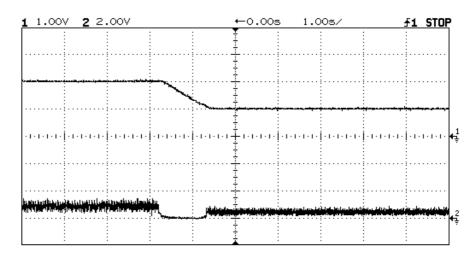

| Fig. 6-8. Experimental waveforms of speed response and DC link current under |    |

|------------------------------------------------------------------------------|----|

| PI and fuzzy control with or without SSRC prediction technique 1             | 33 |

| Fig. A-1. Schematic circuit                                                  | 50 |

| Fig. A-2. Implementation circuit                                             | 50 |

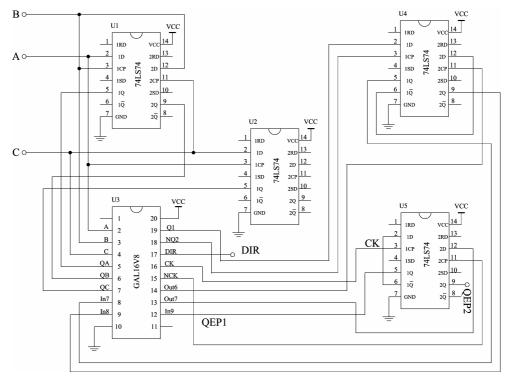

| Fig. A-3. Detail of the IC board in the main drive board                     | 51 |

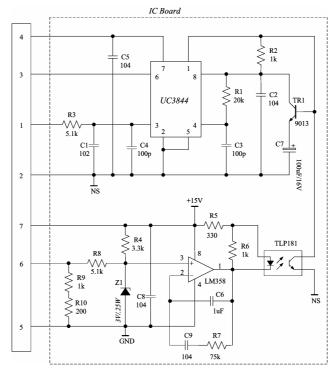

| Fig. A-4. Main drive board for the inverter                                  | 52 |

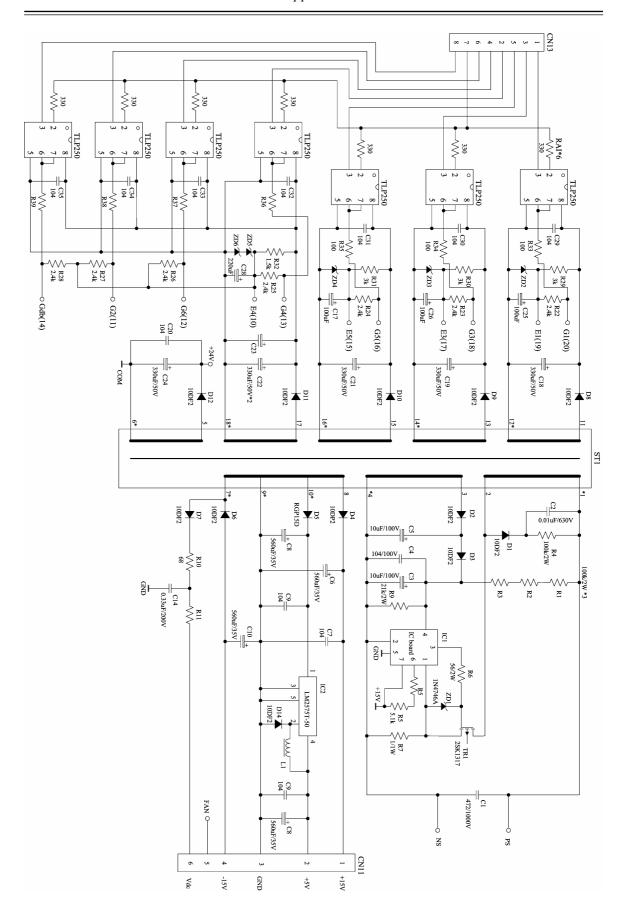

| Fig. A-5. Auxiliary drive board for resonant Dc link inverter                | 56 |

|                                                                              |    |

|                                                                              |    |

|                                                                              |    |

|                                                                              |    |

| List of Tables                                                               |    |

|                                                                              |    |

| Table 2-1 Commutation logic of BDCM                                          | 17 |

#### **List of Abbreviations**

ABEL Advanced Boolean Equation Language

ACRDCLI Actively Clamped Resonant DC Link Inverter

ADC Analog to Digital Converter

AND And logical gate

ANN Artificial Neural Network

ARCPI Auxiliary Resonant Commutated Pole Inverter

BDCM Brushless DC Motor

CK Synchronous Pulse between BDCM Commutation Circuit and

**Control Circuit**

CPLD Complex Programmer Logical Device

CSI Current Source Inverter

DSP Digital Signal Processor

E<sup>2</sup>PROM Electrically Erasable Programmable Read-Only Memory

EMC Electro Magnetic Compatibility

EMF Electromotive Force

EMI Electro Magnetic Interference

GAL Gate Array Logic

IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistor

IPM Intelligent Power Module

JEDEC Joint Electron Device Engineering Council

LED Light-emitting Diode

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MRC Multi-element Resonant Converter

NB Negative big

NM

Negative medium

NOT

Not logical gate

NS

Negative small

OR

Or logical gate

PB

Positive big

PI Proportional Integral

PM Positive medium

PRC Parallel-Resonant Converter

PS Positive small

PWM Pulse Width Modulation

PM Permanent Magnet

QEP Quadrature Encoder Pulse

QRDCLI Quasi Resonant DC Link Inverter

QPRDCLI Quasi Parallel Resonant DC Link Inverter

QRC Quasi-Resonant Converter

RAM Random-access Memory

RDCLI Resonant DC Link Inverter

RF Radio frequency

RPI Resonant Pole Inverter

SCI Serial Communications Interface

SMPS Switching Mode Power Supply

SPRC Series-Parallel Resonant Converter

SRC Series-Resonant Converter

SRM Switch Reluctance Motor

SSRC Steady State Reference Current

SSRS Steady State Reference Speed

SVCRDCLI Source Voltage Clamped Resonant DC Link Inverter

TG Tachometer generator

UPS Uninterruptible power supply

VSI Voltage Source Inverter

Z Zero

ZCS Zero Current Switching

ZVS Zero Voltage Switching

ZVT Zero Voltage Transition

#### **List of Principle Symbols**

a Transformer turn ratio 1: n

$a_1(n) \sim a_5(n)$  Input of the neural network

$a_1A_1$ ,  $a_2A_2$  Coil in BDCM

act conventional controller active signal

$A_{\omega}(s)$  The transfer function of speed loop

B Viscous friction coefficient

$b_1(n), b_2(n), b_3(n)$  Input of the neural network

$B_g$  Air gap flux density

$C_{bs}$  Bootstrap capacitor

$C_c$  Clamping capacitance in ACRDCL inverter

$C_r$  Resonant capacitance

$C_{r1} \sim C_{r6}$  Snubber capacitor

$C_{ra}$ ,  $C_{rb}$ ,  $C_{rc}$  Snubber capacitor

$D_1 \sim D_6$  Build in freewheeling diode of main switches in an inverter

$D_a, D_b$  Auxiliary diode in QPRDCL inverter I

Build in freewheeling diode of auxiliary switch  $S_a$  and  $S_b$

$D_{bs}$  Bootstrap diode

$D_{cl}$  Clamping diode

$D_{fp}$ ,  $D_r$  Auxiliary diode in special design RPI

$D_L$  Build in freewheeling diode of auxiliary switch  $S_L$

E Back EMF of BDCM

*e* Speed error in controller

$\tilde{e}$  Speed error fuzzy variable

$\tilde{\dot{e}}$  Acceleration error fuzzy variable

$e_1, e_2$  Speed error membership function boundary

$\dot{e}_1, \dot{e}_2$  Acceleration error membership function boundary

$e, e_a, e_b, e_c$  Instantaneous phase back EMF of BDCM

$e_{a1}$ ,  $e_{a2}$  Instantaneous phase back EMF of coil  $a_1A_1$  and  $a_2A_2$

$e_h, e_l$  Speed error threshold

$e_i$  Current error

$e_{pu}$  Normalized speed error

$\dot{e}_{pu}$  Normalized acceleration error

$H_i(s)$  The transfer function of current loop

$G_1 \sim G_6$  The output of Monostable flip-flop  $M_1 \sim M_6$

$G_i(s)$  current controller

$G_{S1} \sim G_{S6}$  Gate signal for main switches  $S_1 \sim S_6$

$G_{Sa}$ ,  $G_{Sb}$ ,  $G_{Sc}$  Gate signal for auxiliary switches  $S_a$ ,  $S_b$ ,  $S_c$

$I_0$  Equivalent load current during resonant

$I_{0max}$  Maximum load current

$i, i_a, i_b, i_c$  Instantaneous phase current of BDCM

*i*\* Reference current

$I_{avg}$  Average value of  $i_{sum}$

$I_{boost}$  Preset current threshold in ARCP inverter

$i_{cr}$  Coarse reference current

$i_{cs}^*$  Coarse steady state reference current

$i_{cs}(n)$  Coarse steady state reference current calculated in one sample period

$i_{DL}$  Current of freewheeling diode  $D_L$

$I_{offset}$  Current offset

$i_{Lr}$  Current of resonant inductor  $i_{Lrs}$  Secondary winding current

$i_{Lra}$ ,  $i_{Lrb}$ ,  $i_{Lrc}$  Current of resonant inductor  $L_{ra}$ ,  $L_{rb}$  and  $L_{rc}$

$i_{Lr-m}$  Peak value of resonant inductor current

$I_{Lr0}$ ,  $I_{Lr1}$ ,  $I_{Lr2}$  Preset inductor current level

$I_M$  Current of load

$I_{PR}$  Peak reverse recovery current of freewheeling diode

$I_{PT}$  Turning on peak current of power semiconductor switch

$I_R$  Rated phase current

$i_{S1} \sim i_{S6}$  Current of main switch  $S_1 \sim S_6$

$i_{SL}$  Current of auxiliary switch  $S_L$

*i<sub>sum</sub>* Absolute sum of phase currents

$i_s^*$  Steady state reference current

J Moment of inertia

k Armature constant  $4N_{ph}/\pi$

$k_c$  Clamping factor in ACRDCL inverter

$K_C$  Equivalent gain of the inverter for BDCM

$K_i$  The gain of current sensor

$K_{si}$  The gain of current controller

$K_{s\omega}$  The gain of speed controller

$K_{\omega}$  The gain of speed sensor

l Rotor axial length

L,  $L_a$ ,  $L_b$ ,  $L_c$  BDCM phase inductance

$L_{eq}$  Equivalent inductance (L-M)/2

$L_{l1}$  Primary winding leakage inductance

$L_{l2}$  Secondary winding leakage inductance

$L_r$  Resonant inductance

$L_{ra}$ ,  $L_{rb}$ ,  $L_{rc}$  Branch resonant inductance in resonant pole inverter

M Mutual inductance of BDCM

$M_1 \sim M_6$  Monostable flip-flop

$N_1$  The turn number of full-pitch coils in BDCM

$net_{j}^{1}$  The input of the  $j^{th}$  node in the 1<sup>st</sup> hidden layer

$net_k^2$  The input of the  $k^{th}$  node in the  $2^{nd}$  hidden layer

$net_1^3$  The input of only neuron in the ouput layer

$N_{ph}$  Number of turns in series per phase

p Derivational operator d/dt

P Power

$r_1$  Rotor radius

R,  $R_a$ ,  $R_b$ ,  $R_c$  BDCM phase resistance

$R_{eq}$  Equivalent resistance R/2

$R_{LR}$  Resistance of resonant inductor

$S_1 \sim S_6$  Main switches in an inverter

$S_a, S_b, S_c$  Auxiliary switch

$S_c$  Clamp switch in ACRDCL inverter

sel Controller selection signal

$S_h$  Upper switch in a phaseleg

$S_l$  Lower switch in a phaseleg

$S_{L}$ Auxiliary switch in main conduction path  $S_r$ Auxiliary switch in resonant DC link inverter  $T, T_e$ Electromagnetic torque of BDCM  $T_L$ Load torque Turn on time of a switch  $t_{on}$ Turn off time of a switch  $t_{off}$  $T_r$ Resonant period DC link voltage rising transition time  $T_{w}$ Fuzzy controller output membership function boundary  $u_1, u_2, u_3$  $u_{Cr}$ Voltage of resonant capacitor Voltage drop of main switch  $S_6$  $u_{S6}$ v,  $v_a$ ,  $v_b$ ,  $v_c$ Instantaneous phase voltage of BDCM Bootstrap capacitor voltage  $v_{bs}$  $v_{Cr1} \sim v_{Cr6}$ Snubber capacitor voltage DC link voltage  $v_{dc}$ Output voltage  $v_o$  $V_{FT}$ Conduction voltage drop of power semiconductor switch  $V_{FD}$ Conduction voltage drop of freewheeling diode  $V_R$ Rated voltage  $V_{S}$ Voltage of DC power supplies The weight between the  $j^{th}$  node in the  $1^{st}$  hidden layer and  $w_{ii}^1$ the  $i^{th}$  node in the input layer The weight between the  $k^{th}$  node in the  $2^{nd}$  hidden layer and  $w_{ki}^2$ the  $j^{th}$  node in the 1<sup>st</sup> hidden layer The weight between the  $k^{th}$  node in the  $2^{nd}$  hidden layer and  $w_{1k}^{3}$ the only one neuron in the output layer  $x_1(n) \sim x_5(n)$ Input of the neural network The output of the  $j^{th}$  node in the  $1^{st}$  hidden layer  $y_i^1$ The output of the  $k^{th}$  node in the  $2^{nd}$  hidden layer  $y_k^2$  $y_1^3$ The output of only neuron in the ouput layer Momentum gain  $\alpha$ Resonant circuit time constant τ

Electrical time constant

$au_e$

$\tau_{em}$  Electromechanical time constant

$\tau_m$  Mechanical time constant  $\tau_{si}$  The integral time constant

$\tau_{s\omega}$  The integral time constant of speed controller

$\omega_{cs}$  Critical frequency

$\dot{\omega}_{\scriptscriptstyle{\mathrm{max}}}$  Possible maximum acceleration

$\omega_r$  Natural angular resonance frequency

$\boldsymbol{\omega}_{r}^{*}, \boldsymbol{\omega}^{*}$  Reference speed

$\dot{\omega}_r$  Motor acceleration

$\omega_R$  Rated rotor speed

$\theta_r$  Rotor position

φ Flux

$\varphi_{cs}$  Phase margin  $\psi_1, \psi_2$  Flux linkage

$\psi_{1\text{max}}$  Maximum flux linkage

$\delta$  PWM duty

$\Delta t_1 \sim \Delta t_8$  Duration of the operation mode 1 ~ 8 in soft-switching inverter

$\Delta T_a, \Delta T_b, \Delta T_d$  Pulse width of auxiliary switch control signal  $\Delta T_1, \Delta T_2, \Delta T_3$  Pulse width of auxiliary switch control signal

$\Delta u$  Crisp incremental command

$\Delta \tilde{u}$  Incremental command fuzzy variable

$\Delta w$  Pulse width of Hall signal

$\Delta\delta$  Incremental PI current control output

$\mu(.)$  Membership function

$\eta$  Learning rate of the neural network

#### **Chapter 1** Introduction

#### 1.1 Background

Permanent magnet (PM) brushless DC motor (BDCM) [78, 81] has been widely used in industrial applications because of its low inertia, fast response, high power density, high reliability and less maintenance. It exhibits the operating characteristics of a conventional DC motor but eliminates the mechanical commutator and brushes. The stator structure is similar to that of a polyphase AC induction motor but with PM mounted on the rotor for excitation. This has the advantage of eliminating the use of commutator and brushes which are present in conventinal DC motor. Hence many problems associated with brushes are eliminated such as radio-frequency (RF) interfenence and sparking which is the potential source of ignition in inflammable atmosphere. The brushless configuration provides more cross sectional area for armature windings and produces greater torque and higher efficiency with the absence of brush friction. This also allows reduction of the motor length to provide greater torque/inertia ratio.

BDCM is usually supplied by a hard-switching Pulse-width-modulation (PWM) inverter. The performance of an inverter is dependent on the switching frequency as it determines the value and size of the reactive components in the inverter. Thus, high frequency operation of the inverter is desired. However, operation at high frequency results in higher switching power losses and higher switching stresses caused by the circuit parasitics (stray inductance, junction capacitance). In order to reduce the switching power losses, many soft switching inverters have been designed. Unfortunately, there are many drawbacks, such as high device voltage stress, large DC link voltage ripple, discrete pulse modulation, complex control scheme and so on. On the other hand, the majority of softswitching inverters proposed in recent decades have been aimed at the induction motor drive applications. [98. 99, 101] So research on the novel topology of soft-switching inverter and special control circuit for BDCM drive systems is very important.

#### 1.2 Conventional Voltage Source Inverter

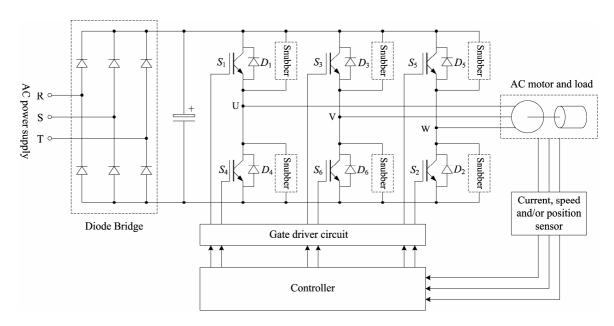

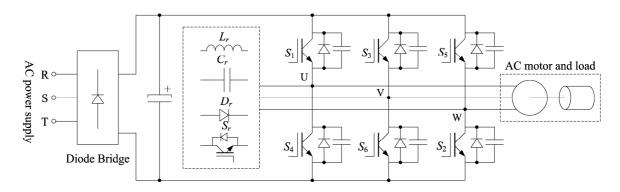

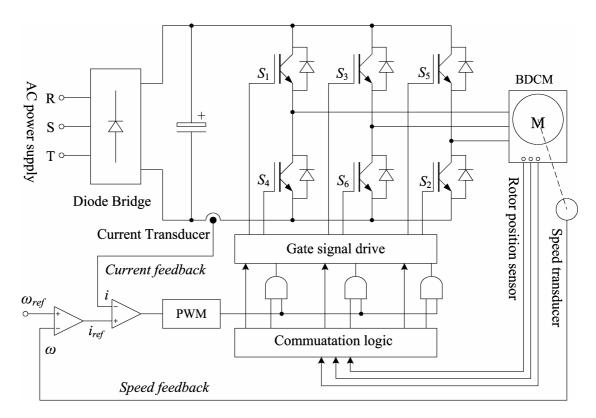

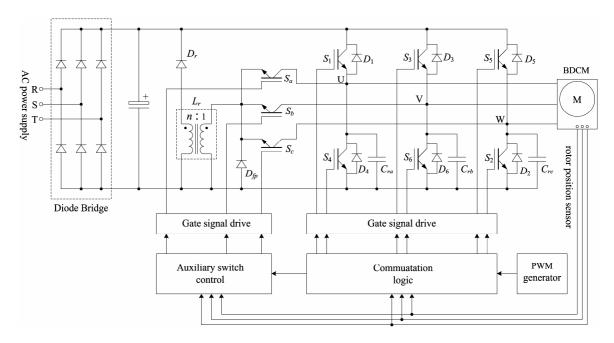

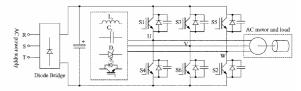

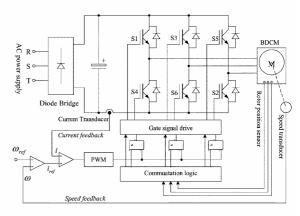

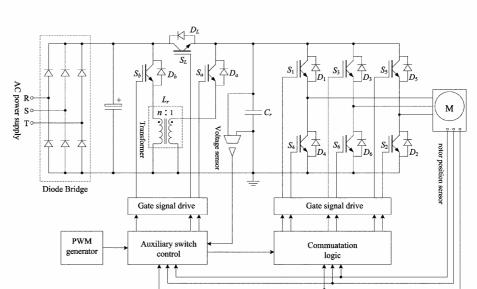

DC-to-AC converters are known as inverters [63]. The function of the inverter is to change a DC input voltage to a symmetrical AC output voltage of desired magnitude and frequency. With the improvement of power semiconductor switches such as insulated gate bipolar transistors (IGBTs), metal oxide- semiconductor field effect transistors (MOSFETs), intelligent power module (IPM), conventional voltage source inverter (VSI) are widely used in industrial applications, e.g. variable speed AC motor drives, induction heating, standby power supplies, uninterruptible power supplies (UPS). In small to medium power ranges, the VSI is superior than current source inverter (CSI) in smaller size, lower power losses and higher efficiency. The construction of a conventional voltage source three-phase inverter is shown in Fig. 1-1. There is diode bridge rectifier connected to AC power supplies, electrolytic capacitor as filter component, six power semiconductor switches inverter (including build-in freewheeling diodes, snubber circuit), gate driver circuit and controller. The current, speed and/or position feedback signal of the motor is usually fed to the controller.

Fig. 1-1. The construction of conventional voltage source three-phase inverter

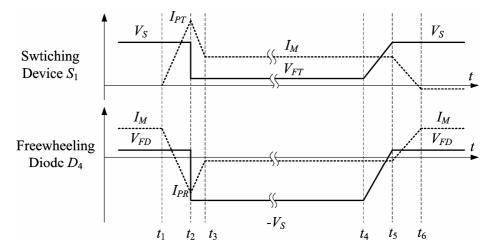

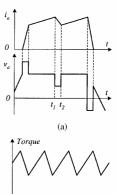

Power semiconductor switches have non-zero turn-on and turn-off times and thus there is a finite time during the transitions wherein the switches are carrying a significant current while a large voltage is applied across it. This results in large energy dissipation. This energy loss increases with the increasing of switching frequency. The typical voltage and current waveforms during one cycle of a power semiconductor switch and freewheeling diode are shown in Fig. 1-2 (linear for convenient). Suppose the load current flows through one lower freewheeling diode (e.g.  $D_4$ ) of the inverter before  $t_1$ , one upper power semiconductor switch (e.g.  $S_1$ ) turned on at  $t_1$ . During  $t_1$  and  $t_2$  load current is shifted from freewheeling diode ( $D_4$ ) to power semiconductor switch ( $S_1$ ), but there is significant reverse recovery current before the freewheeling diode can block reverse voltage. The reverse recovery current also flows through power semiconductor switch ( $S_1$ ), so the switching device current is the sum of reverse recovery current and load current. The voltage drop of power semiconductor switch is the same as that of DC link  $V_S$  before  $t_2$  (actually it is the sum of DC link voltage  $V_S$  and forward voltage drop of freewheeling diode  $V_{FD}$  which is relatively small and can be neglected), thus the power loss of the switching device is high during  $t_1$  and  $t_2$  (i.e. high turning on power loss). Similarly there are significant switching power losses of the freewheeling diode during  $t_2$  and  $t_3$ .

Fig. 1-2. The voltage and current waveforms of power semiconductor switch and freewheeling diode

| $V_S$    | Voltage of DC power supplies                          |

|----------|-------------------------------------------------------|

| $V_{FT}$ | Conduction voltage drop of power semiconductor switch |

| $V_{FD}$ | Conduction voltage drop of freewheeling diode         |

| $I_M$    | Current of load                                       |

| $I_{PR}$ | Peak reverse recovery current of freewheeling diode   |

| $I_{PT}$ | Turning on peak current of power semiconductor switch |

Then the power semiconductor switch  $(S_1)$  is turned off at  $t_4$ . Load current is shifted from switching device to freewheeling diode  $(D_4)$ . The voltage drop of power semiconductor switch rises from conduction voltage drop (several volts) to that of DC link before  $t_5$ . From  $t_5$  and  $t_6$  the switching device current decays to zero, but the voltage drop of power

semiconductor switch is the same as that of DC link, so the power loss of the switching device is high during  $t_4$  and  $t_6$  (i.e. high turning off power loss).

Turning on and turning off power losses are called switching power losses. It is well known that with higher switching frequency, the size of electromagnetic energy storage components like filter inductors and capacitors can be reduced significantly. The performance of the inverter is improved and the output current is more smooth. However the switching power loss increases significantly while the conduction power loss is almost the same. Thus, the total power loss increases significantly. For an IGBT in normal work condition, when the switching frequency is higher than 10kHz, the switching power losses is greater than conduction power losses. The switching power loss is primary for the higher switching frequency inverters.

Besides high power loss, the conventional hard switching has also the following drawbacks [63]:

- Second breakdown: there is turning off current spike for inductive load or turning on voltage spike for capacitive load with hard switching inverter, which can produce excessive localized hot spots to damage power semiconductor switch.

- Severe EMI: In hard switching inverter high dv/dt and di/dt induce voltage and current oscillations in parasitic capacitors and inductors during switching transitions. These oscillations result in higher peak current and voltage in the power switches and thus the switching power losses increase. These oscillations can also produce severe EMI which can interfere with other parts of the circuit or surrounding electronic equipment.

- Increase of power semiconductor switch presses: In order to decrease dv/dt and di/dt, snubber circuit is obligatory, but the snubber can not reduce power losses while it will increase current press on the power semiconductor switches.

- Noise: When the switching frequency is within audio spectrum, it may produce severe acoustic noise.

#### 1.3 Introduction to Soft-switching Inverter

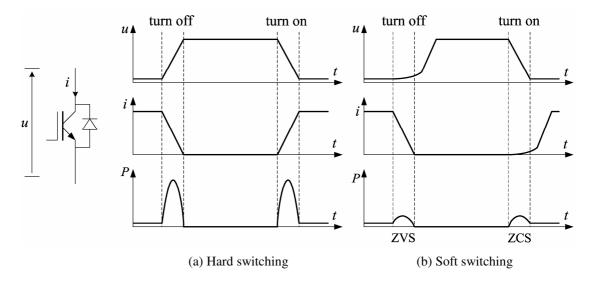

Soft switching has been proven to be an effective means of reducing switching losses and for attaining higher overall efficiencies. Various soft-switching techniques have been developed in recent decades. Soft-switching techniques force the switch voltage or current to zero before the device switching, thus avoiding current and voltage overlap during the switching transition. It can be achieved by either zero-voltage switching (ZVS) or zero-current switching (ZCS). ZVS consists of turning on/off the switches while the voltage across them is zero. ZCS consists of turning on/off the switches when the current through them is zero.

Fig. 1-3. Comparison of hard switching with soft switching

ZVS or ZCS can be accomplished by adding small undamped LC networks at strategic places in the inverter circuit and gating the power semiconductor switches on and off at the right opportunities. With soft-switching technology much demerit related to the hard switching can be reduced: reduction of switching power loss, risk of second breakdown, noise and eliminate snubber circuit. Lowering the inverter's overall losses can also make it possible to reduce its size by using smaller cooling apparatus. The switching waveforms in the conventional hard switching inverter and soft switching inverter are shown in Fig. 1-3. From the figure we can see that overlap of voltage drop and current of the soft-switching inverter is reduced, so the switching power loss can be reduced. ZCS turn on and ZVS turn off are similar to that of Fig. 1-3(b).

Soft switching technique was first introduced in DC/DC converter from the beginning of 1980s, such as Quasi-Resonant Converter (QRC) [25, 45, 46], Series Resonant Converter (SRC) [7, 83], Parallel Resonant Converter (PRC) [2, 93], Series-Parallel Resonant Converter (SPRC) [3, 69, 84], Multi-element Resonant Converter (MRC) [1, 35, 77, 94]. In 1986, D.M. Divan introduced soft switching technique in DC/AC inverter. In electric motor drive applications, soft-switching inverters are usually classified in three categories, namely resonant DC link inverters (RDCLI), resonant pole inverters (RPI) and resonant AC link inverters [6, 58].

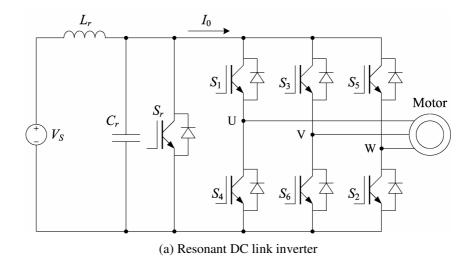

#### 1) Resonant DC Link Inverter

The structure of a resonant DC link inverter [17] is shown in Fig. 1-4. LC resonant circuit was added between DC power supply and 6-switches inverter. All power semiconductor switches' snubber circuit can be eliminated. Resonance occurs periodically or at controlled instant to make DC link voltage reach zero temporarily during which the power semiconductor switches at the output section could be switched on or off under ZVS condition.

Fig. 1-4. The structure of resonant DC link inverter

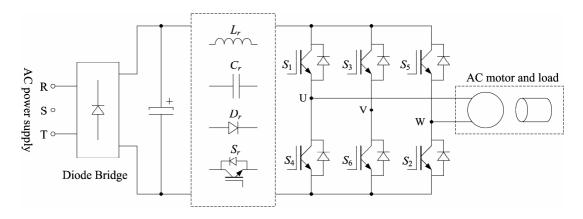

#### 2) Resonant Pole Inverter

The structure of a resonant pole inverter [18] is shown in Fig. 1-5. There is a so-called resonant pole that comprises a resonant inductor and a pair of resonant capacitors at each phase leg. These capacitors are directly connected in parallel with the main switches in order to achieve ZVS. In contrast to resonant DC link inverters, no resonance is produced

at the DC link. Instead of that, the resonant transitions occur separately at each resonant pole, only when the switches in the output stage need to be commutated. The DC link voltage remains unaffected during the resonant transitions. Therefore, the main switches in the inverter phase legs can be commutated totally independent from each other and we can choose the commutation instant freely. One of the disadvantages of the resonant pole inverter is that relatively more auxiliary switches are needed than that of resonant DC link inverter.

Fig. 1-5. The structure of resonant pole inverter

#### 3) Resonant AC Link Inverter

The structure of the resonant AC link inverter [58] is similar to the resonant DC link inverter. The resonant tank in the AC link produces a high-frequency alternating voltage or a high-frequency alternating current. The switches of both the source-side and the load-side inverters are turned on and off when the voltage or the current in the AC link passes through zero, minimizing the switching losses.

#### 1.4 Controller

Fuzzy logic, or fuzzy set theory, was first presented by Zadeh [53]. The main idea of fuzzy logic control [26, 48, 53] is to use the control ability of human being which includes experience and intuition, so the nature of the controller has adaptive characteristics that can achieve robust response to a system with uncertainty, parameter variation, and load disturbance. PI controller has the advantage of fast response especially in motor starting, but it will introduce overshoot and oscillation. The fuzzy logic controller can solve these problems while it is slower response than that of PI controller.

#### Chapter 1 Introduction

To utilize the advantages of both PI and fuzzy logic controllers to provide better response than any one controller only, a hybrid controller with fuzzy logic and PI will be introduced in this thesis.

A variable speed electric drive system is normally controlled by a speed/current double closed-loop controller. In conventional control system, during starting, the current reaches its maximum value quickly which contributes to the fast response of the system as the motor runs with maximum acceleration. When the motor reaches the desired speed, the current can not be reduced to its steady state value immediately; it needs time to settle. Normally overshoot and oscillation are inevitable, settling time is multiple that of the starting time. If current reaches its maximum value immediately during starting and when the motor reaches desired speed, the current skips to its steady state value at the same time and the motor runs at the desired speed, the starting time is shortest and the settling time is only the starting time. If the motor reaches desired speed while the current can only skip to around the steady state value, there is oscillation too, but the oscillation is smaller than that of conventional control system and the settling time can be reduced greatly, too.

To achieve fast starting, the key is to determine (predict) the steady state reference current during starting. An artificial neural network (ANN) [5, 10, 15] is a computational network, consisting of a number of interconnected processing units (neurons), which is able to learn and represent the unknown dependency relationship between a set of input variables and a set of output variables of a system. By selecting the training patterns (acceleration, speed, current, DC link voltage, reference speed) which cover all conditions (i.e. various DC link voltage, various load, various moment of inertia, various reference speed) to train the neural network, the neural network is then possible to predict the SSRC according to the acceleration, speed, current, DC link voltage, reference speed of the drive system, although the predicted value may be not very accurate.

#### 1.5 Objectives and Major Contributions

The objectives of this research work are as follows:

- To conduct a literature survey on soft-switching inverter and find possible topology which is applicable to BDCM drive system;

- To survey the current close-loop controller for variable speed drive system and offer new solutions to improve the performance of the system.

#### The major contributions are:

- Find a transformer based resonant DC link inverter which can generate DC link voltage notches during chopping switches commutation to guarantee all switches working in zero voltage switching condition. The inverter has the advantages: all switches work under soft-switching condition; voltage stress on all the switches would be not greater than DC supply voltage; only one DC link voltage notch is needed during one PWM cycle, and the switching frequency of the auxiliary switches would not higher than PWM frequency; *dvldt* and *dildt* are reduced significantly to reduce EMI, does not need center taped DC link capacitor; simple auxiliary switches control scheme and so on.

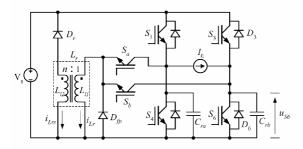

- Propose a novel resonant pole inverter, which is special to brushless DC motor drive system. The inverter possesses the advantages: low switching power loss; low inductor power loss; all switches work under soft-switching condition; voltage stress on all the switches would be not greater than DC supply voltage; The normal operation of the inverter is entirely the same as hard switching inverter; simple auxiliary switches control scheme; *dv/dt* and *di/dt* are reduced significantly to reduce EMI and so on.

- A hybrid controller for the PM BDCM drive system is proposed which holds the advantages of both PI controller and fuzzy controller, i.e. fast response, little overshoot, little oscillation, robust to system parameters variation, stability and so on.

- Propose a steady state reference current (SSRC) prediction technique based on neural network for PM BDCM drive system. Conventional controller combines with this technique can improve system response speed, reduce overshoot and oscillation.

#### 1.6 Organization of this thesis

This thesis comprises the brief describing the operation principle of BDCM, literature review of resonant DC link inverter and resonant pole inverter, analysis of proposed novel resonant DC link inverter and resonant pole inverter for BDCM drive system. Simulation and experiment are also proposed to verify the analysis. This thesis also proposes a fuzzy and PI hybrid controller that holds the advantages of PI and fuzzy logic controller. Then steady state reference current (SSRC) prediction technique will be introduced, Conventional controller with this technique holds the advantages of fast response, little overshoot, robust and so on. There are seven chapters in this thesis, the first chapter is the introduction of research work which contains background, overview of soft-switching inverter and major contribution of this thesis. The main contents are presented in Chapter 2, 3, 4, 5 and 6, respectively.

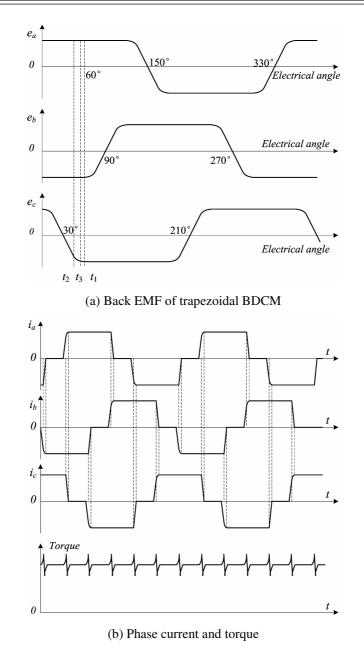

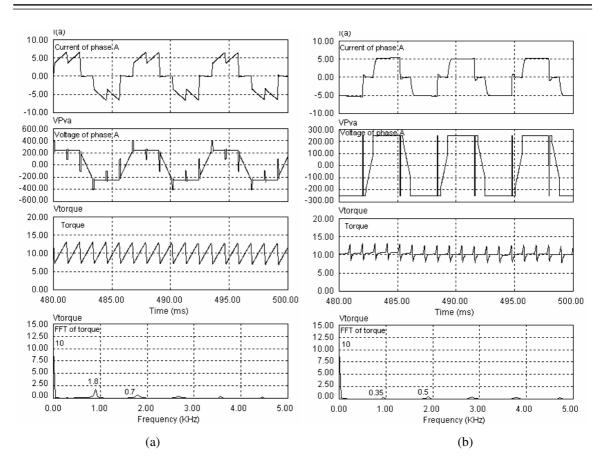

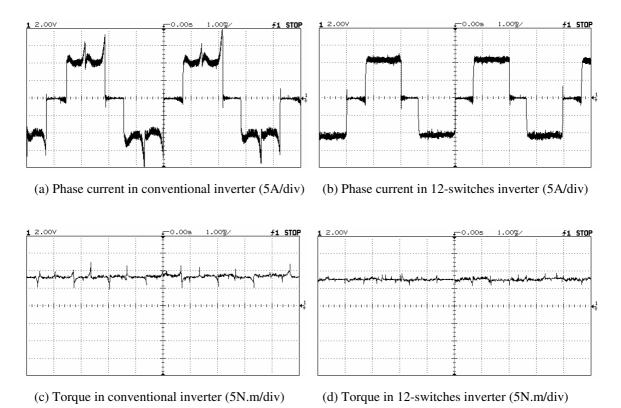

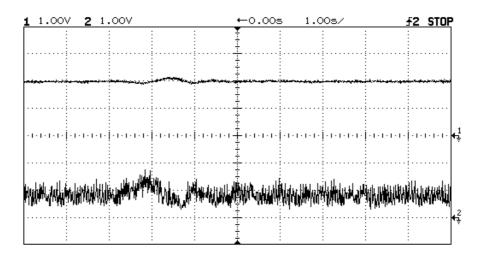

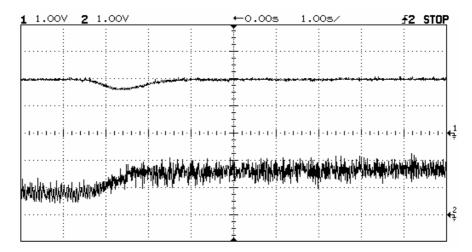

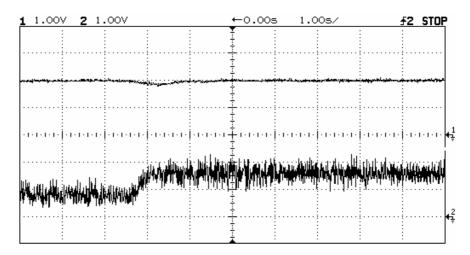

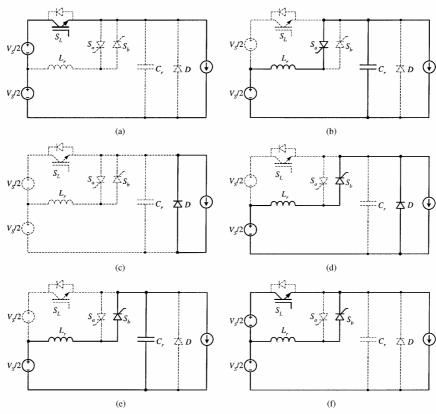

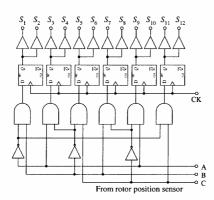

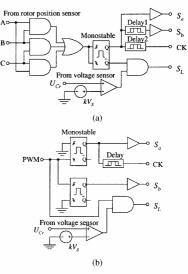

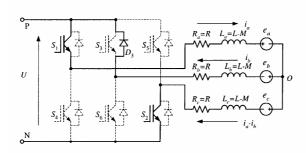

In Chapter 2, the operation principle of BDCM will be introduced first, the controller of the BDCM will be briefly described, then one novel method to reduce torque ripple will be proposed.