## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Fast finite field multipliers for public key cryptosystems

Satzoda Ravi Kumar

2007

Satzoda, R. K. (2007). Fast finite field multipliers for public key cryptosystems. Master's thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/39047

https://doi.org/10.32657/10356/39047

Downloaded on 20 Mar 2024 18:35:59 SGT

## Fast Finite Field Multipliers for Public Key Cryptosystems

#### Satzoda Ravi Kumar

School of Electrical and Electronic Engineering

A thesis submitted to the Nanyang Technological University in fulfillment of the requirement for the degree of Master of Engineering

2007

## Contents

| A  | cknov | wledgn  | nents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ⁄ii |

|----|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A۱ | bstra | ct      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ix  |

| 1  | Intr  | oducti  | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   |

|    | 1.1   | Backgr  | round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   |

|    | 1.2   | Motiva  | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2   |

|    | 1.3   |         | iives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3   |

|    | 1.4   |         | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4   |

|    | 1.5   |         | ization of Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6   |

| 2  | Bac   | kgroun  | nd and Literature Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9   |

|    | 2.1   | _       | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9   |

|    | 2.2   |         | aic Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9   |

|    |       | 2.2.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10  |

|    |       |         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11  |

|    |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11  |

|    | 2.3   | Public  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13  |

|    | 2.4   |         | [[[[[[[[[[[[[[[[[[[[[[[[[[[[[[[[[[[[[                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14  |

|    |       | 2.4.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15  |

|    | 2.5   | Ellipti |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17  |

|    |       | 2.5.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18  |

|    |       |         | Sundands⊕readed representations of the respect to the respect     | 19  |

|    |       | 2.5.2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22  |

|    |       | 2.5.3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23  |

|    |       | 2.5.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24  |

|    |       | 2.5.5   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25  |

|    |       | 2.5.6   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27  |

|    |       |         | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28  |

|    |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29  |

|    |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31  |

|    |       | 2.5.7   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32  |

|    |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33  |

|    |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34  |

|    |       |         | Source and property and the control of the control | 35  |

|   |     |         | Generalized bit-level parallel implementations [18]         |

|---|-----|---------|-------------------------------------------------------------|

|   |     |         | Consolidated results                                        |

|   | 2.6 | Inferen | ces and Summary                                             |

| 3 | Nev | Systo   | olic Architectures for Montgomery Modular Multiplication 45 |

|   | 3.1 | Introdu | uction                                                      |

|   | 3.2 | Montge  | omery Modular Multiplication Revisited                      |

|   | 3.3 | Proble  | m Statement                                                 |

|   | 3.4 |         | sed Modified MMM                                            |

|   | 3.5 | Archite | ectures                                                     |

|   |     |         | Basic Computing Cell                                        |

|   |     |         | Two-dimensional Pipelined Parallel Architecture             |

|   |     |         | One-dimensional Variant                                     |

|   | 3.6 | Hardw   | are Implementation Results                                  |

|   |     | 3.6.1   | Qualitative Results                                         |

|   |     | 3.6.2   | FPGA Implementation Results 60                              |

|   |     | 3.6.3   | ASIC Implementation Results 64                              |

|   | 3.7 | Summa   | ary                                                         |

| 4 | Uni | fied M  | ontgomery Modular Multiplication 67                         |

|   | 4.1 |         | uction                                                      |

|   | 4.2 | Prelim  | inaries                                                     |

|   |     | 4.2.1   | $GF(N)$ and $GF(2^m)$                                       |

|   |     | 4.2.2   | Montgomery multiplication in $GF(N)$ and $GF(2^m)$ 69       |

|   |     | 4.2.3   | Review of Existing Unified MMMs                             |

|   | 4.3 | Proble  | m Statement                                                 |

|   | 4.4 | Propos  | sed Unified Montgomery Multiplier                           |

|   |     | 4.4.1   | Notations                                                   |

|   |     | 4.4.2   | Derivation of the Dual-field Logic                          |

|   |     | 4.4.3   | Derivation of the Dependency Graphs                         |

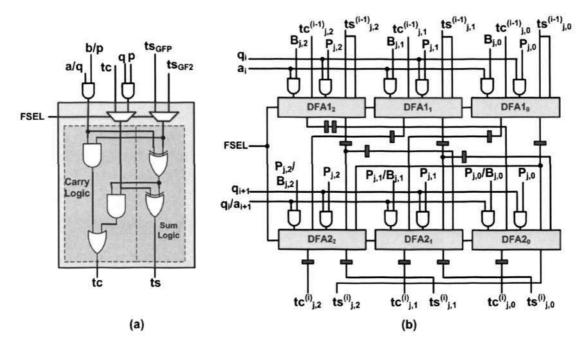

|   |     | 4.4.4   | Processing Unit for Unified Multiplier                      |

|   |     | 4.4.5   | Computation of $q$                                          |

|   |     | 4.4.6   | Reservation Table of the Pipeline                           |

|   |     | 4.4.7   | Multiplier Architecture                                     |

|   | 4.5 | Result  | s                                                           |

|   |     | 4.5.1   | Critical Path and Latency                                   |

|   |     | 4.5.2   | FPGA Implementation Results                                 |

|   |     | 4.5.3   | Total Computation Time                                      |

|   |     | 4.5.4   | Area Time Product                                           |

|   |     | 4.5.5   | Discussion                                                  |

|   | 16  | Cumm    | 05                                                          |

| 5  | LSE           | 3-first/ | MSB-first Multipliers for Generic Curves             | 100         |

|----|---------------|----------|------------------------------------------------------|-------------|

|    | 5.1           | Introd   | uction                                               | 100         |

|    | 5.2           |          | ninaries                                             |             |

|    |               | 5.2.1    | Fixed Order Algorithms                               | 102         |

|    |               | 5.2.2    | Problem of Field Order Generalization                |             |

|    |               | 5.2.3    | Existing Generalized LSB-first/MSB-first Multipliers |             |

|    | 5.3           | Proble   | em Statement                                         |             |

|    | 5.4           |          | sed Method and Architectures                         |             |

|    |               | 5.4.1    |                                                      |             |

|    |               |          | Signal Flow Graphs                                   |             |

|    |               |          | Implementation of SFGs                               |             |

|    |               | 5.4.2    | The S-Array                                          |             |

|    | 5.5           | Result   | as and Discussion                                    |             |

|    | 11/25/11/07/0 | 5.5.1    | Gate Count                                           |             |

|    |               | 5.5.2    | Latency and critical path delay                      |             |

|    | 5.6           | Summ     | ary                                                  |             |

| 6  | Cor           | clusio   | ns and Future Work                                   | 121         |

| U  | 6.1           |          | usions                                               | CERTAIN THE |

|    | 6.2           |          | nmendations for Future Work                          |             |

|    | ٥.2           | 100001   |                                                      |             |

| Li | st of         | Auth     | or's Publications                                    | 125         |

| В  | iblio         | graphy   |                                                      | i           |

## List of Figures

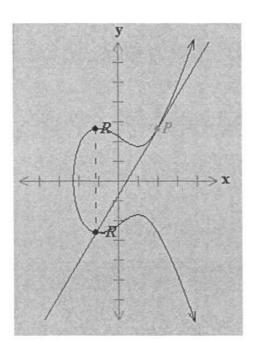

| 2.1      | Point addition (PA) on elliptic curves                                                                                                                             | 19 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2      | Point doubling (PD) on elliptic curves                                                                                                                             | 20 |

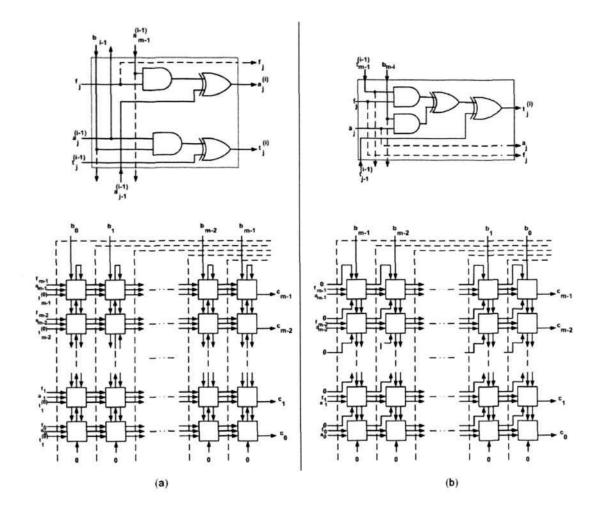

| 2.3      | (a) Basic cell and architecture for LSB-first bit-parallel finite field multi-                                                                                     |    |

|          | plier [18](b) Basic cell and architecture for MSB-first bit-parallel finite field                                                                                  |    |

|          | multiplier [18]                                                                                                                                                    | 29 |

| 2.4      | (a) Basic cell and (b) Bit-serial MSB-first finite field multiplier [51]                                                                                           | 30 |

| 2.5      | (a) DG as in [13] (b) DG as in [20]                                                                                                                                | 31 |

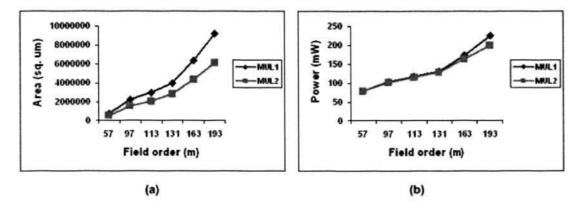

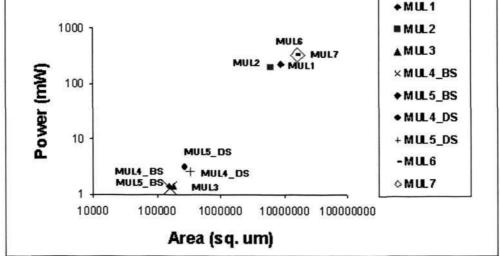

| 2.6      | (a) Area results and (b) Power results of MUL1 and MUL2                                                                                                            | 36 |

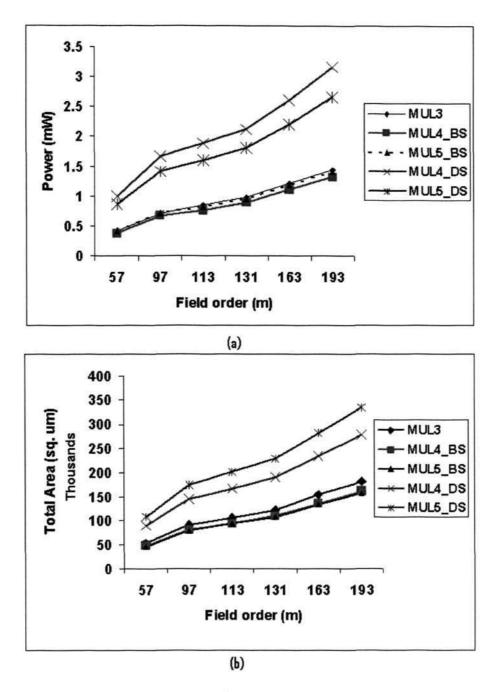

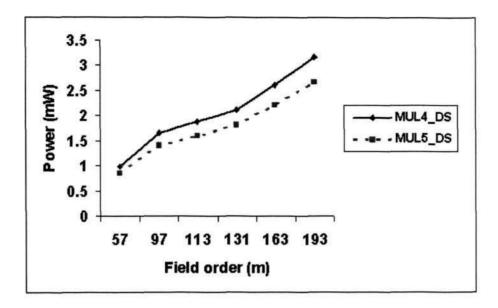

| 2.7      | (a) Power and (b) Area results of serial multipliers                                                                                                               | 37 |

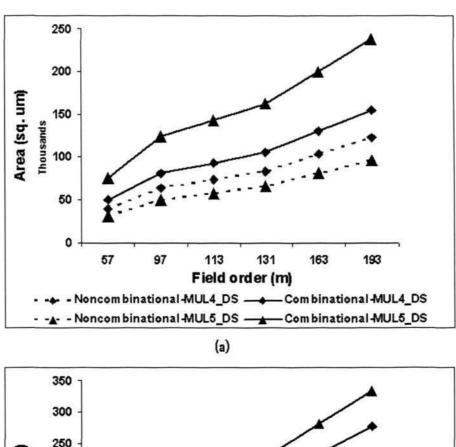

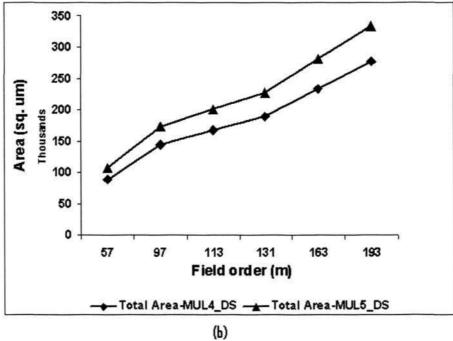

| 2.8      | (a) Combinational and non-combinational areas (b) Total areas of digit-                                                                                            |    |

|          | serial multipliers                                                                                                                                                 | 38 |

| 2.9      | Power dissipation of digit-serial multipliers                                                                                                                      | 39 |

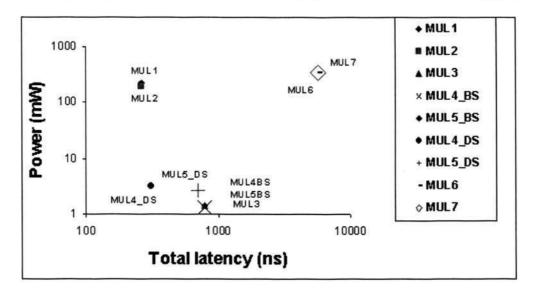

| 2.10     | Consolidated Results: Power vs. Total Latency                                                                                                                      | 40 |

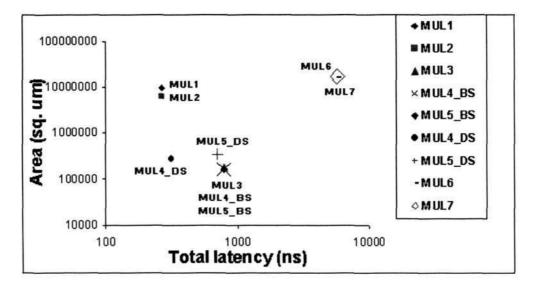

| 2.11     | Consolidated Results: Area vs. Total Latency                                                                                                                       | 41 |

| 2.12     | Consolidated Results: Power vs. Area                                                                                                                               | 42 |

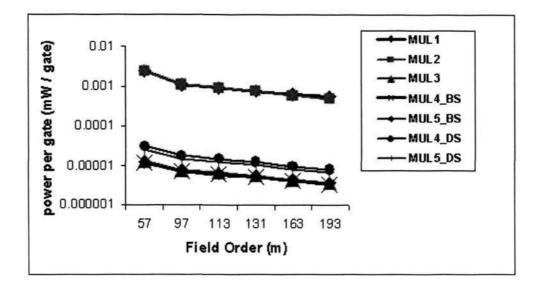

| 2.13     | Consolidated Results: Power per gate vs. Field order                                                                                                               | 43 |

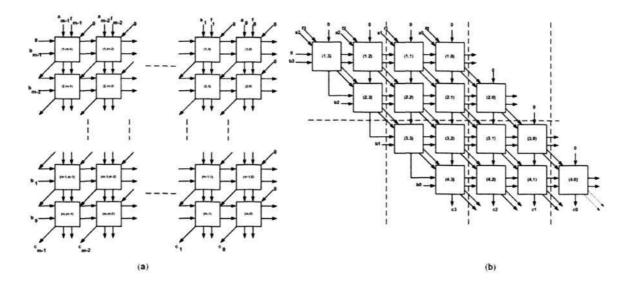

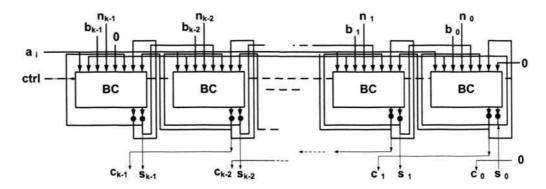

| 3.1      | Basic cell (BC) or computation unit                                                                                                                                | 54 |

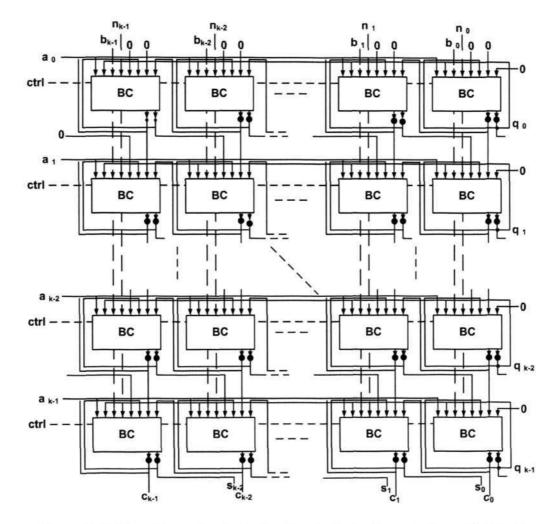

| 3.2      | Two dimensional pipelined systolic implementation - Design 1                                                                                                       | 55 |

| 3.3      | a) Indices of Sum $S$ and Carry $C$ of the $i$ -th row of basic cells in the $m$ -th and $(m+1)$ -th clock cycles (b) Reservation table of the pipeline of the 2-D |    |

|          | architecture                                                                                                                                                       | 56 |

| 3.4      | One-dimensional systolic implementation - Design 2                                                                                                                 | 57 |

| 0.1      |                                                                                                                                                                    |    |

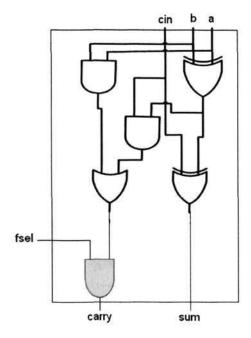

| 4.1      | Dual field adder in [48]                                                                                                                                           | 71 |

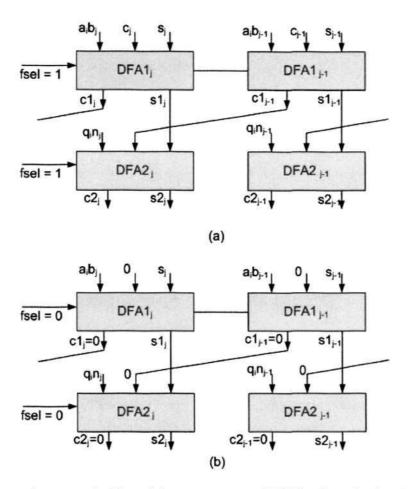

| 4.2      | Input/output of adders (a) operation in $GF(N)$ when $fsel = 1$ (b) operation                                                                                      |    |

|          | in $GF(2^m)$ when $fsel = 0 \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                       | 73 |

| 4.3      | Sum and carry logics in (a) $GF(N)$ (b) $GF(2^m)$                                                                                                                  | 75 |

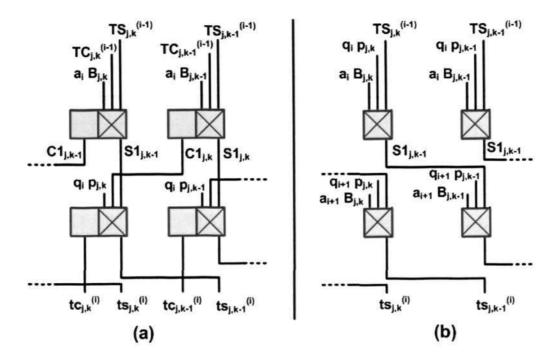

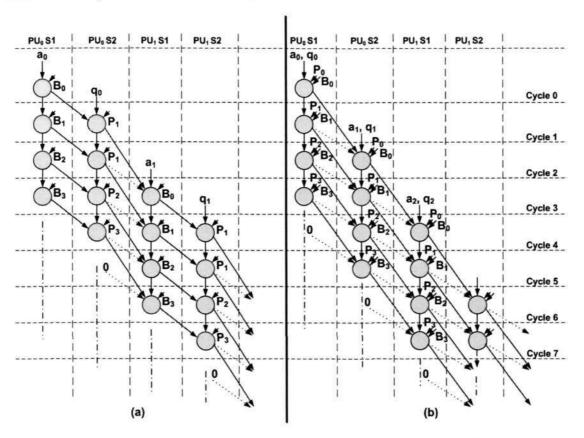

| 4.4      | Dependency graphs for (a) $GF(N)$ (b) $GF(2^m)$                                                                                                                    | 82 |

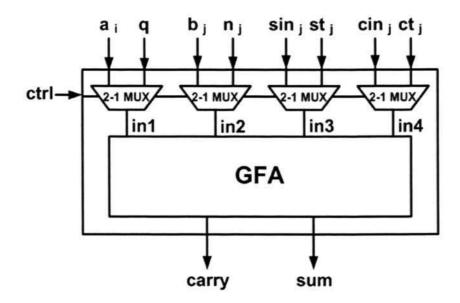

| 4.5      | (a) Dual Field Adder for $w = 1$ (b) Processing unit for wordlength $w = 3$ .                                                                                      | 84 |

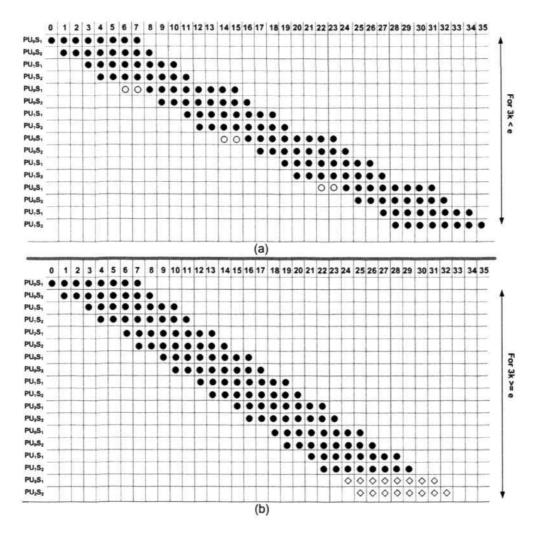

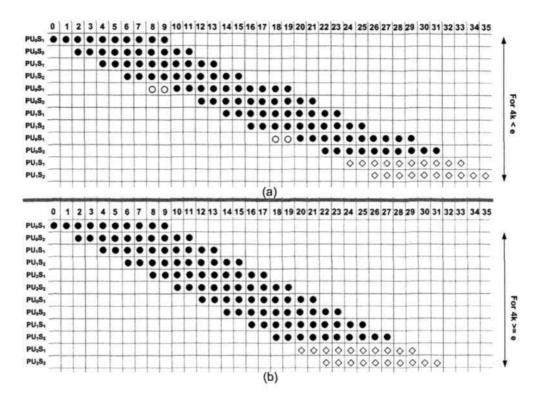

| 4.6      | Reservation table for operation in $GF(N)$ (a) $m = 8$ , $w = 1$ and $k = 2$                                                                                       |    |

| 10/12/20 | (b) $m = 8$ , $w = 1$ and $k = 3$                                                                                                                                  | 86 |

| 4.7      | Reservation table for operation in $GF(2^m)$ (a) $m = 10$ , $w = 1$ and $k = 2$                                                                                    | -  |

| 4.0      | (b) $m = 10$ , $w = 1$ and $k = 3$                                                                                                                                 | 87 |

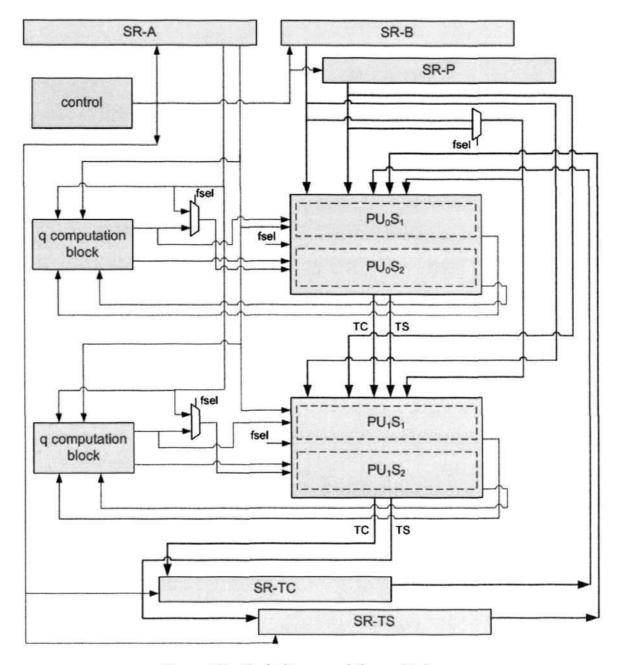

| 48       | Block diagram of the multiplier                                                                                                                                    | 89 |

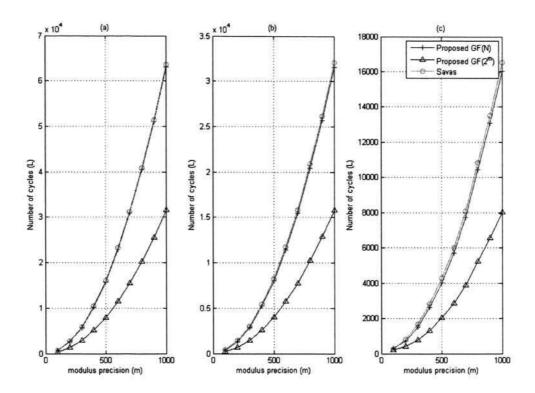

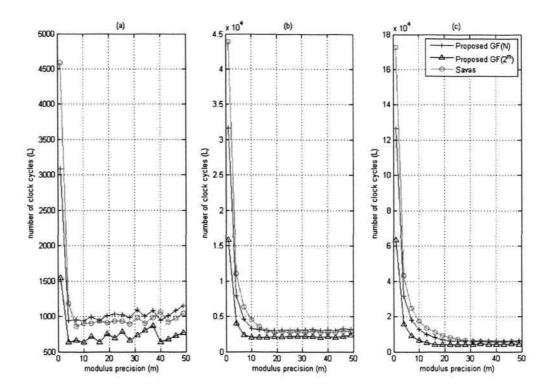

| 4.9  | Total clock cycles (L) vs. modulus precision (m) for (a) $w = 8$ (b) $w = 16$                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

|      | (c) $w = 32 \dots $ | 91  |

| 4.10 | Total clock cycles (L) vs. number of PUs (k) for $w = 16$ and (a) $m = 160$                                               |     |

|      | (b) $m = 512$ (c) $m = 1024$                                                                                              | 92  |

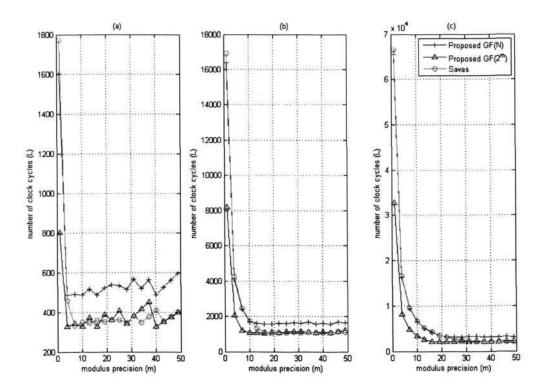

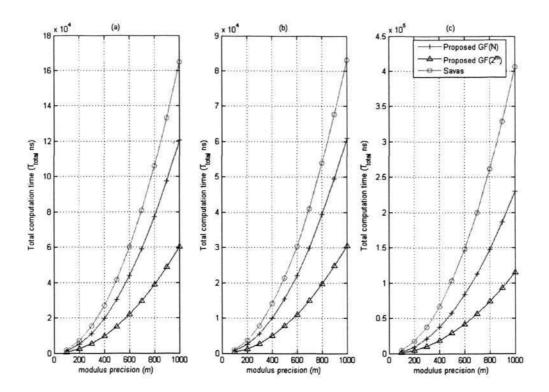

| 4.11 | Total computation time $(t_{total})$ vs. modulus precision (m) for (a) $w = 8$ (b)                                        |     |

|      | w = 16 (c) $w = 32$                                                                                                       | 96  |

| 4.12 | Total computation time $(t_{total})$ vs. number of PUs $(k)$ for $(a)$ $w = 8$ $(b)$                                      |     |

|      | w = 16 (c) $w = 32$                                                                                                       | 97  |

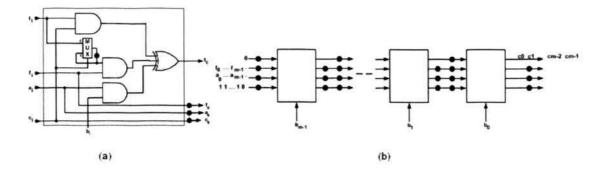

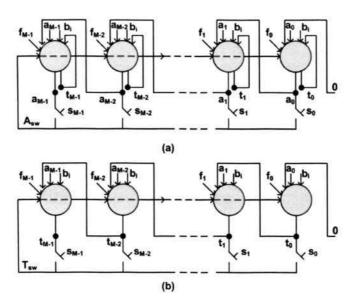

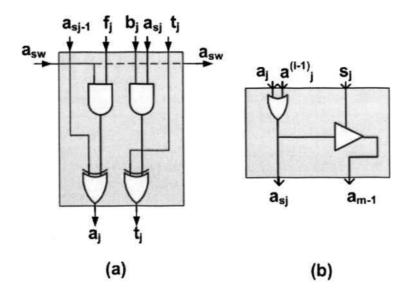

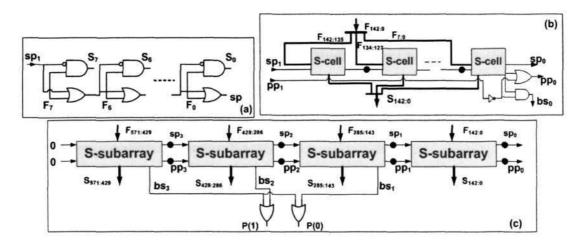

| 5.1  | Signal flow graphs (a) LSB-first multiplier (b) MSB-first multiplier for $GF(2^M)$                                        | 110 |

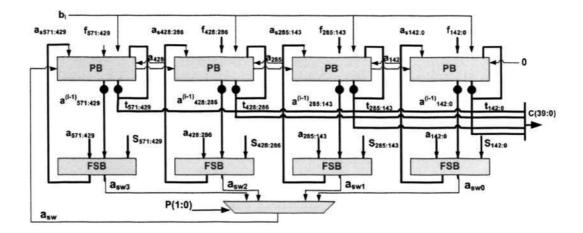

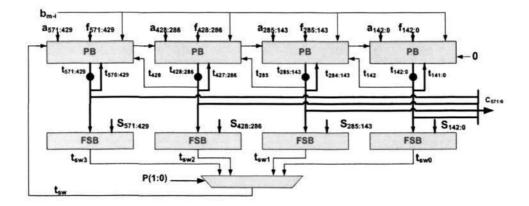

| 5.2  | Proposed LSB-first multiplier for arbitrary $m \leq 572 \dots \dots$                                                      | 113 |

| 5.3  | (a) Processing element (b) Field selector for the proposed LSB-first mulitplier                                           | 113 |

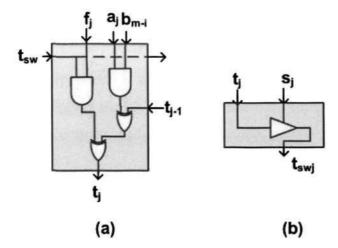

| 5.4  | Proposed MSB-first multiplier for arbitrary $m \leq 571 \dots \dots \dots$                                                | 114 |