### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

## Fully-integrated CMOS building blocks for phase-locked loops in the multi-GHz range

Yu, Xiaopeng

2006

Yu, X. (2006). Fully-integrated CMOS building blocks for phase-locked loops in the multi-GHz range. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/3940

https://doi.org/10.32657/10356/3940

Nanyang Technological University

Downloaded on 09 Apr 2024 10:50:37 SGT

# Fully-Integrated CMOS Building Blocks for Phase-Locked Loops in the Multi-GHz Range

#### **YU XIAOPENG**

#### School of Electrical & Electronic Engineering

A thesis submitted to the Nanyang Technological University in fulfillment of the requirement for the degree of Doctor of Philosophy

#### STATEMENT OF ORIGINALITY

| I hereby certify the content of this thesis is the result of work done by me and has |             |  |  |

|--------------------------------------------------------------------------------------|-------------|--|--|

| not been submitted for higher degree to any other University or Institution.         |             |  |  |

|                                                                                      |             |  |  |

|                                                                                      |             |  |  |

|                                                                                      |             |  |  |

|                                                                                      |             |  |  |

| Date                                                                                 | Yu Xiaopeng |  |  |

#### **Acknowledgments**

With a deep sense of gratitude, I wish to express my sincere thanks to my supervisor, Professor Do Manh Anh, for his continuous insight, enthusiasm and encouragement. His deep passion for various scientific problems has taught me a lot. His guidance during the development of my research has been invaluable. I also would like to thank Associate Professor Ma Jian Guo and Associate Professor Yeo Kiat Seng. Their professional attitudes, continuous supports and management skills deserve special acknowledgment. I would like to extend my special thanks to Associate Professor Lin Yiqun, my undergraduate supervisor in Zhejiang University. He has been a great advisor and a friend for me.

People at Centre for Integrated Circuits and Systems have contributed to this work. I had the most wonderful learning experience working with a team of very active and bright PHD and Master students in the RFIC design, which include Jia Lin, Dr. Boon C. C., Lim Wei Meng, Cabuk A., Wu Rui and Yan Guoqiang. It would have been impossible to achieve these research results without the consistent technical support of Mr. Richard, Miss Guee and Mrs. Min Lin in IC Design Lab II.

Finally, I will never find words enough to express the gratitude that I owe to my family in China. Tender love and support from my parents and my wife have always been the cementing force for building the blocks of my research career.

#### **ABSTRACT**

The wireless communication industry is currently experiencing a tremendous growth. For Wireless LAN applications, the IEEE 802.11 multiple standards have been widely adopted for the short-range communication in the two ISM bands of 2.45 GHz and 5.1-5.8 GHz. This results in an increasing demand for highly integrated transceivers of lower power consumption and small die sizes. The frequency synthesizer, which is usually formed by a Phase-Locked Loop (PLL), is a major and critical component of a wireless transceiver because it operates at high frequency and consumes a very large portion of the total power consumption in the transceiver. Currently, there exist several different standards of operation; thus a multi-standard frequency synthesizer is desirable for operations under different wireless systems. The performance in power consumption and channel selection of a frequency synthesizer are limited by the two most important building blocks, namely the frequency divider and voltage-controlled oscillator (VCO). The objective of this project is to design the most critical building blocks for the multi-GHz frequency synthesizers. All proposed circuits are realized on cost effective CMOS technology (0.18 µm CMOS process) rather than bipolar, SiGe and GaAs technologies. The power consumption and the operating frequency of PLL circuits will be analyzed in details. The power consumption reduction and speed enhancement are realized through novel topologies proposed for the frequency dividers, which dominate the overall power consumption and speed performance of the PLL. A 1 V 4 mW 10 GHz divide-by-2 unit is proposed by using the modified dynamic MOS Current Mode Logic structure in post-layout simulation. Two prescalers, implemented with the dynamic CMOS circuit and the imbalanced

phase switching technique are proposed to achieve lower power consumption for a higher operating frequency. The dynamic CMOS divide-by-8/9 prescaler implemented with an E-True-Single-Phase-Clock dynamic circuit achieves a lower power consumption compared to that of existing designs. Due to the limitation of the process design kit, large size RFMOS FETs were used in the implementation; the current consumption was 25 mA for an input signal frequency of 3.5 GHz. If the device width is scaled down to 2 µm, low power consumption of 1.6 mW is achieved. The prescaler implemented with large RFMOSs in the front stages using the 4-to-1 imbalance phase switching technique can work from 2 GHz to well above 4 GHz with a power consumption of 32 mW for a supply voltage of 1.8 V. A large power consumption reduction is expected if smaller RFMOSs are available in the process design kit. The GHz operation of all-stage programmable counter is first achieved in this work by proposing a new re-loadable bitcell. The measurement result shows that the all-stage programmable counter can work up to 1.8 GHz with a power consumption of 5.8 mW for a supply voltage of 1.8 V. To achieve the multi-band operation, a VCO with a wide tuning range of 5-6 GHz and a good phase noise performance is designed. A multi-band imbalance phase switching prescaler is used to cover the 5-6 GHz and 2-3 GHz WLAN bands. Moreover, to obtain a high resolution for the output frequency channels, a GHz allstage-programmable counter is used in the design of the programmable frequency divider. By combining with other low frequency building blocks, namely the phase frequency detector, the charge pump and the loop filter, a complete 5-6 GHz frequency synthesizer is realized to cover both the IEEE 802.11a and the HIPERLAN II standards. Post-layout simulation shows that the whole frequency synthesizer is able to work with a low power consumption of 30 mW.

Besides configured as a frequency synthesizer, a PLL is also widely used as a clock data recovery (CDR) system. In this application, the phase detector has become the most challenging block in the PLL since it has to operate at the highest frequency with the two high speed input signals. A novel full-rate linear phase detector using an I/Q splitter is proposed for 10 Gb/s SONET applications.

#### The author's publications:

#### Journal publications:

- **X. P. Yu**, M. A. Do, L. Jia, J. G. Ma, K. S. Yeo, "Design of a low power wide band high resolution programmable frequency divider," *IEEE Trans. VLSI*, Volume: 13, no. 9, pp. 1098-1103, Sep. 2005.

- **X. P. Yu**, M. A. Do, J. G. Ma, K. S. Yeo, R. Wu and G. Q. Yan, "10Gb/s linear full-rate CMOS phase detector for clock data recovery circuit," Analog *Integrated Circuits & Signal Processing*, Volume: 45, pp. 191-196, Kluwer Academic Publishers, 2005.

- **X. P. Yu**, M. A. Do, J. G. Ma, K. S. Yeo, R. Wu and G. Q. Yan, "Low power high speed CMOS dual-modulus prescaler design with imbalanced phase switching technique," *IEE Proc. Circuits, Devices & Systems*, Volume: 152, Issue: 2, pp. 127-132. Apr. 2005.

- G. Q. Yan, M. A. Do, X. P. Yu, J. G. Ma, K. S. Yeo and R. Wu, "Compact CMOS Baluns for the 4-10GHz Band Applications," *Analog Integrated Circuits & Signal Processing*, vol. 45, pp. 5-13, Kluwer Academic Publishers, 2005.

- **X. P. Yu**, M. A. Do, J. G. Ma, K. S. Yeo, R. Wu and G. Q. Yan, "1V 10GHz CMOS frequency divider with low power consumption," *Electronics Letters*, Volume: 40, Issue: 8, pp. 467-468, Apr. 2004.

- M. A. Do, **X. P. Yu**, J. G. Ma, K. S. Yeo, R. Wu and Q.X. Zhang, "GHz programmable counter with low power consumption," *Electronics Letters*, Volume: 39, Issue: 22, pp. 1572-1573, Oct. 2003.

#### **Conference proceedings:**

- **X. P. Yu**, M. A. Do, J. G. Ma and K. S. Yeo, "A new 5GHz CMOS dual-modulus prescaler," *2005 IEEE International Symposium on Circuits and Systems*, Kobe, Japan, pp. 5027 5030, May, 2005.

- M. A. Do, **X. P. Yu**, J. G. Ma, K. S. Yeo, R. Wu and Q.X. Zhang, "A 2GHz programmable counter with new re-loadable D flip-flop," *Proceeding of 2003 IEEE Conference on Electron Devices and Solid-State Circuits (EDSSC'03)*, pp. 269-272, Dec. 2003.

- M. A. Do, **X. P. Yu,** J. G. Ma, K. S. Yeo and Q.X. Zhang, "A 1.5V Frequency Divider for 5~6GHZ Wireless LAN Applications," *Proceeding of Asia Pacific Microwave Conference (APMC'03)*, pp. 998-1001, Nov. 2003.

#### **List of Contents:**

| Ackno      | wledgments                                                                             | I        |

|------------|----------------------------------------------------------------------------------------|----------|

| ABSTR      | ACT                                                                                    | IJ       |

| Chapte     | er 1 Introduction                                                                      | 1        |

| 1.1        | Background and motivation                                                              | 1        |

| 1.2        | Wireless LAN and CDR standards                                                         | 4        |

| 1.3        | Thesis organization                                                                    | 6        |

| Chapte     | er 2 Overview of Phase-Locked Loops                                                    | 8        |

| 2.1        | Building blocks of PLLs                                                                | 8        |

| 2.2        | Linear model of PLLs                                                                   | 10       |

| 2.3        | The performance of PLLs                                                                | 16       |

|            | 3.1 Tuning range and frequency resolution                                              | 17       |

|            | 3.2 Phase noise                                                                        |          |

|            | Voltage Controlled Oscillators                                                         |          |

|            | 4.1 Ring oscillators                                                                   |          |

|            | 4.2 LC oscillators                                                                     |          |

|            | 4.3 Noise performance of an oscillator                                                 |          |

| 2.5        | High Speed Frequency Dividers5.1 The implementation of frequency dividers              |          |

|            | 5.2 High speed digital circuits                                                        |          |

|            | Conclusion                                                                             |          |

| Chapte     | er 3 Design and Optimization of high speed CMOS Prescalers                             | 50       |

| 3.1        |                                                                                        |          |

| 3.2        |                                                                                        |          |

|            | 2.1 TSPC and E-TSPC divide-by-2 units                                                  |          |

| 3.2        | 2.2 E-TSPC based divide-by-2/3 unit                                                    | 59       |

|            | 2.3 Proposed topology                                                                  |          |

|            |                                                                                        |          |

| 3.3        | Low power high speed CMOS dual-modulus prescaler with Imbala<br>se switching technique |          |

|            | 3.1 Challenging of phase switching prescaler design                                    |          |

|            | 3.2 Imbalanced phase switching technology                                              |          |

|            | 3.3 Design of prescaler with the imbalanced phase switching techn                      |          |

|            | 3.4 Simulation and silicon verifications                                               |          |

| 3.4        | Conclusion                                                                             | 90       |

|            | er 4 Design of a Low Power Wide Band High Resolution Programma                         |          |

| 4.1        | Introduction                                                                           |          |

|            | Design consideration                                                                   |          |

| 4.2<br>4.3 | Design of a high speed low power digital counter                                       | 93<br>08 |

| 4 3        | LIESTON OF A THURS STEED HOW HOWEL HILLIAL COURSE                                      | UX       |

| 4.4    | Simulation and measurement results of the counter     | 105 |

|--------|-------------------------------------------------------|-----|

| 4.5    | A Wide band high resolution frequency divider         | 109 |

| 4.6    | Conclusion                                            | 117 |

| Chapte | er 5 Phase Noise in the TSPC Based Frequency Divider  | 118 |

| 5.1    | Introduction                                          | 118 |

| 5.2    | Phase noise and jitter in frequency dividers          | 119 |

| 5.3    | Time-variant jitter method                            | 121 |

| 5.4    | Noise estimation                                      | 127 |

| 5.5    | Design implementation                                 | 132 |

| 5.6    | Conclusion                                            | 133 |

| Chapte | er 6 A 5-6 GHz frequency synthesizer                  | 134 |

| 6.1    | Phase frequency detector                              | 134 |

| 6.2    | Charge pump                                           | 138 |

| 6.3    | Loop filter                                           | 140 |

| 6.4    | Design of the wideband VCO                            | 142 |

| 6.5    | Layout issues of the frequency synthesizer            |     |

| 6.6    | Post layout simulation results                        | 150 |

| 6.7    | Conclusion                                            | 152 |

| Chapte | er 7 High Speed Phase Detectors and Divide-by-2 Units | 153 |

| 7.1    | A 10 Gb/s linear full-rate CMOS phase detector        | 153 |

|        | 1.1 Review of linear PD design                        | 156 |

|        | 1.2 Limitation in existing designs                    |     |

|        | 1.3 Proposed topology                                 |     |

| 7.2    |                                                       |     |

|        | umption                                               | 169 |

|        | 2.1 Design challenging in the divide-by-2 unit        |     |

| 7.2    | 2.2 Proposed topology                                 | 173 |

| 7.3    | Conclusion                                            |     |

| 7.3    | Conclusion                                            | 1/9 |

| •      | er 8 Conclusion                                       |     |

| 8.1    | Conclusion of remarks                                 | 181 |

| 8.2    | Future work                                           | 183 |

| Refere | nces                                                  | 185 |

#### **List of Figures:**

| Figure 2.1: A general topology of a PLL                                          |      |

|----------------------------------------------------------------------------------|------|

| Figure 2.2: A linear model for PLL                                               | . 11 |

| Figure 2.3: A lag RC filter                                                      | . 12 |

| Figure 2.4: A passive lag-lead filter                                            | . 13 |

| Figure 2.5: A Charge-pump PLL                                                    |      |

| Figure 2.6: The output spectrum of a PLL                                         | . 18 |

| Figure 2.7: Effects of phase noise in a receiver                                 | . 19 |

| Figure 2.8: Feedback diagram of an oscillator                                    |      |

| Figure 2.9: A three stage ring oscillator a) topology b) linear model            |      |

| Figure 2.10: The general topology of a LC oscillator                             |      |

| Figure 2.11: Conversion of a tank to three parallel components                   |      |

| Figure 2.12: A complex model for the LC tank                                     | . 27 |

| Figure 2.13: The cross-coupled structure                                         |      |

| Figure 2.14: PN-junction varactor a) structure b) capacitance over voltage       | . 30 |

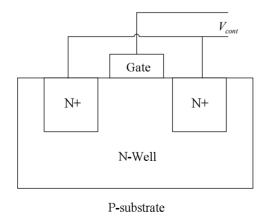

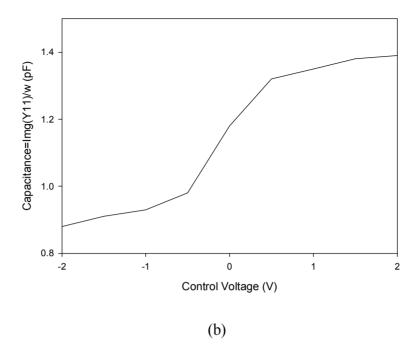

| Figure 2.15: Accumulation-mode varactor a) structure b) capacitance over voltage | 31   |

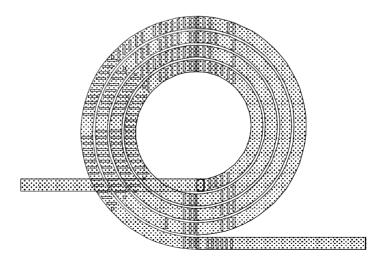

| Figure 2.16: Geometry of a spiral inductor                                       |      |

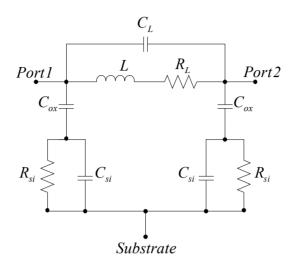

| Figure 2.17: The lump element model of an on-chip inductor                       |      |

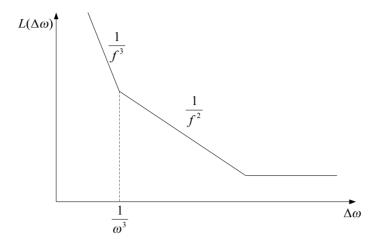

| Figure 2.18: The spectrum of the phase noise                                     |      |

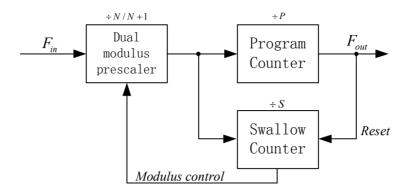

| Figure 2.19: The pulse swallow integer frequency divider                         |      |

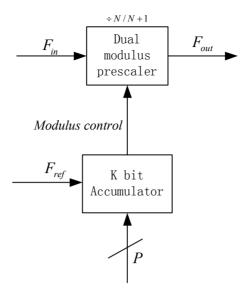

| Figure 2.20: The fractional frequency divider                                    |      |

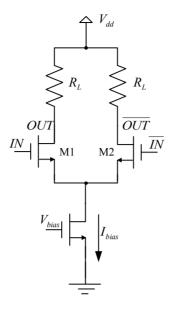

| Figure 2.21: MCML inverter                                                       |      |

| Figure 2.22: CMOS inverter                                                       |      |

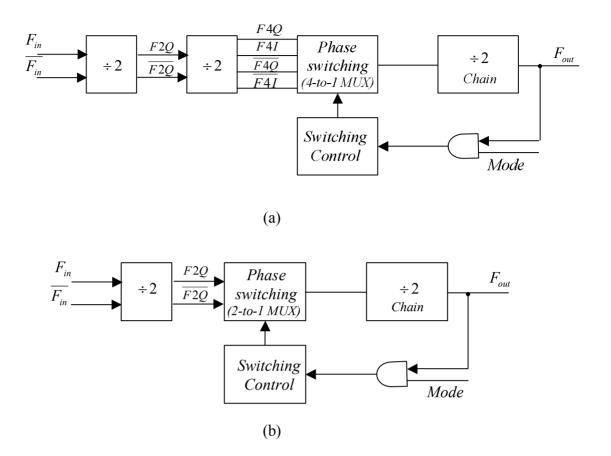

| Figure 3.1: Topology of the prescaler                                            |      |

| Figure 3.2: Dynamic DFFs a) TSPC b) E-TSPC                                       |      |

| Figure 3.3: Operation of divide-by-2 function                                    |      |

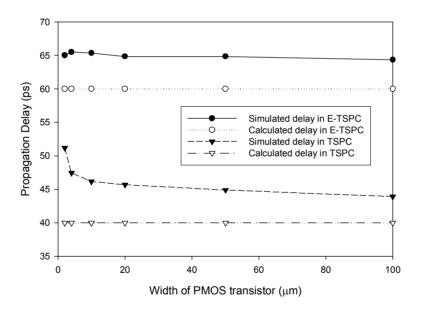

| Figure 3.4: Propagation delays of the TSPC and the E-TSPC divide-by-2 unit.      |      |

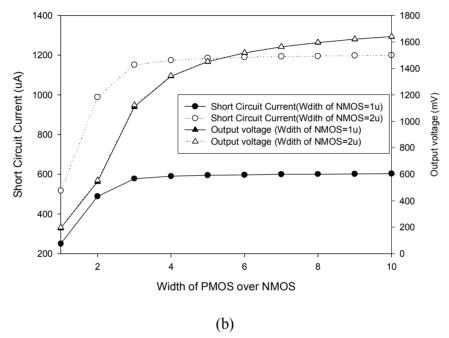

| Figure 3.5: Short circuit in the E-TSPC logic style                              |      |

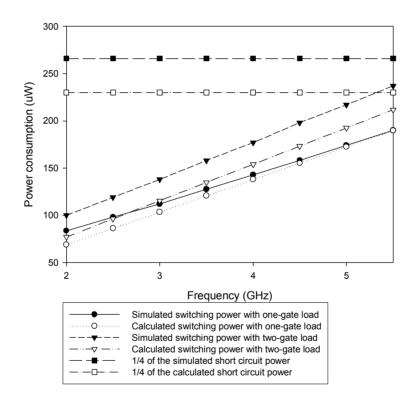

| Figure 3.6: The switching power and short circuit power in one stage of E-       | . 50 |

| TSPC                                                                             | 58   |

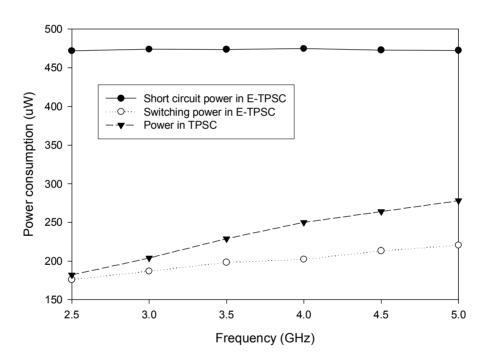

| Figure 3.7: The switching power and short circuit power in the E-TSPC and        |      |

| TSPC unit                                                                        | . 59 |

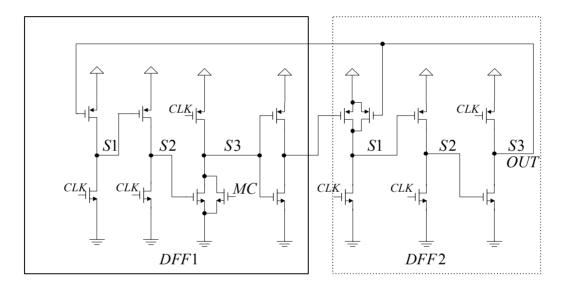

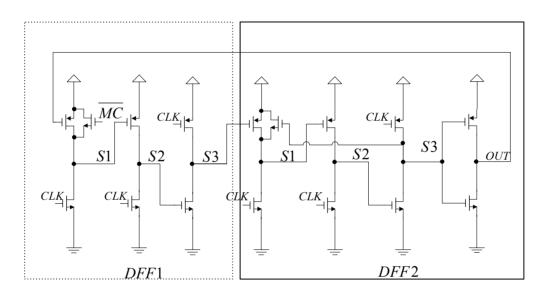

| Figure 3.8: The divide-by-2/3 unit in [99]                                       |      |

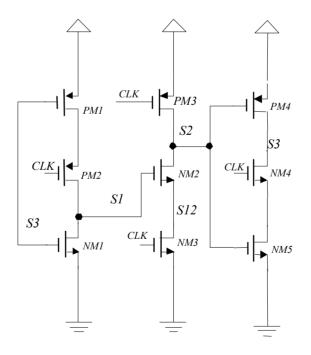

| Figure 3.9: The proposed divide-by-2/3 unit                                      |      |

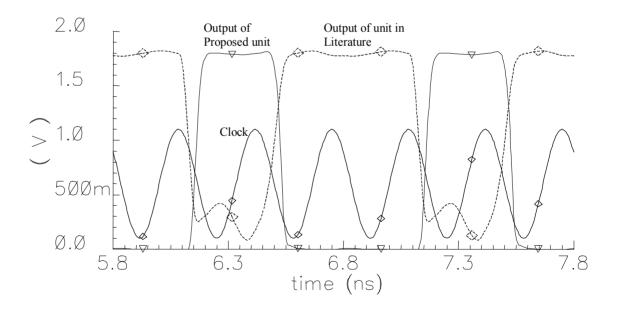

| Figure 3.10: Output divide-by-3 waveform of two divide-by-2/3 units              |      |

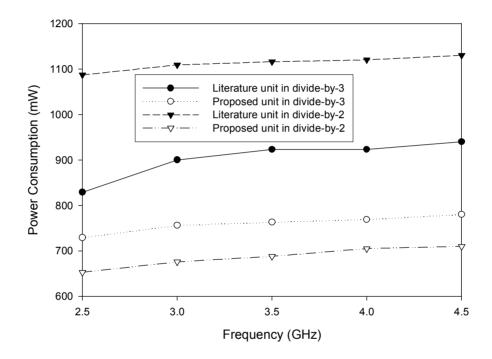

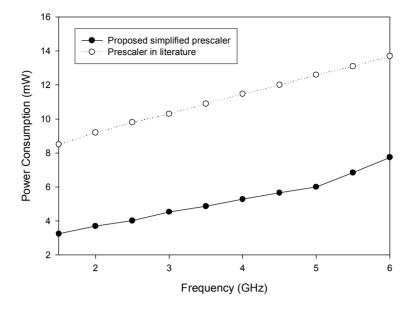

| Figure 3.11: Power consumption vs. operating frequency of the proposed           |      |

| divide-by-2 unit and the divide-by-2 unit in [99].                               | . 63 |

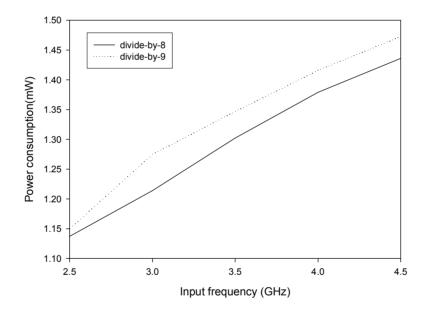

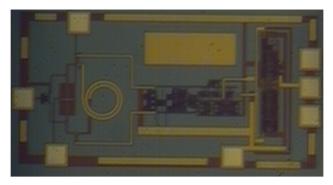

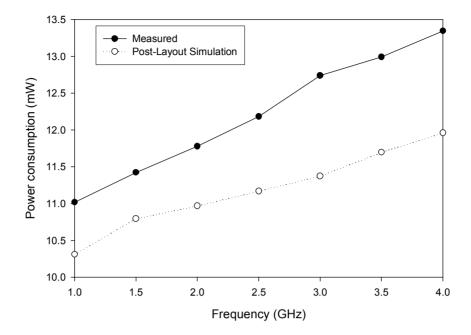

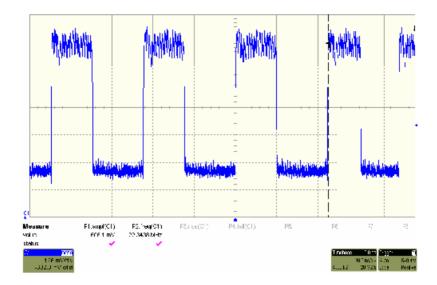

| Figure 3.12: Power consumption of the proposed divide-by-8/9 prescaler           |      |

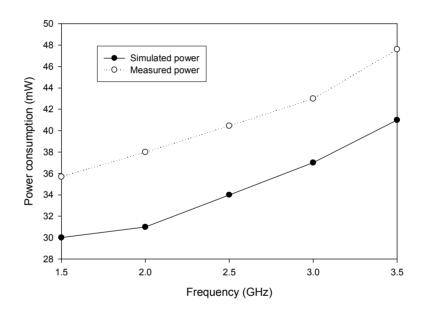

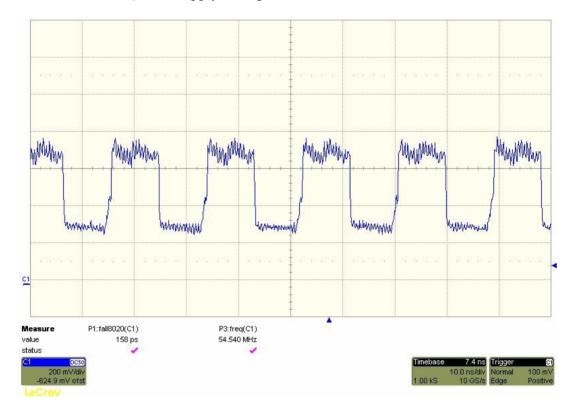

| Figure 3.13: Simulated and measured results of the proposed prescaler with       |      |

| RFMOS                                                                            |      |

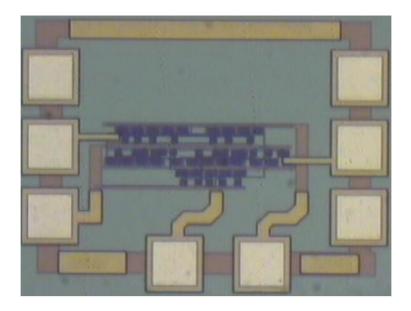

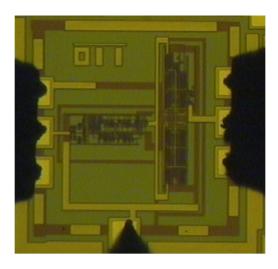

| Figure 3.14: Die photo of the proposed prescaler                                 | . 66 |

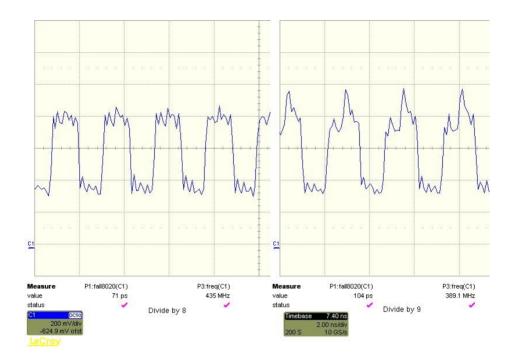

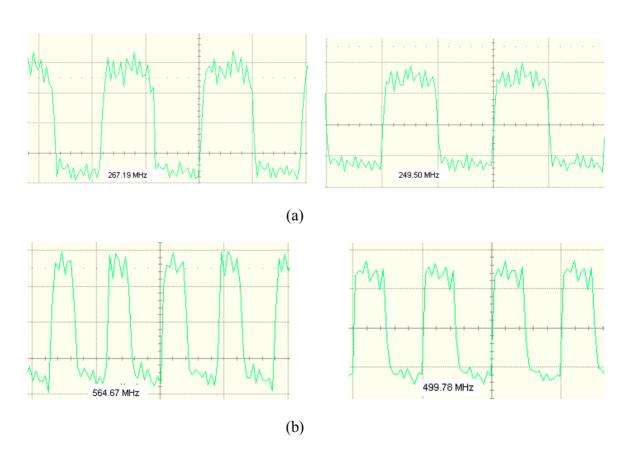

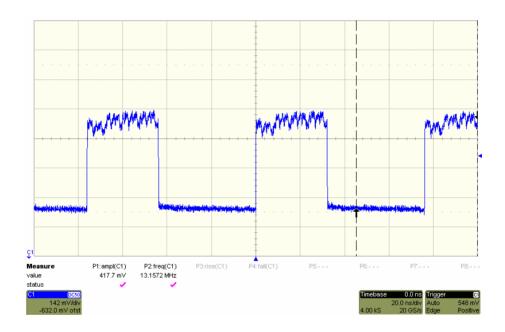

| Figure 3.15: Measured transient results of the proposed divide-by-8/9            |      |

| prescaler                                                                        | . 67 |

| Figure 3.16: The architecture of the phase switching Technique                   | . 70 |

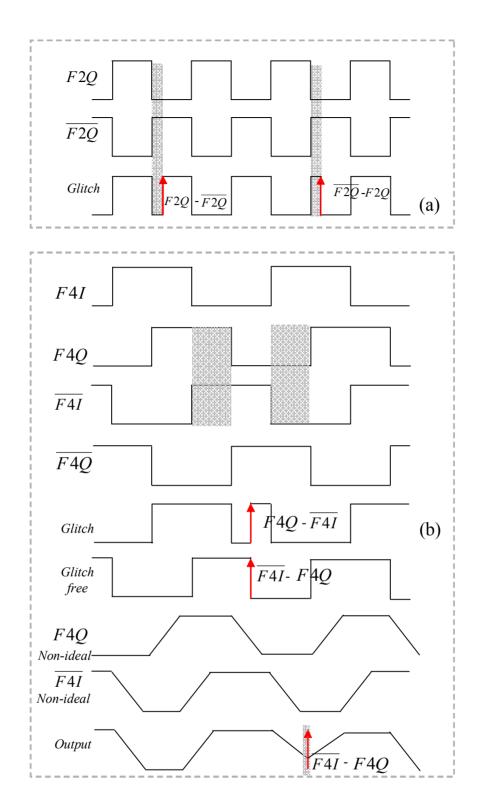

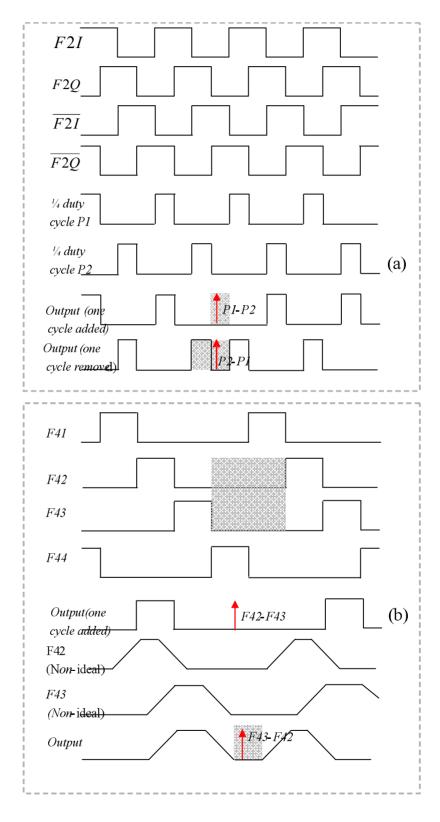

| Figure 3.17: Limitation in the 50% duty cycle phase switching technique          | . 72 |

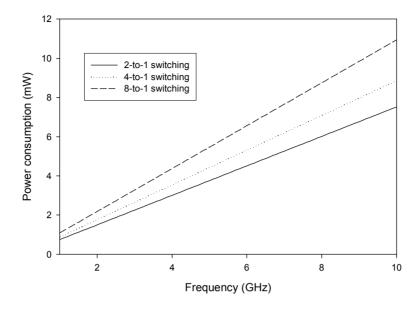

| Figure 3.18: Power consumption vs. operating frequency of the three              |      |

| equations                                                                        | . 77 |

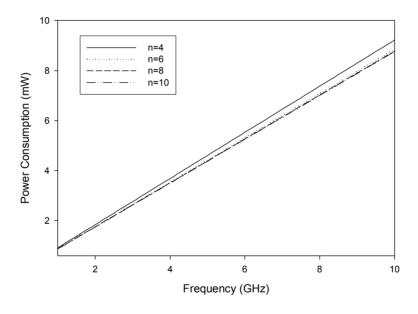

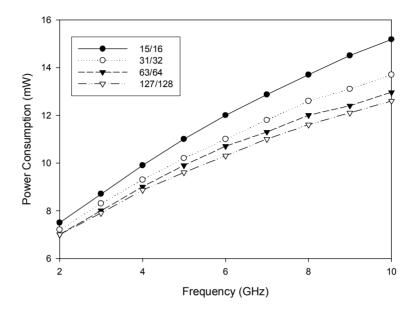

| Figure 3.19: Power consumption vs. operating of 4-to1 switching with different   |      |

| stages                                                                           | . 77 |

| Figure 3.20: The operation of the imbalanced phase switching                     | . 80 |

| Figure 3.21: Divider in [102]                                                    | . 81 |

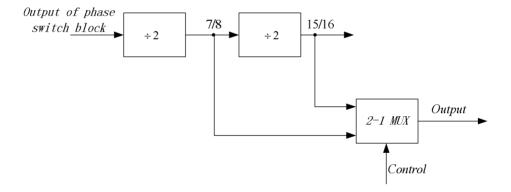

| Figure 3.22: Multi-modulus applications                                          | . 83 |

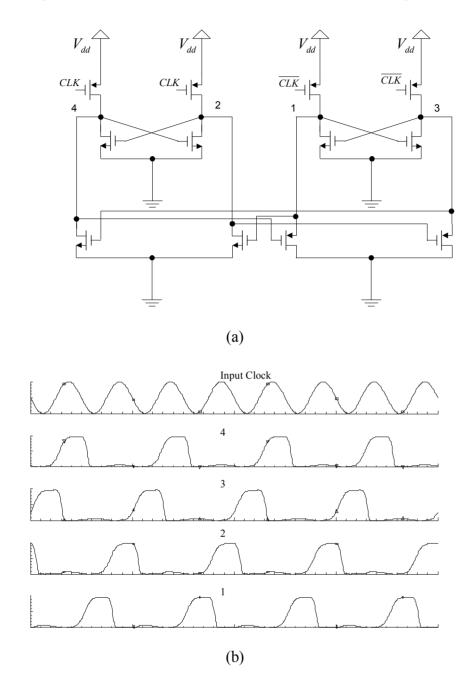

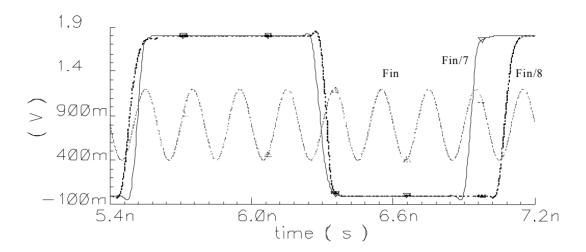

| Figure 3.23: Simulated input and output waveforms of the proposed prescale       | er   |

|                                                                                  | . 84 |

| Figure 3.24: Power consumption vs. operating frequency of the proposed 1 phase switching prescaler and the 4-to-1 phase switching prescaler [40] |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 3.25: Power consumption vs. operating frequency of the proposed                                                                           | 4-to- |

| 1 phase switching prescaler with different division ratios                                                                                       |       |

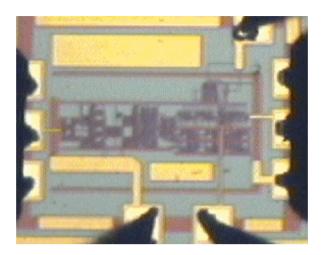

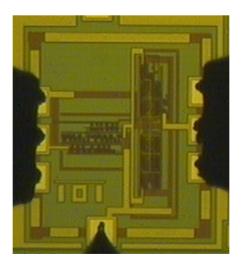

| Figure 3.26: Die photo of the proposed phase switching prescaler                                                                                 | 88    |

| Figure 3.27: Operation of the proposed phase switching prescaler                                                                                 | 88    |

| Figure 3.28 Die photo of the 4-to-1 phase switching prescaler                                                                                    |       |

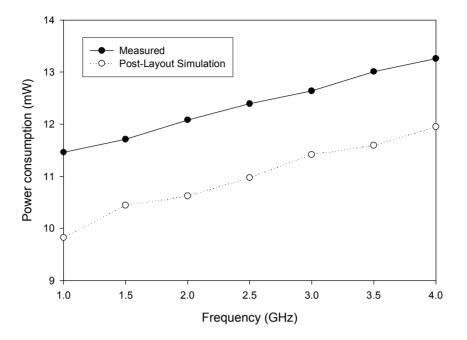

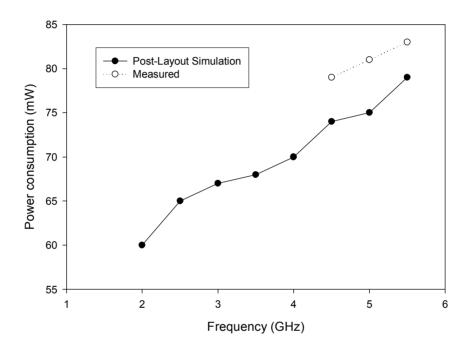

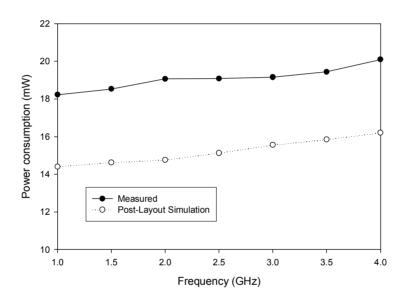

| Figure 3.29 Power consumption vs. operating frequency                                                                                            |       |

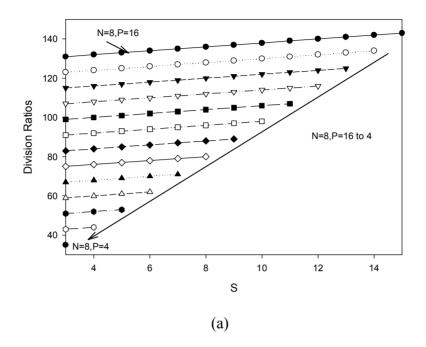

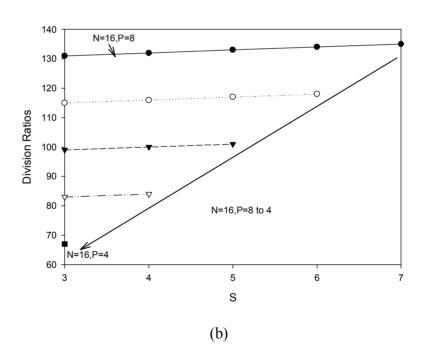

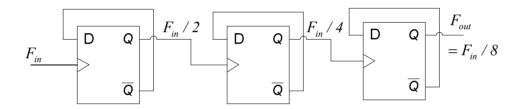

| Figure 4.1: Division ratios available                                                                                                            | 94    |

| Figure 4.2: Toggled TSPC DFF as a divide-by-2 unit                                                                                               | 95    |

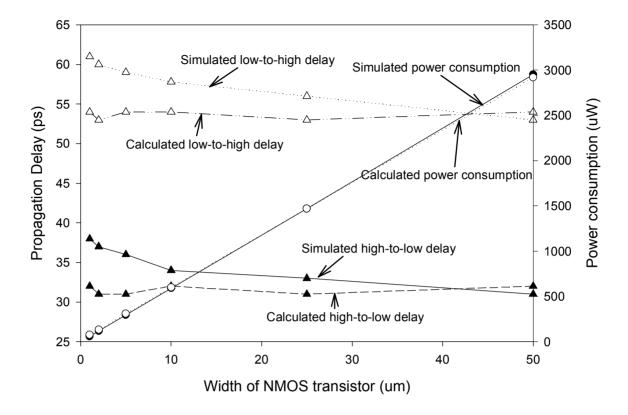

| Figure 4.3: The propagation delay and power consumption of the TSPC div                                                                          | ⁄ide- |

| by-2 unit                                                                                                                                        |       |

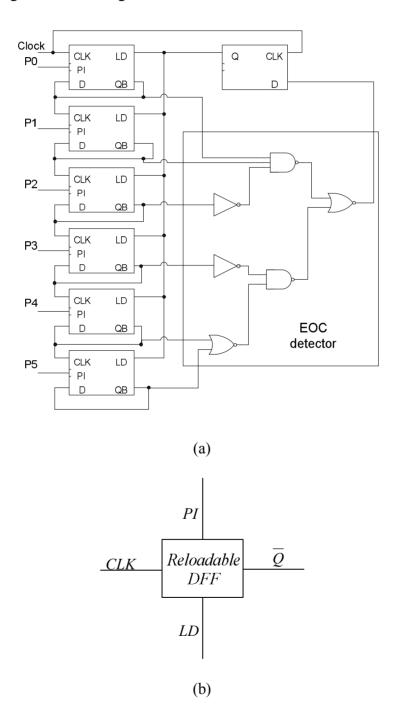

| Figure 4.4: A general topology of the digital counter                                                                                            |       |

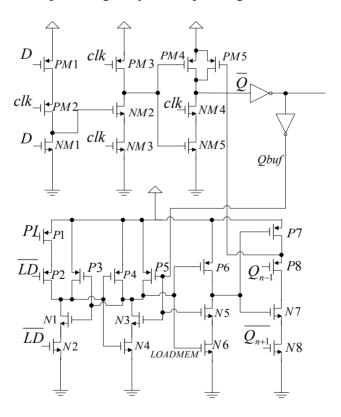

| Figure 4.5: Schematic of the bitcell in [65]                                                                                                     |       |

| Figure 4.6: The propagation delay and power consumption of the bitcell in                                                                        | 100   |

| Figure 4.7: The schematic of the bitcell in []                                                                                                   |       |

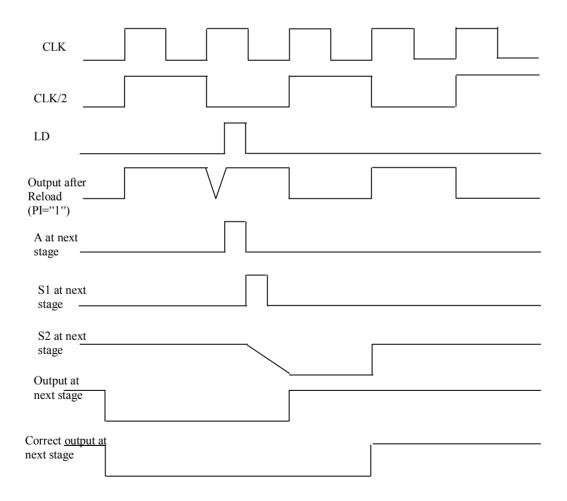

| Figure 4.8: The glitch in the bitcell in [66]                                                                                                    |       |

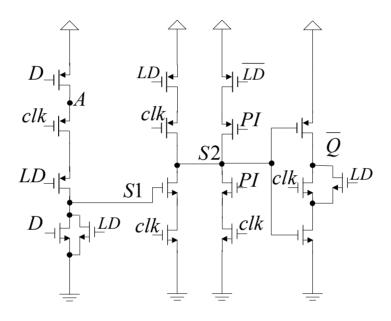

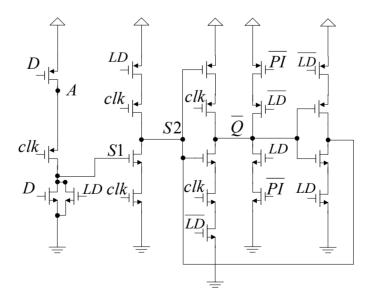

| Figure 4.9: The schematic of the proposed bitcell                                                                                                |       |

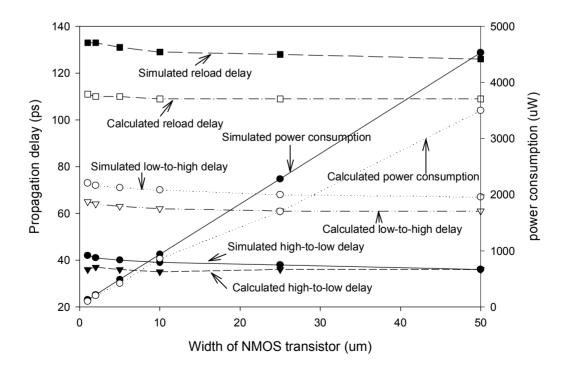

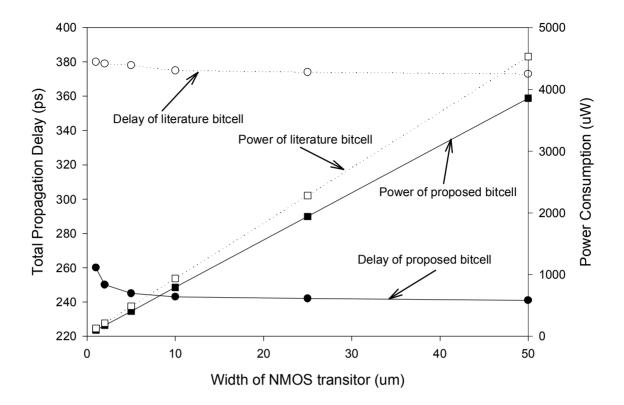

| Figure 4.10: The power consumptions and propagation delays of the bitcel [65] and the proposed bitcell                                           | 105   |

| Figure 4.11: The power consumption of the three bitcells                                                                                         |       |

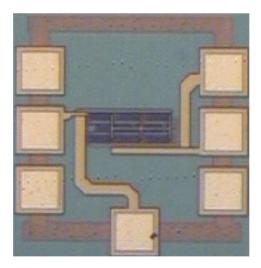

| Figure 4.12: The die photo of the proposed counter                                                                                               |       |

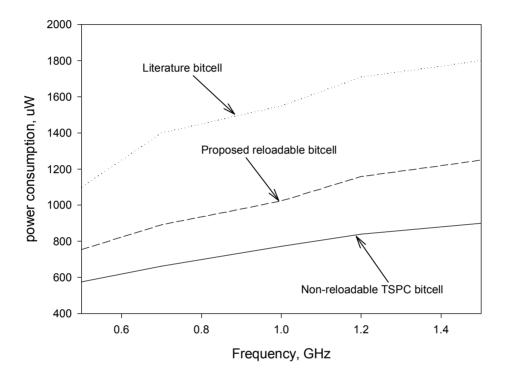

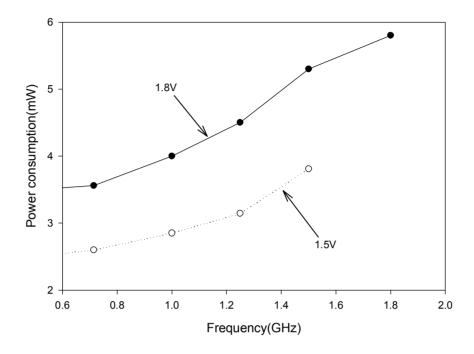

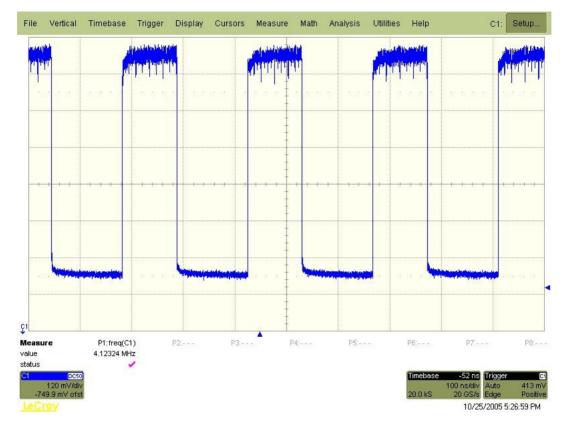

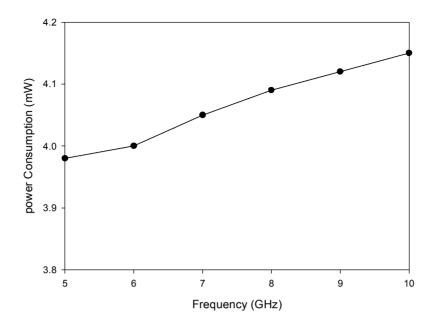

| Figure 4.13: The power consumption vs. frequency of the proposed count                                                                           |       |

| Figure 4.14: The measured transient result of divide-by-33 for the propose                                                                       |       |

| counter                                                                                                                                          |       |

| Figure: 4.15: Die photo                                                                                                                          |       |

| Figure 4.16: Power consumption vs. operating frequency                                                                                           |       |

| Figure 4.17: Output waveform of the frequency divider                                                                                            |       |

| Figure 4.18 The Die Photo of the proposed frequency divider                                                                                      |       |

| Figure 4.19 The output of the frequency divider with 4 GHz inputFigure 4.20 power consumption vs. operating frequency                            |       |

| Figure 4.21 Die photo of the E-TSPC based frequency divider                                                                                      |       |

| Figure 4.22 Output of the frequency divider with 4 GHz                                                                                           |       |

| Figure 4.23 power consumption vs. operating frequency                                                                                            |       |

| Figure 5.1: The Asynchronous divider                                                                                                             |       |

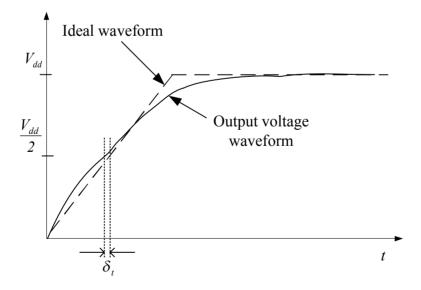

| Figure 5.2: The output voltage waveform and time jitter                                                                                          | 121   |

| Figure 5.3: ISF in a ring oscillator                                                                                                             |       |

| Figure 5.4: Dynamic DFF a) TSPC b) E-TSPC                                                                                                        | 127   |

| Figure 5.5: The time variant slope and NMF in an inverter                                                                                        |       |

| Figure 5.6: Phase noise in the inverter chain                                                                                                    |       |

| Figure 5.7: Phase noise in the TSPC divide-by-2 unit                                                                                             |       |

| Figure 5.8: Phase noise in the three divide-by-2 units                                                                                           | 131   |

| Figure 5.9: The proposed prescaler                                                                                                               | 133   |

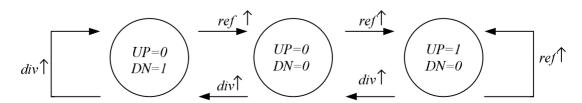

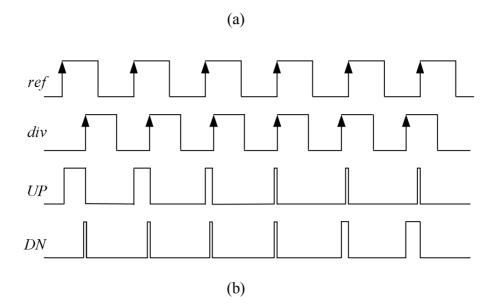

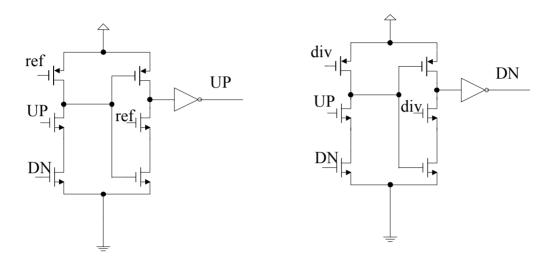

| Figure 6.1: The PFD a) state machine b) Operation                                                                                                | 135   |

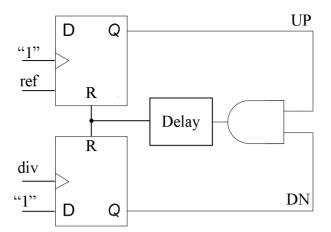

| Figure 6.2: A tri-state PFD                                                                                                                      | 136   |

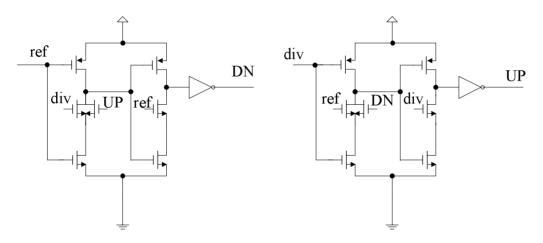

| Figure 6.3: Other PFDs                                                                                                                           |       |

| Figure 6.4: Schematic of the PFD                                                                                                                 |       |

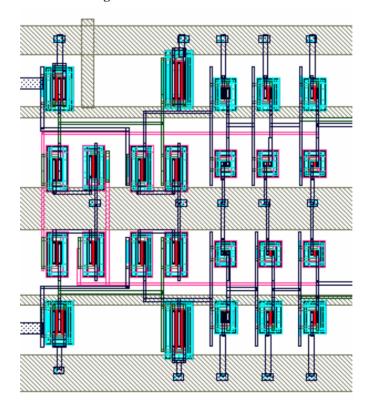

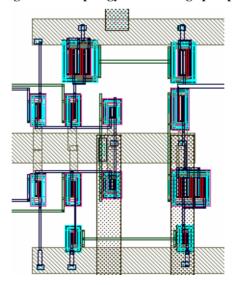

| Figure 6.5: Layout of the PFD                                                                                                                    |       |

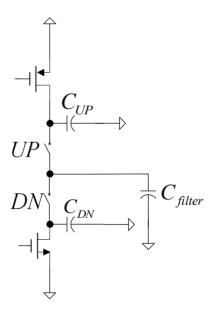

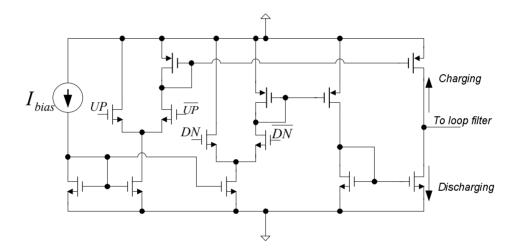

| Figure 6.6: A conventional charge pump                                                                                                           |       |

| Figure 6.7: Topology of the charge pump                                                                                                          | 139   |

| Figure 6.8: Layout of the charge pump                                                                                                            |       |

| Figure 6.9: Layout of the loop filter                                                                                                            |       |

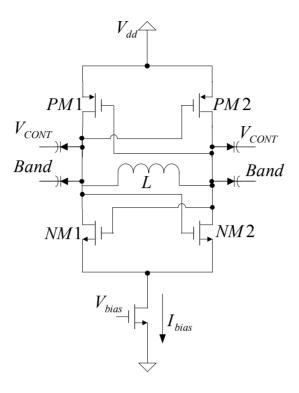

| Figure 6.10: Topology of LC oscillators                                                                                                          |       |

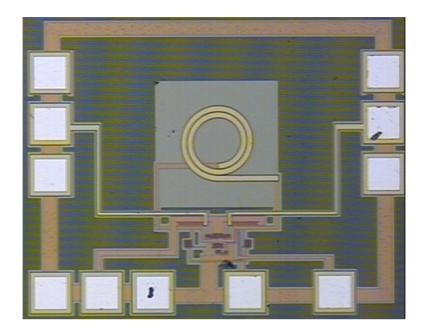

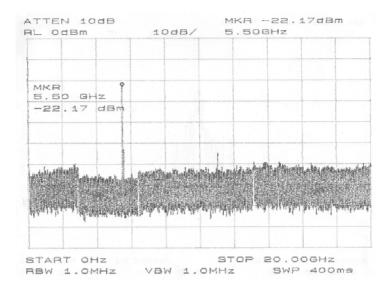

| Figure 6.11: Test chip for a 5 GHz VCOFigure 6.12: Measured output spectrum                                                                      |       |

| riquie 0.12. Medsured outbut spectrum                                                                                                            | 146   |

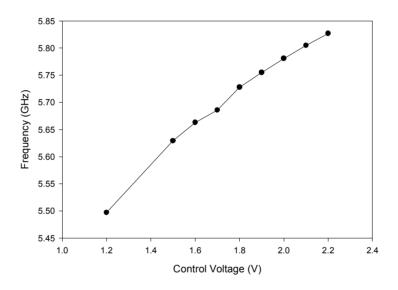

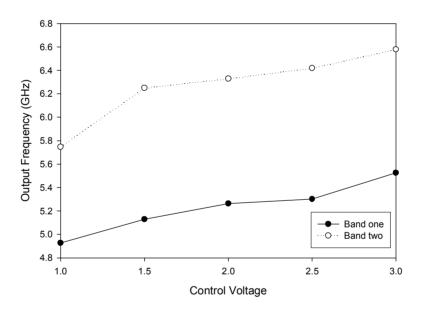

| Figure 6.13: Operating range of the proposed VCO                           | 146 |

|----------------------------------------------------------------------------|-----|

| Figure 6.14: The proposed wide band VCO                                    | 147 |

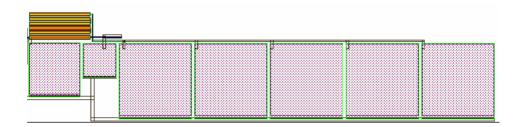

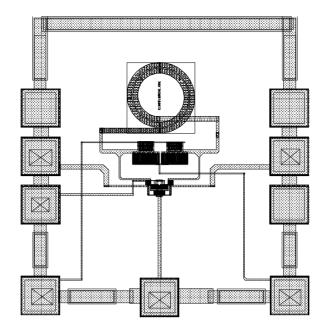

| Figure 6.15: Layout of the proposed VCO                                    | 148 |

| Figure 6.16: Tuning range of the proposed VCO                              | 148 |

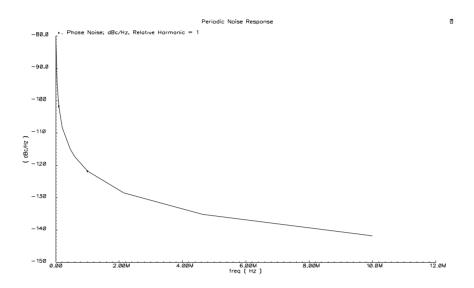

| Figure 6.17: Output phase noise of the proposed VCO                        | 149 |

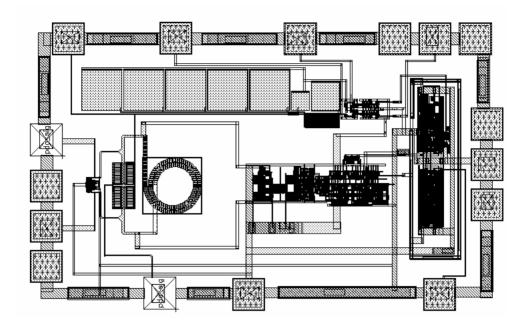

| Figure 6.18: Layout of the proposed frequency synthesizer                  |     |

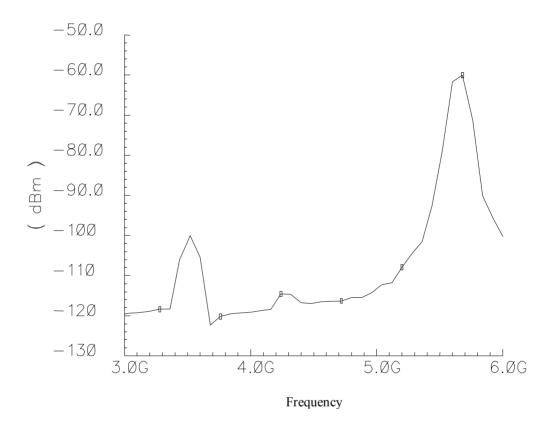

| Figure 6.19: Output spectrum of the proposed PLL                           | 151 |

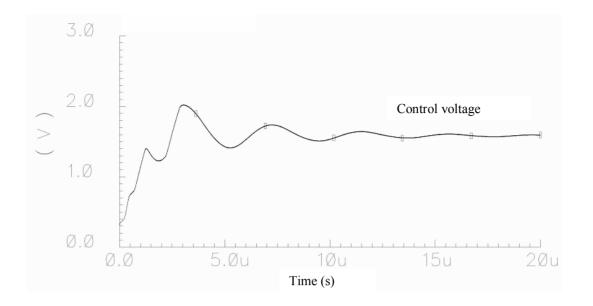

| Figure 6.20: Transient response of the control voltage of the proposed PLL | 152 |

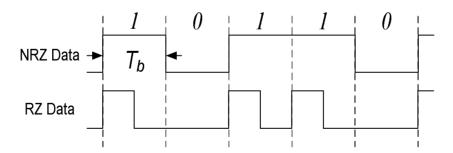

| Figure 7.1: NRZ and RZ bit streams with identical bit patterns             | 154 |

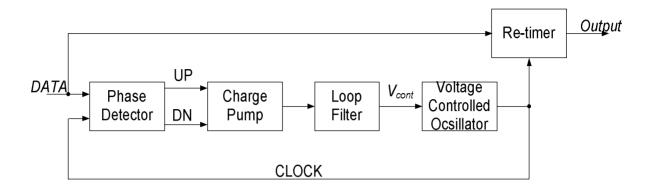

| Figure 7.2: A generic topology of the CDR system                           | 155 |

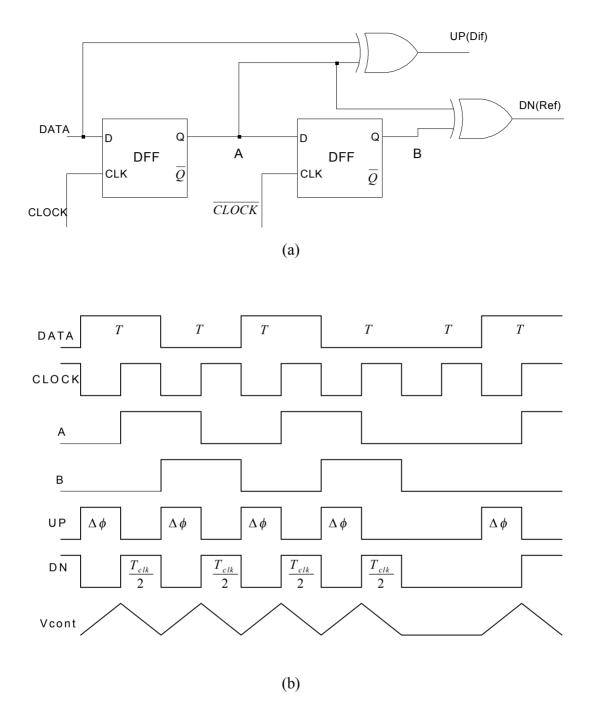

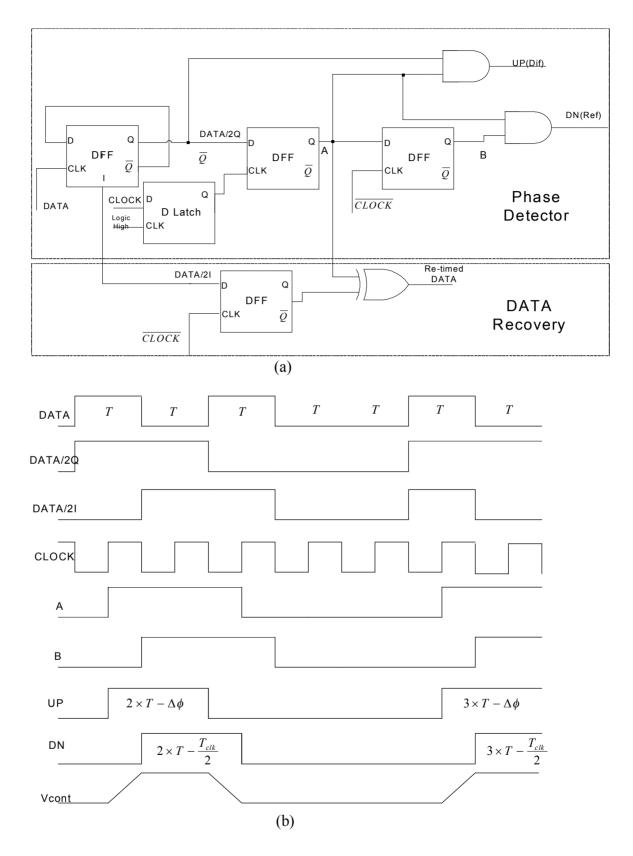

| Figure 7.3: Hogge's PD (a) Architecture (b) Operation                      | 157 |

| Figure 7.4: Half-rate PD in [93]                                           | 159 |

| Figure 7.5: Toggled master slave DFF as an I/Q splitter                    | 162 |

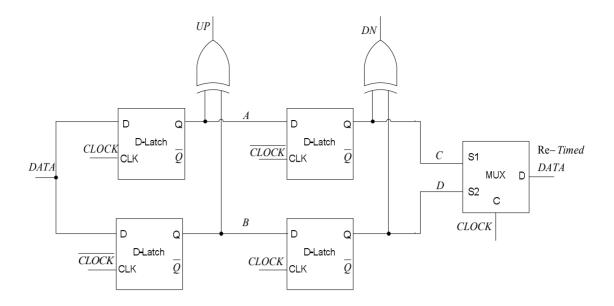

| Figure 7.6: The proposed PD a) topology b) operation                       | 164 |

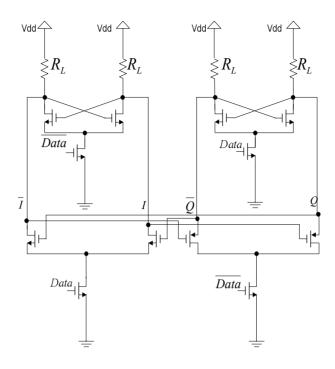

| Figure 7.7: The schematic of the MCML AND gate                             | 165 |

| Figure 7.8: Simulation result of the PD in [93]                            | 166 |

| Figure 7.9: Simulation result of the proposed PD                           | 167 |

| Figure 7.10: Layout of the proposed PD                                     |     |

| Figure 7.11: The inverters of different load                               | 171 |

| Figure 7.12: The divide-by-2 unit in [101]                                 | 172 |

| Figure 7.13: Dynamic MCML                                                  |     |

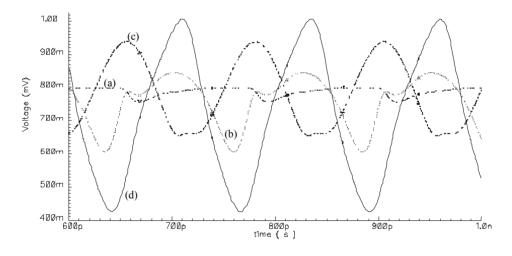

| Figure 7.14: The transient results of the inverters                        | 174 |

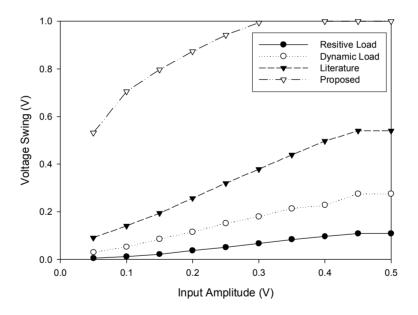

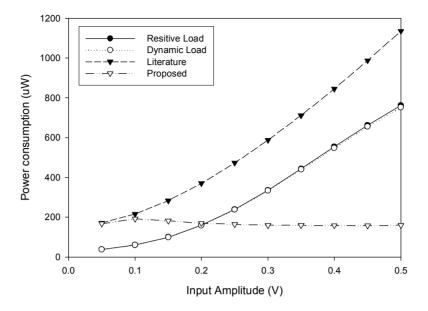

| Figure 7.15: The output voltage swing for the inverters                    | 175 |

| Figure 7.16: Power consumptions of the inverters                           | 176 |

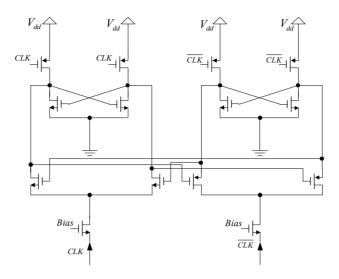

| Figure 7.17: The proposed frequency divider                                | 176 |

| Figure 7.18: The transient result of the proposed frequency divider        | 177 |

| Figure 7.19: Power consumption vs. operating frequency of the two dividers | 178 |

| Figure 7.20: Layout of the frequency divider                               | 178 |

| Figure 7.21: Power consumption vs. operating frequency                     | 179 |

#### List of Tables:

| Table 1.1: WLAN standards                                           | 5   |

|---------------------------------------------------------------------|-----|

| Table 3.1: Comparison to other published prescalers                 |     |

| Table 4.1: Center frequencies for HIPERLAN II and UNII              | 111 |

| Table 6.1: Design Specification                                     | 141 |

| Table 7.1: Comparison between proposed PD and other PDs reported in |     |

| Literature                                                          | 168 |

#### **Chapter 1**

#### Introduction

#### 1.1 Background and motivation

Phase-Locked Loops (PLLs) are widely used in communication systems. Thus, low cost and high performance PLLs are the key components of modern highly integrated communication transceivers.

In recent years, the rapid development of wireless communications has lead to an increasing demand for low cost lower power and high performance Integrated Circuits (ICs). The typical applications of wireless communication devices include cellular phones, global positioning systems and Wireless Local Area Network (WLAN), etc. Numerous communication standards have been proposed to define and optimize certain applications. For example, for voice applications, the Global System for Mobile communication (GSM), Code Division Multiple Access (CDMA), Personal Communication Systems (PCS) and 3G communications are proposed. Different WLAN standards, such as the IEEE 802.11 a/b/g standards, HIPERLAN I/II, Bluetooth are proposed to provide various high data rate wireless applications. The operating frequencies of these communication standards range from a few hundred MHz to several GHz.

The recent rapid expansion of the wireless communication market has driven world-wide electronic and communication device providers to develop small size, low cost, and high performance mobile terminals. Until recently, the wireless transceivers are implemented using the BJT, or GaAs process [1] [2]. The recent advancement of the CMOS technology makes it possible now to design and

implement Radio Frequency Integrated Circuits (RFICs) using the low cost CMOS processes [3].

The PLL is commonly used as a frequency synthesizer as well as to stabilize the LO in wireless transceivers. From a stable reference frequency, a PLL can synthesize carriers at precise frequencies. Modern communication systems always operate at closely allocated channels at very high frequencies. Therefore, a frequency synthesizer must have an excellent frequency purity to ensure a good noise performance in the up-converted or down-converted signals.

The volume of data over the telecommunication networks has increased rapidly with the increase of the internet data traffic [4]. As the network volume increases the capacity of the transmission links which connect the network switching nodes must be also increased. The major method is to use the Wavelength Division Multiplexing (WDM) in the optical fibre. One example is the Synchronous Optical NETwork (SONET), a data communication standard which defines optical carrier levels and electrical signals for the fiber-optic based transmissions. For example, the SONET OC-192 has a transfer rate of 9953.28 Mb/s. Its full clock rate is almost 10 GHz. PLLs are also used in data communications as Clock Data Recovery (CDR) circuits. At the receiver end of the channel, the digital data has to be sampled at the same rate as that of the transmitter end. The clock is recovered from the input data stream by a PLL based recovery circuit.

In all these applications, the phase noise performance of the PLL has a great impact on the system performance. Excessive phase noise causes cross-talk in wireless communications and increases the Bit Error Rate (BER) in data communications. A synchronous system also needs a low clock skew signal for increasing throughput. Thus a high frequency low jitter and low clock skew PLL is

prerequisite.

In the design of transceivers, there is a clear trend towards a full integration of the Radio Frequency (RF) front end on a single die for the purposes of low cost and low power. However, there are many difficulties in the realization of the fully integrated multi-GHz CMOS PLLs with high performances.

The first difficulty is the operating frequency. The relatively low  $f_T$  of MOSFETs limits the maximum operating frequencies of the high frequency building blocks such as the VCO and the frequency divider in a frequency synthesizer. Furthermore, there are other challenging requirements, for example, the low phase noise performances in the CMOS technology, the smaller die size, and the full integration.

Another issue related to the high operating frequency is the power consumption. In the design of wireless communication terminals, low power consumption means long battery life, which is a major consideration in the market of consumer electronics. For example, for a wireless terminal in the turn-on state, RF front end is working all the time, while the digital baseband past is working only 5% of the turn-on duration. Therefore, most of the power consumption comes from the RF front end. A PLL in the RF front end contributes significantly to the overall power consumption. In the PLL, especially in the ultra-high speed digital circuits, i.e., the frequency divider in the frequency synthesizer and the phase detector in the CDR, the power consumption increases linearly with the increase in operating frequency. As a result, such high frequency building blocks dissipate a great portion of the total power consumption in the RF front-end.

Through the development of modern wireless communications, many standards coexist in the similar bands, while different standards are adopted in different regions. Therefore, a transceiver system which is able to operate over a wide band for multi-standard applications is highly desired.

#### 1.2 Wireless LAN and CDR standards

There are many popular wireless LAN standards proposed by global and regional organizations, e.g. Institute of Electrical and Electronics Engineers (IEEE), European Telecommunication Standards Institute (ETSI). The different standards can be classified by the operating bands. For example, the IEEE 802.11b/g and the Bluetooth work at 2.4 GHz, while the HIPERLAN I/II and the IEEE 802.11a are located in the 5-6 GHz band.

The Bluetooth standard was proposed by Ericsson in 1994. It includes a system solution consisting of hardware, software and interoperability requirements. The Bluetooth wireless technology uses the globally available unlicensed ISM radio band of 2.4 GHz, from 2.4 GHz to 2.479 GHz, in 1 MHz spacing channels. It uses the Frequency-Hopping Spread-Spectrum (HFSS) technology to mitigate the effects of interference and to increase the number of bits transmitted while expanding the bandwidth. The first generation of the Bluetooth specification has a secure exchange of data up to a rate of about 1 Mbps. IEEE 802.11b emerged in 1999 and has become the most popular wireless networking standard. It also operates in the 2.4 GHz radio band and uses the Direct Sequence Spread Spectrum (DSSS) technique to disperse the data frame signal over a relatively wide (30 MHz) portion of the 2.4 GHz band [5]. As a result, the immunity to radio frequency interference is improved. The IEEE 802.11a standard operates in the 5-6 GHz band using the Orthogonal Frequency Division Multiplexing (OFDM) technique for the packet based networks. Its maximum bit rate can reach 54 Mbps. The Media

Access Control (MAC) layer in the IEEE 802.11a is an extension of the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) protocol employed in wired LANs [6].

The IEEE 802.11g standard incorporates the merit of the IEEE 802.11a standard but operates in the 2.4 GHz band. It has the same modulation scheme and MAC layer as that of the IEEE 802.11a standard. By using the OFDM modulation, its data rate increases to 54 Mbps as well.

The ETSI proposed its own standards in Wireless LAN, namely the HIPERLAN. The HIPERLAN I standard supports a maximum data rate of 23.5 Mbps with a total available bandwidth of 150 MHz. HIPERLAN II increases the maximum data rate to 54 Mbps with a total available bandwidth of 455 MHz. It has a similar definition in the physical layer as that of the IEEE 802.11a standard but it supports time critical services in the MAC layer [7].

Table 1.1: WLAN standards

| Standard  | Carrier     | Number   | Channel Spacing | Total     | Maximum   |

|-----------|-------------|----------|-----------------|-----------|-----------|

|           | Frequency   | of       | (MHz)           | Bandwidth | Data Rate |

|           | (GHZ)       | Channels |                 | (MHz)     | (Mbps)    |

| IEEE      | 5.150-5.350 | 12       | 20              | 300       | 54        |

| 802.11a   | 5.725-5.825 |          |                 |           |           |

| IEEE      | 2.4-2.479   | 11       | 5               | 79        | 11        |

| 802.11b   |             |          |                 |           |           |

| IEEE      | 2.4-2.479   | N/A      | 5               | 79        | 54        |

| 802.11g   |             |          |                 |           |           |

| Bluetooth | 2.4-2.479   | 79       | 1               | 79        | 1         |

| HIPERLAN  | 5.15-5.35   | 19       | 20              | 455       | 54        |

| Type II   | 5.470-5.725 |          |                 |           |           |

The state of art for the time division multiplexed (TDM) bit streams in the Dense

Wavelength Division Multiplexing (DWDM) system is the 10 Gb/s SONET OC-192 standard and its European counterpart, the synchronous data hierarchy (SDH) STM-64 [4]. The standard bit rate for these two standards is 9.95328 Gb/s with the non-return-to-zero (NRZ) coding.

#### 1.3 Thesis organization

This thesis is organized into twelve chapters. Chapter 1 provides an introduction to the problem addressed, and an outline of the thesis.

The theory, mathematical description and operation of a PLL will be discussed in Chapter 2. The existing design techniques for VCO and frequency divider are reviewed.

Chapter 3 presents two high-speed prescalers. One is dynamic divide-by-8/9 prescaler, which is based on the E-TSPC logic. By analyzing and optimizing the power consumption in the E-TSPC divide-by-2 unit, a new divide-by-2/3 unit in the prescaler design is proposed. The performance of the prescaler based on this unit is silicon verified. The other prescaler is based on an imbalanced phase switching technique. The performance of the new prescaler is silicon verified.

Chapter 4 describes a GHz digital counter and the integration of a 5-6 GHz wide band high resolution frequency divider implemented with the high speed low power digital counter. The frequency divider is able to cover both the HIPERLAN II and the IEEE 802.11a standards.

Chapter 5 analyzes the phase noise in the TSPC based frequency dividers, while the analysis of the phase noises is verified by the simulation.

In Chapter 6, a frequency synthesizer based on the new frequency divider and VCO is presented.

In Chapter 7, a new linear full rate phase detector for SONET OC-192 is proposed. It has a better linearity over a wider frequency range compared to the results reported in the literature. Finally, a new 1 V 10 GHz divide-by-2 unit is proposed. This divide-by-2 unit using a dynamic MCML inverter is able to operate at higher frequencies with a lower power consumption.

Chapter 8 provides the conclusion of this dissertation.

#### **Chapter 2**

#### **Overview of Phase-Locked Loops**

The frequency synthesizer is an essential block in multi-channel wireless transceivers. Phase-Locked Loop (PLL) based frequency synthesizers are commonly used as local oscillators (LOs) in wireless receivers to down-convert the carrier frequency to a lower Intermediate Frequency (IF), or up-convert the IF signal to the RF signal [8]. PLLs are also used in clock data recovery circuits, e. g. SONET OC-192 applications [9] [10]. In this chapter, the operation of a basic PLL and its transfer function are analyzed, and the implementation of the PLL-based frequency synthesizer is described and discussed. The role and requirements of PLLs in the application of frequency synthesizers for wireless LAN are presented. Finally, the most challenging high frequency blocks, the VCO and the frequency divider are reviewed.

#### 2.1 Building blocks of PLLs

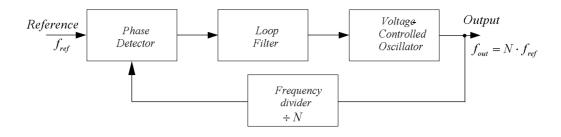

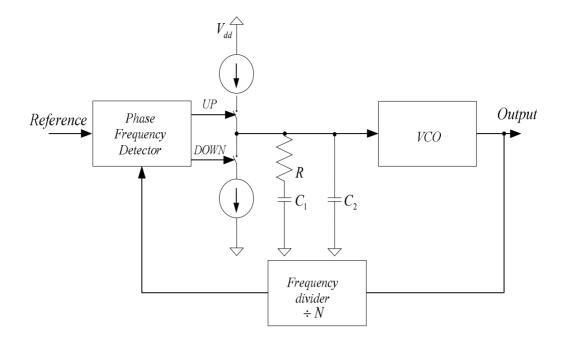

A PLL is a negative feedback system which operates on the excess phase of periodic signals. A general topology of a PLL is shown in Figure 2.1 [11]. It is formed by a phase detector (PD), a loop filter, and a voltage controlled oscillator (VCO). If it is used as a frequency synthesizer, a frequency divider is also added between the VCO and PD.

Figure 2.1: A general topology of a PLL

The phase detector compares the phase of the input reference signal and that of the oscillator's output signal or of the frequency divider's output in a frequency synthesizer. The output signal of the phase detector is a function of the phase difference between these two signals. The PD can be implemented in many methods, for example, the analog multiplier, XOR gate, Phase Frequency Detector (PFD), etc. The detailed analysis of the performance of different topologies can be found in [12]. The loop filter is usually implemented with a low pass filter that filters the output of the phase detector to produce the VCO's control voltage. In many applications, a charge pump is used before the loop filter to change the digital voltage output of the phase detector to the charging/discharging current. The filter is required to suppress the voltage ripple and to reduce the spurious tones and distortions of the RF oscillator.

The VCO produces an output signal, with an angular frequency,  $\omega_{VCO}$ , which is controlled by the output voltage of the loop filter,  $V_{cont}$ , according to the following relationship:

$$\omega_{VCO}(t) = \omega_0 + K_{VCO}V_{cont} \tag{2.1}$$

where  $\omega_0$  is the center angular frequency of the VCO and  $K_{VCO}$  is the gain of the voltage-controlled oscillator. The output phase of the VCO is:

$$\theta_{VCO}(t) = K_{VCO} \int V_{cont}(t) dt \tag{2.2}$$

The frequency divider is used to extend the functionality of the loop to a frequency synthesizer. It divides the output frequency of the VCO by a ratio of N. In the stable condition, the output frequency of the PLL will be:

$$f_{out} = f_{ref} N (2.3)$$

The division ratio, N can be changed to synthesize the different frequencies. If N is an integer, the PLL is called an integer-N frequency synthesizer.

The PLL is in a locked state when the phase difference at the PD output is constant with time and as a result these two input frequencies of the PD are equal. In the locked condition, all signals in the loop reach a steady state. The phase detector produces an output signal whose DC value is proportional to the phase difference of its two input signals. The loop filter suppresses the high-frequency components in the PD's output and generates a constant control voltage for the VCO. The VCO oscillates at a frequency which is equal to the reference frequency multiplied by the division ratio of the frequency divider.

If the output frequency step has to be smaller than  $f_{\it ref}$ , N can be a non-integer. Such a topology is called a fractional frequency synthesizer, which is usually used in high resolution and small channel spacing transceivers.

#### 2.2 Linear model of PLLs

Although a PLL is normally a non-linear system because of the non-linearity of the phase detector, the VCO, and the divider, it is usually analyzed using a linear model when the loop is in a locked state [13].

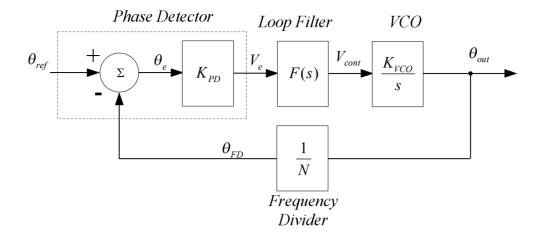

Figure 2.2: A linear model for PLL

The models for all building blocks in a PLL are summarized in Figure 2.2. For applications without a frequency divider, N is an integer with a minimum value of one. The transfer function of a PLL in S domain is given by:

$$H(s) = \frac{\theta_{out}}{\theta_{ref}} \tag{2.4}$$

where  $\theta_{out}$  and  $\theta_{ref}$  are the phases of the output signal and input reference signal respectively.

The phase detector produces the phase error signal which is equal to:

$$V_{e}(s) = K_{PD}[\theta_{ref}(s) - \theta_{FD}(s)] = K_{PD}\theta_{e}(s)$$

(2.5)

where  $\theta_{FD}(s)$  and  $\theta_e(s)$  are the phase signals at the frequency divider output and the phase detector output respectively while  $K_{PD}$  is the gain of the phase detector.

Consequently, the phase error signal generates the control voltage of the VCO which is given by:

$$V_{cont}(s) = V_e F(s) \tag{2.6}$$

where F(s) is the transfer function of the loop filter.

The output phase is given by:

$$\theta_{out}(s) = \frac{K_{VCO}V_{cont}(s)}{s} \tag{2.7}$$

The output phase is then divided by N before it is fed back to the phase detector.

$$\theta_{FD}(s) = \frac{\theta_{out}(s)}{N} \tag{2.8}$$

Therefore, the transfer function of the PLL can be obtained:

$$H(s) = \frac{\theta_{out}(s)}{\theta_{ref}(s)} = \frac{K_{PD}K_{VCO}F(s)}{s + \frac{K_{PD}K_{VCO}F(s)}{N}}$$

(2.9)

By the same method, the transfer function for the phase error signal is given by:

$$\frac{\theta_e(s)}{\theta_{ref}(s)} = \frac{s}{s + \frac{K_{PD}K_{VCO}F(s)}{N}}$$

(2.10)

The PLL transfer function has a low-pass characteristic with a gain of N, while the phase error transfer function has a high-pass characteristic.

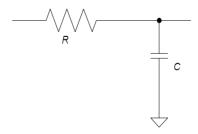

Figure 2.3: A lag RC filter

The dynamics of the PLL are decided by the transfer function of the loop filter F(s). For example, if a simple lag RC filter as shown in Figure 2.3 is used, the filter will have a transfer function of:

$$F(s) = \frac{1}{(1 + sRC)} \tag{2.11}$$

The transfer function of the PLL is given by:

$$H(s) = \frac{\theta_{out}(s)}{\theta_{ref}(s)} = \frac{NK_{PD}K_{VCO}}{s^2 NRC + sN + K_{PD}K_{VCO}}$$

(2.12)

It can be mapped to a control system with a transfer function of [12]:

$$H(s) = \frac{N\omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2}$$

(2.13)

where

$$\omega_n = \sqrt{\frac{K_{PD}K_{VCO}}{NRC}}$$

and  $\xi = \frac{1}{2}\sqrt{\frac{N}{K_{PD}K_{VCO}RC}}$

$\omega_n$  and  $\xi$  are defined as the natural frequency and damping factor respectively.

This topology has limitations in the applications of PLLs. The natural frequency and the damping factor cannot be selected independently by selecting the values of R and C. Therefore, there will be a trade-off in determining these two parameters in the design of a frequency synthesizer.

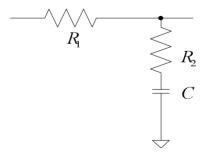

Figure 2.4: A passive lag-lead filter

If a resistor is added in series with the capacitor as Figure 2.4 shows, the transfer function of the filter changes to:

$$F(s) = \frac{1 + \tau_2 s}{1 + \tau_1 s} \tag{2.14}$$

where

$$\tau_2 = R_2 C$$

and  $\tau_1 = (R_1 + R_2)C$

The transfer function of the PLL is therefore:

$$H(s) = \frac{s\omega_n (2\xi - \frac{N^2 \omega_n}{K_{PD} K_{VCO}}) + N\omega_n^2}{s^2 + 2\xi \omega_n s + \omega_n^2}$$

(2.15)

where

$$\omega_n = \sqrt{\frac{K_{PD}K_{VCO}}{N\tau_1}}$$

and  $\xi = \frac{1}{2}\sqrt{\frac{K_{PD}K_{VCO}}{N\tau_1}(\tau_2 + \frac{N}{K_{PD}K_{VCO}})}$

For this topology, the natural frequency and damping factor can be determined independently.

The charge pump circuit is used to improve the performance of the PLL. The charge pump PLL has advantages compared with the traditional design. Its static phase error is zero, and the mismatch is negligible [14].

Figure 2.5: A Charge-pump PLL

Figure 2.5 shows the topology of a charge pump PLL with a 2<sup>nd</sup> order loop filter. It has been widely used for its outstanding advantages [13]. The output signals of the phase frequency detector, the *UP* and *DOWN* signals are used to drive the charge pump. The charge pump changes the control voltage of the VCO by applying positive and negative charges to the filter. The transfer function of the charge pump is given by:

$$\frac{I_d(s)}{\theta_e(s)} = \frac{I_{CP}}{2\pi} \tag{2.16}$$

where  $I_d(s)$  and  $\theta_e(s)$  are the Laplace transform of the average current over a cycle and of the phase difference output of the PFD,  $I_{CP}$  is the charging/discharging current.

The 2<sup>nd</sup> order loop filter has a transfer function of:

$$F(s) = \frac{1 + \tau_2 s}{s(C_1 + C_2)(1 + \tau_1 s)} \tag{2.17}$$

where

$$\tau_2 = RC_2$$

and  $\tau_1 = \frac{C_1C_2}{C_1 + C_2}$

Hence the transfer function of the PLL is found to be:

$$H(s) = \frac{K_{PD}K_{VCO}(\frac{1+s\tau_2}{C_1+C_2})}{s^3 + (\frac{1}{\tau_1})s^2 + (\frac{K_{PD}K_{VCO}\tau_2}{N(C_1+C_2)})s + (\frac{K_{PD}K_{VCO}\tau_2}{N(C_1+C_2)\tau_1})}$$

(2.18)

Approximating it with a second-order expression, the simplified transfer function is given by [15]:

$$H(s) \cong \frac{K_{PD}K_{VCO}(\frac{1+s\tau_2}{N(C_1+C_2)})}{s^2 + (\frac{K_{PD}K_{VCO}\tau_2}{N(C_1+C_2)})s}$$

(2.19)

The natural frequency and damping factor can be obtained:

$$\omega_n = \sqrt{\frac{K_{PD}K_{VCO}}{N(C_1 + C_2)}}$$

and  $\xi = \frac{RC_2}{2}\omega_n$

The poles are located at  $-\zeta \omega_n \pm \omega_n \sqrt{\zeta^2 - I}$

#### 2.3 The performance of PLLs

The PLL is frequently used as a frequency synthesizer in the RF receiver. The design of the frequency synthesizer must follow the specifications that determine the quality of the generated signal and its effects on the received signals.

#### 2.3.1 Tuning range and frequency resolution

The tuning range of the frequency synthesizer is usually designed to cover the operating frequency range of the selected standard taking into account the selection of the system architecture. The tuning range sets the minimum requirement for the operating range of the VCO in the frequency synthesizer. The frequency resolution of the synthesizer is normally designed according to the channel spacing of the specifications. In an integer-N PLL, the output frequency resolution is determined by the input reference frequency. The IEEE 802.11a standard has a channel spacing of 20 MHz. The center frequencies and channel spacing are listed in Table 1.1. The channel spacings and center frequencies for these standards vary even when they are located in the similar band. For example, the center frequencies of the IEEE 802.11b and Bluetooth can be expressed as (2402+k) MHz and  $(2412+k\times5)$  MHz respectively, where k is an integer.

#### 2.3.2 Phase noise

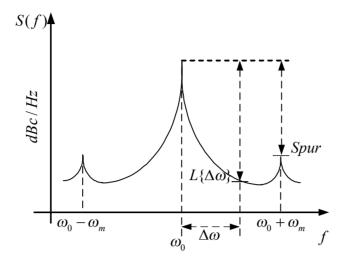

The phase noise is one of the most important parameters for the characterization of the synthesizer. The phase noise in the frequency synthesizer has a great impact over the noise performance of the RF receiver [16]. All frequency synthesizers rely on analog circuits, which introduce various types of nonidealities. The output of a PLL is not an ideal sine wave of an oscillating frequency,  $\omega_0$ . A typical output spectrum of a PLL is shown in Figure 2.6:

Figure 2.6: The output spectrum of a PLL

Phase noise  $L\{\Delta\omega\}$  is defined as the ratio of the noise power in a bandwidth of 1 Hz at an offset frequency  $\Delta\omega$  to the carrier power  $P_{carrier}$ . The result is a single sided spectral noise density in the unit of dBc/Hz.

$$L\{\Delta\omega\} = 10\log\frac{P_{noise}}{P_{carrier}}$$

(2.20)

In a PLL, the output of the VCO also has spurs. The energy is also concentrated on frequency other than the main oscillating frequency. The major sources of the ripple in the PLL are: the leakage currents in the filter and the charge-pump; the mismatch in the charge pump up and down current sources [17]. For the phase detector, the output clock is switched on and off periodically. The pull up and pull down currents in the charge pump introduce the current injection,  $\Delta I_{CP}$ , which will cause ripple in the output of the VCO.

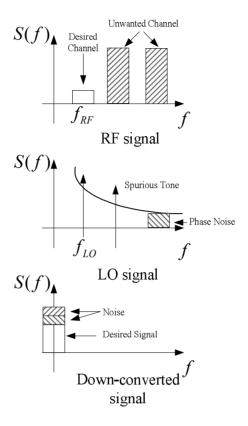

Phase noise and spurious signals affect the performance of the down-converted signal as shown in Figure 2.7 [18]. The section of the phase noise from the local oscillator noise that falls over the adjacent channel is down-converted on top of the desired signal. This output noise will degrade the signal-to-noise ratio (SNR) of the

down-converted signal. Therefore, the phase noise performance of the frequency synthesizer must be able to meet the requirement of the WLAN standards.

Figure 2.7: Effects of phase noise in a receiver

The requirement of the phase noise in a receiver is given by [8]:

$$L\{\Delta\omega\} < P_{sig\_\min}(dBm) - P_{blk\_\max}(dBm) - f_{BW}(dBHz) - SNR(dB)$$

(2.21)

where  $P_{sig\_min}$  is the minimum received signal,  $P_{blk\_max}$  is the maximum blocking signal,  $f_{BW}$  is the bandwidth, and SNR is the minimum required SNR.

For example, in the Bluetooth applications, the phase noise in 3 MHz offset should below -116 dBc/Hz [19].

The spurious signal of the frequency synthesizer has a similar effect in the receiver's performance. Therefore, the maximum spurious level in the frequency synthesizer is given by:

$$spur\{\Delta\omega\} < P_{sig-min}(dBm) - P_{blk-max}(dBm) - SNR(dB)$$

(2.22)

However, the power spectrum of the spur is different from that of the phase noise. As shown in Figure 2.6, it is a pair of frequency components at a distance of  $\pm f_m$  from the carrier frequency  $f_0$ .

#### 2.3.3 Settling time

Another requirement in the design of the frequency synthesizer is the requirement of settling time. The WLAN standards define the requirement of switching between the different channels, e.g., in the HIPERLAN II, the required switching time for the change of the carrier is less than 1 ms [7].

In the frequency synthesizer, the covering of different channels is achieved by changing the division ratio of the frequency divider, for example, from the initial division ratio N to  $(N+\Delta N)$  to switch to another channel. This will cause successive changes in the phase error, then in the control voltage and in the VCO's output frequency. After the feedback, the PLL settles down again. The time required for this complete procedure is called the settling time. Theoretically, the settling time is large and has an exponential behavior. Therefore, the specified output frequency error tolerance,  $\varepsilon$ , is introduced. The settling time,  $t_s$  of the PLL can be defined as:

$$t_s = \{t_s : |f_{out}(t) - f_{out}(\infty)| < \varepsilon\}$$

(2.23)

where  $f_{out}(t)$  is the output frequency at time t, and  $f_{out}(\infty)$  is the steady-state frequency of the VCO.

The analysis of the transient response can be obtained from a linear model if  $\Delta N$  is much smaller than N. For example, for a simple loop filter PLL which has a transfer function of Equation 2.13, the change of the output of the PLL due to a

change of  $\Delta N$  can be obtained:

$$\Delta f_{out}(\infty) = \Delta N f_{ref} \frac{(2\xi \omega_n + \omega_n^2)}{s(s^2 + s\xi \omega_n + \omega_n^2)}$$

(2.24)

The settling time for the new division ratio is given by:

$$t_s = \left| L^{-1} \left\{ \Delta f_{out}(s) - \Delta f_{out}(\infty) \right| < \varepsilon \tag{2.25}$$

#### 2.4 Voltage Controlled Oscillators

The voltage-controlled oscillator (VCO) is one of the most critical blocks in a frequency synthesizer. It mainly determines the phase noise performance of a frequency synthesizer. The performance parameters of the VCO include the tuning range, tuning linearity, output amplitude, and phase noise.

The tuning range of the VCO is determined by the application of the VCO. Some margins in the tuning range may be needed due to the process and temperature variations. The tuning linearity describes the nonlinear tuning characteristics of the VCO. Because the gain of the VCO can not be constant over the operating range, the output frequency can not change linearly with the control voltage. The output amplitude is another consideration. For less sensitivity to noise, a higher amplitude is desired. However, there will be trade-offs with the supply voltage, power dissipation and tuning range. Finally, the output signal purity, which is measured by the phase noise, is a key consideration in the application of a frequency synthesizer.

To design a VCO with good performances such as low phase noise and low power consumption, the fundamentals must be first understood. These include the basic principles of the oscillation, the relation between the power consumption and

device dimensions, effects from the quality factor of the devices specifically the LC tank and the identification of the noise source.

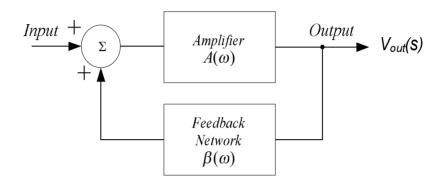

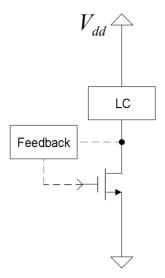

An oscillator can be described as a positive feedback system which amplifies its own signal at a selected frequency  $\omega_0$ , as shown in Figure 2.8.

Figure 2.8: Feedback diagram of an oscillator

$A(\omega)$  and  $\beta(\omega)$  are the gains of the amplifier and the feedback network respectively.

The transfer function of the oscillator is:

$$A = \frac{A(\omega)\beta(\omega)}{1 - A(\omega)\beta(\omega)} \tag{2.26}$$

According to Barkhausen's Criteria, the system will oscillate at  $\omega_0$  when the closed loop gain approaches infinity under the following conditions: (1) the open loop gain is equal to unity, i.e.  $A(\omega_0)\beta(\omega_0)=1$ , and (2) the total phase shift of the loop is equal to  $2\pi n$ , where n is an integer or  $\text{Im}\{A(\omega_0)\beta(\omega_0)\}=0$ . In order to ensure the startup of the oscillation in presence temperature and process variations, the small signal loop gain is typically chosen to be 2-3 times of the required value.

# 2.4.1 Ring oscillators

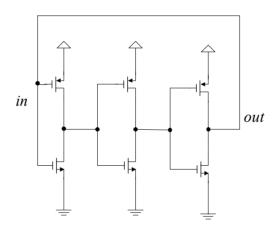

Ring oscillators are widely used in PLL frequency synthesizers and clock recovery circuits. The implementation of the ring oscillator in the CMOS technology is easier since only transistors are required; hence a smaller silicon area is needed. Another advantage of the ring oscillator over the LC oscillator is its larger tuning range. In the ring oscillator, the Barkhausen's Criteria are achieved by the positive feedback of the output signal to the input. It is usually designed by cascading an odd number of single-ended inverters in a loop configuration as shown in Figure 2.9.a.

(a)

Figure 2.9: A three stage ring oscillator a) topology b) linear model

The tuning of the oscillator frequency can be obtained by many methods, e. g. using variable capacitors, or variable supply voltage, or the current-starved method [20]. The linear model for a ring oscillator is shown in Figure 2.9.b [21]. In this model, each stage contains a single pole with a DC gain of  $-GmR_0$ , the transfer function of the ring oscillator is therefore given by:

$$H(j\omega_0) = \left(\frac{-GmR_0}{1 + j\omega_0 R_0 C_0}\right)^N \tag{2.27}$$

where N is the number of the stages.

In this case, N is equal to 3. To meet the requirement of oscillation, the total phase shift is  $180^{\circ}$  and the loop gain should be equal to unity:

$$\left(\frac{-GmR_0}{1+j\omega_0R_0C_0}\right)^3 = 1\tag{2.28}$$

$$tan^{-1}(\omega_0 R_0 C_0) = 60^0 \tag{2.29}$$

From these two equations, we can get  $GmR_0 = 2$ .

The oscillating frequency of the ring oscillator is decided by either the 3-dB bandwidth or the time delay of each stage [22]. For the large signal analysis, the oscillating frequency is given by:

$$f_0 \approx \frac{1}{2Nt_{delay}} \approx \frac{I}{2NC_L V_p} \tag{2.30}$$

$t_{delay}$  is the time delay for each delay cell, I is the current passing through each delay cell,  $C_L$  is the load capacitance of each stage and  $V_p$  is the peak output voltage.

The oscillating frequency of a ring oscillator can be tuned by changing the load capacitance, equivalent resistance or transconductance of MOS transistors to change the delay since the delay of each stage is decided by the RC constant. The speed limitation of the ring oscillator is set by the transconductance to parasitic capacitance ratio. For a given supply voltage, increasing W/L of the MOS transistors to increase the transconductance can not increase the oscillating frequency significantly since the parasitic capacitances increase as well.

The ring oscillator suffers a relatively high phase noise level compared to that of the LC oscillator. The switching activities in a ring oscillator introduce a lot of disturbances in the oscillator. Moreover, the multiple stage design also has an accumulated noise level. As a result, the ring oscillator is not suitable in the high performance RF systems for its poor noise performance compared to that of the LC counterpart. A general discussion of the ring oscillator phase noise is given in [20] and the resulting phase noise is given by:

$$L(\Delta\omega) = \frac{3\Gamma^2_{rms}}{8\pi^2 \Delta f^2} \frac{\overline{i^2}_n / \Delta f}{C_L^2 V_p^2}$$

(2.31)

Where  $\Gamma_{rms}$ ,  $\Delta f$ ,  $\overline{i^2}_n/\Delta f$ , and  $C_L$  are the root-mean square of Impulse Sensitivity Function (ISF), the offset frequency, the total noise power density and the output load capacitance respectively.

#### 2.4.2 LC oscillators

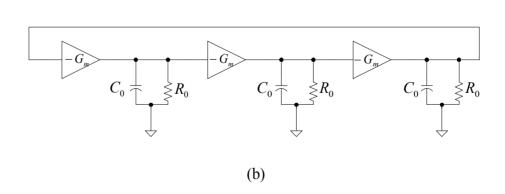

An oscillator employing an LC tank offers a higher operating frequency and lower phase noise compared with that of a ring oscillator. Therefore, it is widely used in most modern RF systems even it requires a larger silicon area and has a smaller tuning range.

Figure 2.10: The general topology of a LC oscillator

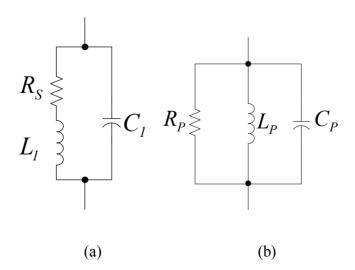

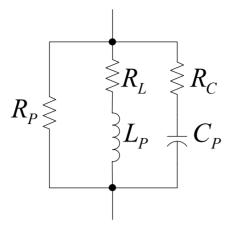

Figure 2.10 shows the general topology for an LC oscillator. It consists of an active circuit and an LC resonator. As the LC resonator is the key block in the VCO, it is instructive to review the basic properties of RLC circuits. Figure 2.11 shows a simple model of the LC tank, both in the series combination and the parallel configuration. However, in a real circuit, due to the parasitic resistors in the inductor and capacitor, the above model is modified as in Figure 2.12.

Figure 2.11: Conversion of a tank to three parallel components

Figure 2.12: A complex model for the LC tank

At the resonant frequency, the imaginary part of the admittance of the LC tank is zero, thus the resonant frequency is given by:

$$\omega_0 = \frac{1}{\sqrt{L_p C_p}} \sqrt{1 - \frac{R_L^2 C_p}{L_p}}$$

(3.32)

The lossy LC-tank resonates at a lower frequency than that of the ideal tank formed by the ideal inductor and capacitor only.

The quality factor of a resonator using an inductor with a series resistor is given by:

$$Q_p = \frac{\omega L}{R} \tag{3.33}$$

For an ideal resonator, the value of R is equal to zero, and Q is infinite. In other words, the ideal resonator would not need to have active devices and no energy is needed to maintain the oscillation once the oscillation starts. However, in practice the Q of an on-chip inductor is quite low, typically from 3 to 20. The operating frequency is normally below 10 GHz. This is mainly due to their parasitic series resistance and the substrate loss [23].

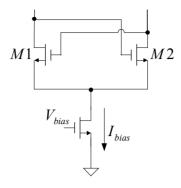

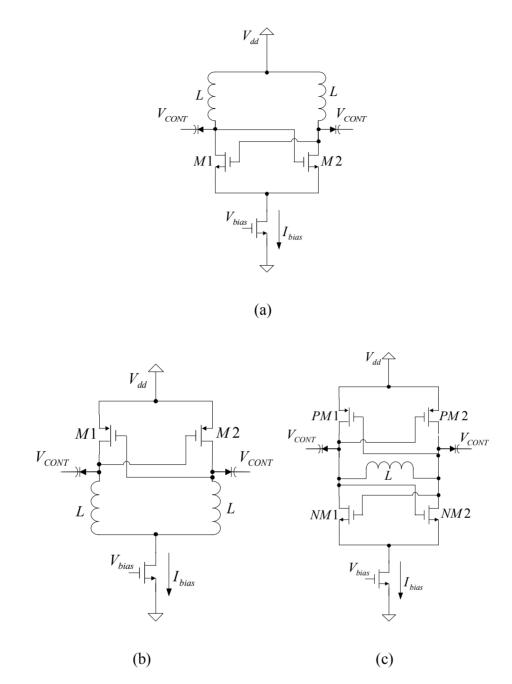

Figure 2.13: The cross-coupled structure

Due to the existance of the parasitic resistor, the energies in the capacitor and inductor are lossy and therefore, a negative resistance is needed to cancel the resistance therefore compensate the energy loss. In an LC Oscillator, the negative resistor is usually implemented by a cross-coupled differential structure as shown in Figure 2.13.

The negative resistance can is given by:

$$R = -\frac{2}{g_m} \tag{2.34}$$

where  $g_m$  is the transconductance of the transistors M1 and M2.

To guarantee the oscillation, the transconductance is usually designed to be twice the required value. Hence, with enough negative resistance, the cross-coupled pair can compensate for the loss of the LC tank and maintain a stable oscillation.

Once the requirement of the transconductance has been determined, the power dissipation of the VCO can be obtained. The power consumption is given by:

$$Power = (I_{M1} + I_{M2})V_{dd} (2.35)$$

while

$$I_{M1} = I_{M2} = \mu C_{ox} \frac{W}{2L} (V_{gs} - V_{th})^2$$

(2.36)

The resonant frequency of an LC oscillator is determined by the inductance and capacitance of the LC tank. Therefore, the tuning of the oscillating frequency can be carried out by changing the inductance or capacitance. Varactors are widely used as voltage-controlled variable capacitors. If a larger tuning range of the output frequency is required, a larger tuning ratio of the capacitance of the varactor is needed. There are several varactor options for the frequency tuning, such as PN-junction varactors, inversion mode varactors and accumulation mode varactors.

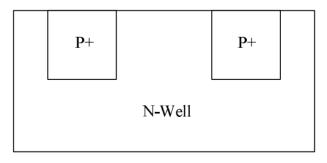

## The PN-junction varactor

The PN-junction varactor is formed by the P+ diffusion on an N-Well as shown in Figure 2.14.a. Figure 2.14.b shows the simulation result of the C-V curve based on the Chartered Semiconductor Manufacturing (CSM) model for the 0.18 µm CMOS technology [24]. The PN-junction should be reverse-biased. The PN-junction varactor cannot be optimized to achieve both a large tuning range and high quality factor [25].

P-substrate

(a)

Figure 2.14: PN-junction varactor a) structure b) capacitance over voltage

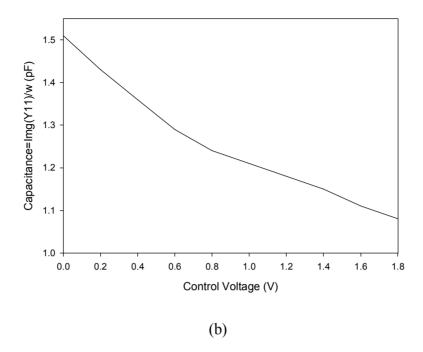

#### The Accumulation-mode varactor

In a standard CMOS process, typical PN-junction varactors have very low Q values. The A-MOS varactor is implemented by using a P-channel MOSFET in a P-well/substrate or an n-Channel MOSFET in an N-well.

(a)

Figure 2.15: Accumulation-mode varactor a) structure b) capacitance over voltage

Figure 2.15 shows the varactor based on the NMOS transistor where the drain and source are connected together. By varying the gate-to-well voltage from a positive voltage above the flatband voltage to a negative value, the device goes from the deep accumulation region to the deep depletion region while the capacitance of the varactor drops. The accumulated charge on the surface of the silicon decreases with the drop of Vg until it reaches the flatband voltage. If Vg is less than the flatband voltage, the surface of the device undergoes the depletion. As a result, an additional capacitance is formed in series with the oxide capacitance which causes a decrease of the overall capacitance. The A-MOS varactor's Q varies significantly its tuning range due to the variation of its resistance value. However, even with the large variation of Q, in the worst case, the Q of an A-MOS varactor is still better than that of the PN-junction varactor. To achieve a better Q, more gate fingers should be used and the gate length should be minimized. The A-MOS

varactor is however less linear over the tuning voltage than the PN-junction varactor. As a result, the gain of the VCO using the A-MOS varactor is more non-linear [26].

#### **Inductors**

The inductor is a key element in determining the performance of an LC oscillator. The on-chip spiral inductor is constructed based on the lithography, where the geometry of coils is well-controlled. There are several topologies of the spiral inductor available, for example, square, hexagonal and circular. The square spiral inductor has been widely used for its easy layout. However, it has larger loss compared with the circular spiral inductor. Figure 2.16 shows a typical geometrical layout of a spiral inductor using the top metal layer and returning to outside through the underpass metal layer. The design parameters of an inductor are given by the number of turns (n), the metal width (w), the metal to metal spacing (s), the inner-hole diameter  $(d_{in})$  and the outer diameter  $(d_{out})$ .

Figure 2.16: Geometry of a spiral inductor

The lumped element model is widely used to simulate the performance of an inductor [27] [28]. A typical  $\pi$ -equivalent model is shown in Figure 2.17.

Figure 2.17: The lump element model of an on-chip inductor

It consists of nine components, where L is the total inductance produced by the metal winding and mutual coupling,  $R_L$  is the total loss of the inductor,  $C_{ox}$  is the capacitance between inductor and substrate,  $R_s$  and  $C_s$  are the parasitic resistance and capacitance of the substrate.

The total inductance of the spiral inductor is the sum of the self-inductance and the mutual-inductance [29]. It is given as:

$$L_{total} = L_{self} + M_{+} - M_{-} \tag{2.37}$$

where  $L_{\it self}$  is the total sum of the self-inductance of all conductor segments,  $M_+$  and  $M_-$  are the inductances due to positive and negative coupling between conductors respectively.

The mutual inductance is introduced by the magnetic coupling between the conductors. The same direction of the current flow results a positive coupling,

otherwise, a negative coupling is introduced. The detailed calculation of the mutual inductance is summarized in [30].

The efficiency of an inductor is defined by the Q, which is given by [31]:

$$Q = 2\pi \frac{energy\ stored}{energy\ lost\ per\ cycle}$$

(2.38)

Equation 2.38 defines the energy stored in the LC tank and provides an indication of how much energy is lost as it is being transferred between the capacitor and the inductor. The energy stored in the LC tank is actually the sum of the average magnetic and electric energies. However, for a silicon spiral inductor, only the energy stored in the magnetic field is of interest. Any energy stored in the form of electric field by the parasitic capacitance is counterproductive [32]. Hence, Q is proportional to the net magnetic energy stored, which is equal to the difference between the peak magnetic and electric energies:

$$Q = 2\pi \frac{Peak\ Magnetic\ Energy - Peak\ Electric\ Energy}{Energy\ Loss\ Per\ Cycle} \tag{2.39}$$

The detailed analysis about the on-chip spiral inductor can be found in [24] [30].

In a standard CMOS technology, the quality factor of the on-chip inductor is generally smaller than that of the capacitor. Therefore, the quality factor of an LC-tank is crucial to VCO designs.

#### 2.4.3 Noise performance of an oscillator

The figure of merit for the noise performance of an oscillator is the phase noise which measures the short-term frequency stability of an oscillator. It is defined as [20]:

$$L(\Delta\omega) = 10\log\frac{P_{sideband}(\omega_0 + \Delta\omega)}{P_{carrier}}$$

(2.40)

where  $P_{carrier}$  and  $P_{sideband}(\omega_0 + \Delta\omega)$  are power of the carrier and the total power in a 1-Hz bandwidth at an offset of  $\Delta\omega$  from  $\omega_0$  respectively. The unit is dBc/Hz where dBc indicates a measurement in dB relative to the carrier power.

In the design of an oscillator, the noise sources can affect both the amplitude and phase of the output signal. But the amplitude noise can be reduced by the amplitude limiting mechanism in the oscillator [20]. Therefore, amplitude noise is usually negligible. Phase noise can be regarded as the fluctuation of the zero crossing locations of a signal. The detailed explanation of this fluctuation can be found at [20]. The phase noise output is caused by both internal and external sources. The internal noise is the main source, which is caused by the noise of the oscillator's active elements, and the up-conversion of the baseband noise to the oscillator band. The external VCO noise includes the substrate coupling of unwanted signals, power supply fluctuations due the switching activity of digital/analog circuits. Noise coupled onto the control voltage applied across the varactor of the LC-tank varies the tank capacitance and hence the resonant frequency. This can be viewed as the frequency modulation (FM) noise mechanism which translates the low-frequency noise to the oscillating frequency. These phase noises on the VCO control line can expressed as a narrow-band FM which is given by [33]:

$$L(f_m) = 10\log(\frac{P_{noise}}{P_{carrier}}) = 10\log[\frac{(K_{VCO}V_{cont})^2}{2\Delta f^2}]$$

(2.41)

From this equation, it is observed that phase noise contribution from the control PLL output can be minimized by reducing the VCO's gain.

Because the amplitude of phase noise is small compared with the magnitude of the carrier signal, phase noise is approximated as a linear function of frequency. For example, a simple Linear Time Invariant (LTI) model can be expressed as [20]:

$$L(\Delta\omega) = 10\log\left[\frac{2kT}{P_{sig}}\left(\frac{\omega_0}{2Q\Delta\omega}\right)^2\right]$$

(2.42)

where k is the Boltzman's constant, T is the absolute temperature,  $P_{sig}$  is the average power dissipated in the resistive part of the tank,  $\omega_0$  is the oscillation frequency, Q is the effective quality factor, and  $\Delta\omega$  is the offset frequency from the carrier. This simple model only includes noise associated with the LC tank loss noise originating in the  $\frac{1}{(\Delta\omega)^2}$  region and the noise floor contributions at a large frequency offset are not included. In the Leeson's formula, several nonlinear effects are added to the final noise expression. Leeson's formula is given by [20]:

$$L(\Delta\omega) = 10\log\left[\frac{2FkT}{P_{sig}}\left(1 + \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2\right)\left(1 + \frac{\omega_{I/f}^3}{|\Delta\omega|}\right)\right]$$

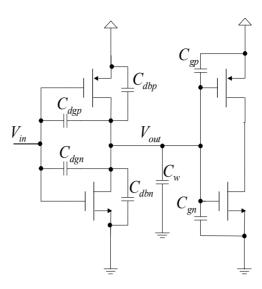

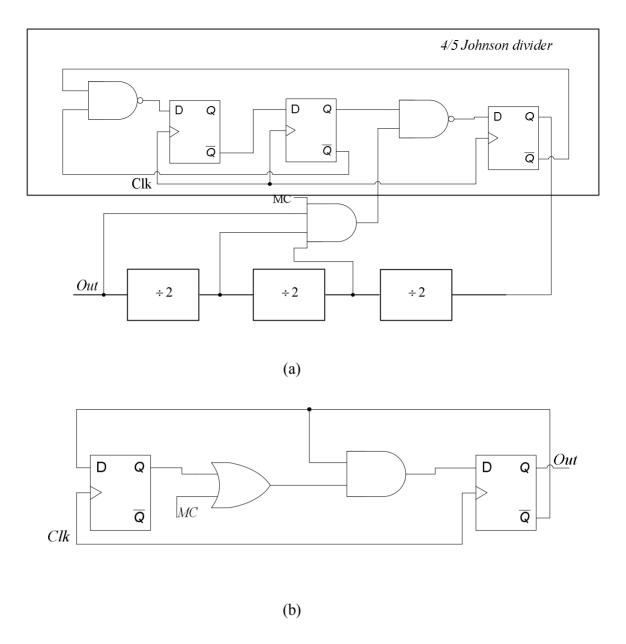

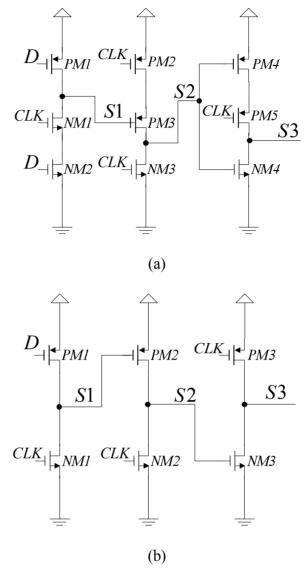

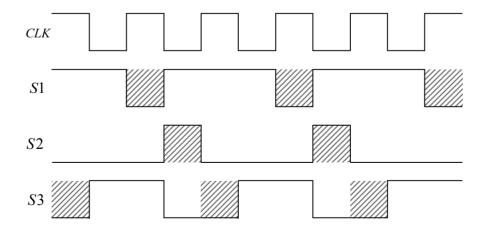

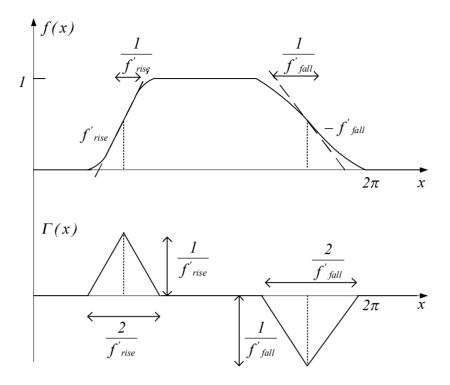

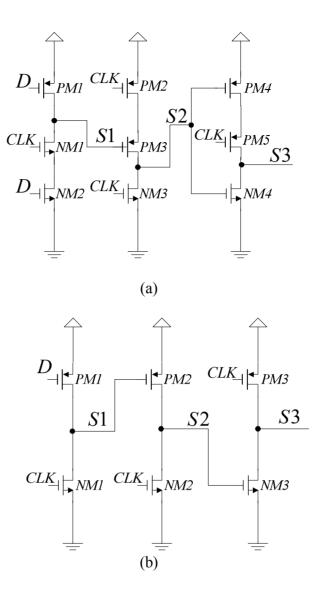

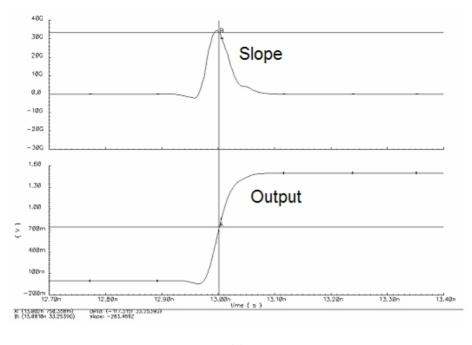

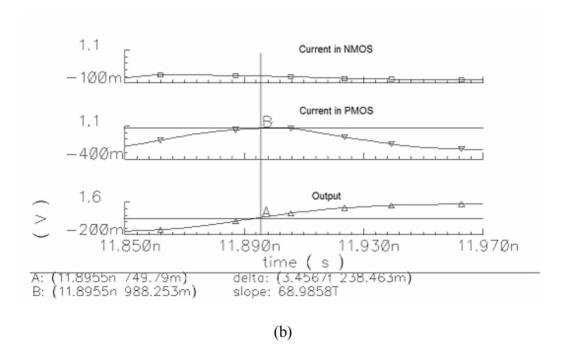

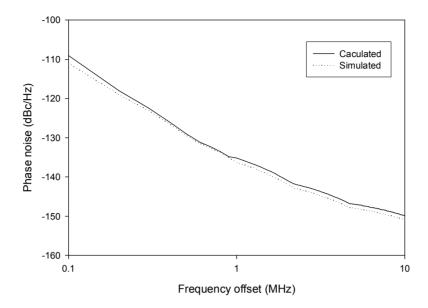

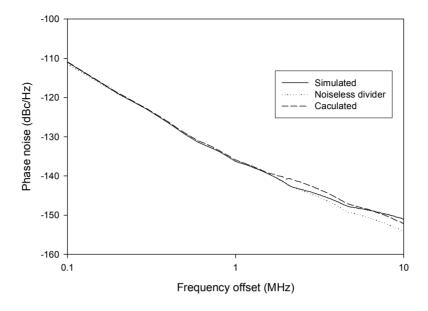

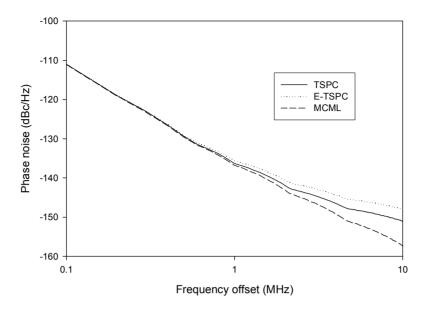

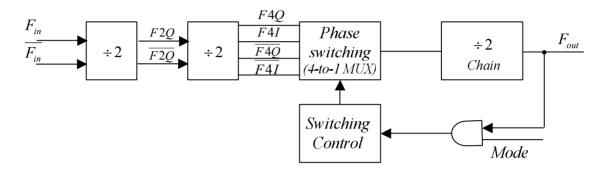

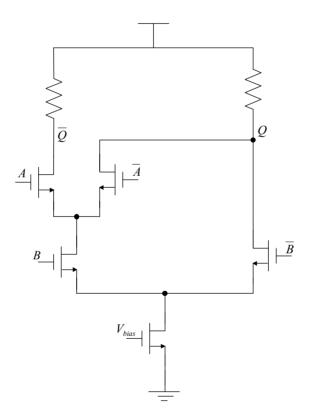

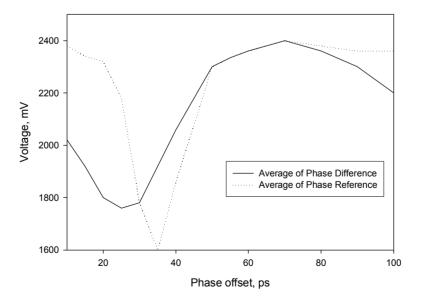

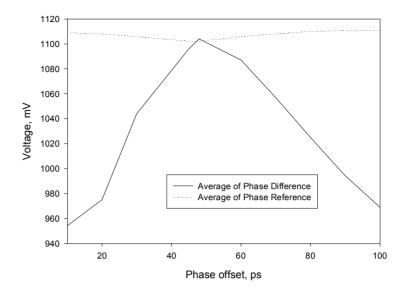

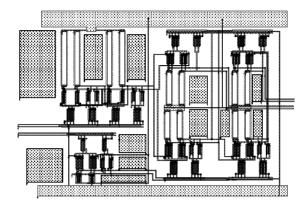

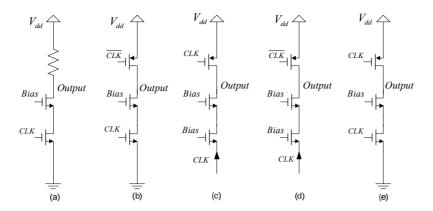

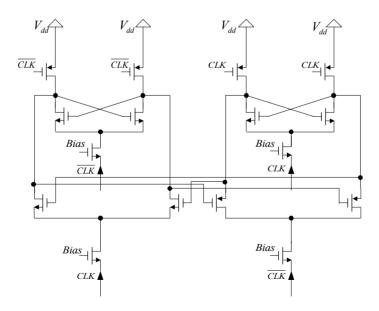

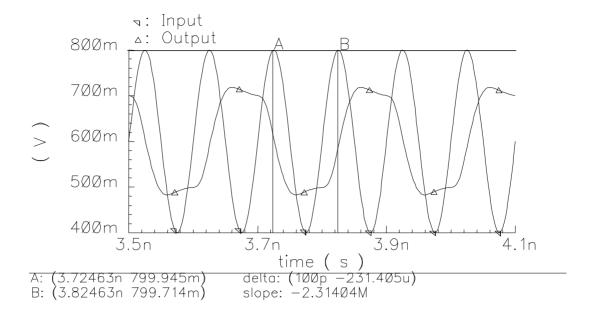

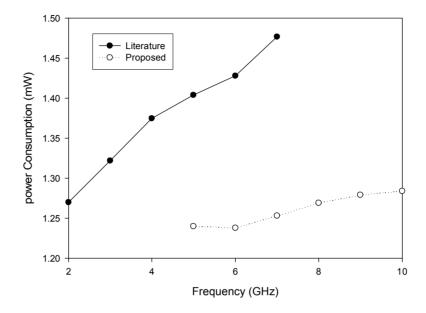

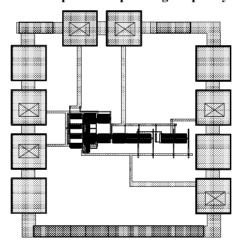

(2.43)