# This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Studies of electrical and optoelectronic properties of Ge-ion-implanted SiO2 thin films

Yang, Ming

2010

Yang, M. (2010). Studies of electrical and optoelectronic properties of Ge-ion-implanted SiO2 thin films. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/40793

https://doi.org/10.32657/10356/40793

Downloaded on 09 Apr 2024 13:26:08 SGT

# STUDIES OF ELECTRICAL AND OPTOELECTRONIC PROPERTIES OF GE-ION-IMPLANTED SIO<sub>2</sub> THIN FILMS

YANG MING

SCHOOL OF ELECTRICAL AND ELECTRONIC

ENGINEERING

2010

# STUDIES OF ELECTRICAL AND OPTOELECTRONIC PROPERTIES OF GE-ION-IMPLANTED SIO<sub>2</sub> THIN FILMS

#### **YANG MING**

School of Electrical and Electronic Engineering

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirement for the degree of Doctor of Philosophy This thesis is dedicated to my parents.

#### Acknowledgements

### **ACKNOWLEDGEMENTS**

My foremost gratitude goes to my supervisor, Dr. Chen Tupei, for his continuous guidance, support and encouragement throughout my Ph.D study. He introduced me to the world of scientific research and encouraged me to develop my research skills. He also taught me the disciplines in both study and life. Also I would like to express my sincere thanks to Dr. Sam Zhang Shanyong from School of Mechanical and Aerospace Engineering, NTU for his guidance and useful suggestions on my research project. Thanks also go to my seniors, Dr. Liu Yang, Dr. Ng Chi Yung and Dr. Ding Liang, as well as my team members, Mr. Wong Jen It, Mr. Yang Jianbo, Mr. Cen Zhanhong, Mr. Liu Zhen, Ms. Goh Shing Mei Eunice, Ms. Zhu Wei, Mr. Zhu Shu and Mr. Zhang Wali. I greatly enjoyed the time working with them and sincerely appreciate their contribution to my project. Furthermore, I would like to thank Dr. Zhu Furong from Institute of Materials Research & Engineering and Ms. Liu Yuchan from Singapore Institute of Manufacturing Technology for their support in the fabrication and characterization of my samples. The great support from Nanophotonics Lab and Nanyang NanoFabrication Center (N<sup>2</sup>FC) is also appreciated. Last but not least, my parents deserve my deepest appreciation for their care, love, encouragement and understanding through all the years. The completion of this thesis is not possible without their continuous support.

#### Summary

### **SUMMARY**

It is the intent of this work to present a systematic investigation on the electrical and optoelectronic properties of SiO<sub>2</sub> thin films embedded with Ge nanocrystals (nc-Ge) for the potential applications in non-volatile memories as well as light emitting devices. The Ge nanocrystals embedded in SiO<sub>2</sub> have been synthesized with low-energy (2 – 16 keV) Ge ion implantation technique which is fully compatible with modern complementary-metal-oxide-semiconductor (CMOS) technology and has the advantage of being able to precisely control the nc-Ge concentration and depth distribution by adjusting the implant energy and Ge ion dose. The synthesized SiO<sub>2</sub> thin films embedded with nc-Ge have been characterized by the techniques of transmission electron microscopy (TEM), secondary ion mass spectroscopy (SIMS), x-ray photoelectron spectroscopy (XPS), current-voltage (*I-V*), capacitance-voltage (*C-V*) and electroluminescence (EL).

The current conduction behavior of the Ge-ion-implanted SiO<sub>2</sub> thin films embedded with nc-Ge has been studied. The characteristics of gate current density versus oxide field at various temperatures have been investigated, and the different transport mechanisms dominating in different oxide field regions have been identified. Appropriate models used to explain the current transport behavior have been proposed. On the other hand, the conduction of the Ge-ion-implanted SiO<sub>2</sub> can be switched to a higher- or lower-conductance state with ultra-violet (UV) illumination. Such photon-induced conduction modulation phenomenon is caused by the charging and discharging of nc-Ge due to the UV illumination.

#### Summary

The charge trapping and retention behavior of the Ge-ion-implanted SiO<sub>2</sub> thin films embedded with nc-Ge has been studied. The dependence of trapped charges on the polarity and magnitude of the charging voltage as well as the charging time has been studied. Besides, the influences of thermal annealing temperature, implant energy and implant dose on the charge trapping and charge retention behavior have been investigated, and the results are well correlated to the changes in the structural properties of the Ge-ion-implanted SiO<sub>2</sub> thin films. In addition, the charge loss caused by the lateral charge transfer along the nc-Ge distributed region and the charge leakage to the Si substrate has also been studied.

The metal-oxide-semiconductor (MOS) capacitance of the Ge-ion-implanted SiO<sub>2</sub> thin films embedded with nc-Ge has been modeled using an approach based on the calculation of effective dielectric constant using the sub-layer method and the Maxwell-Garnett effective medium approximation (EMA) for each sub-layer. Both the distribution of nc-Ge in SiO<sub>2</sub> and the reduced dielectric constant corresponding to the nanometer size of nc-Ge have been taken in account during the calculation. Using this approach, the influences of implant energy and dose on the MOS capacitance have been studied, and the static dielectric constant of nc-Ge embedded in SiO<sub>2</sub> has been determined. The calculated results have been compared with the experimental data showing that good agreement exists over a wide range of nc-Ge distribution.

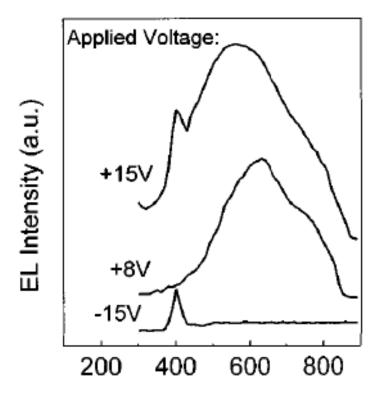

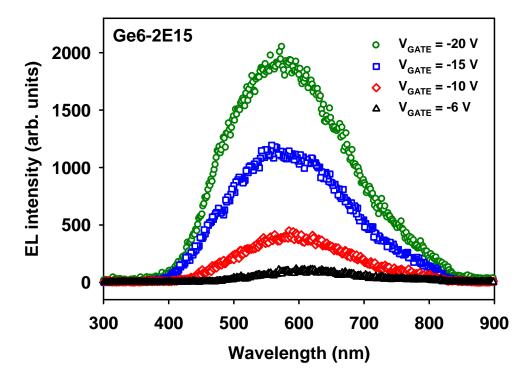

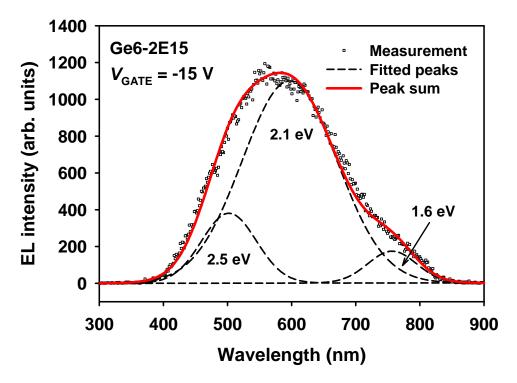

Light-emitting devices based on a structure of indium tin oxide (ITO) /  $SiO_2$  embedded with nc-Ge / p-Si substrate have been fabricated. Visible electroluminescence (EL) with a dominant EL band at 2.1 eV and two shoulder bands

#### Summary

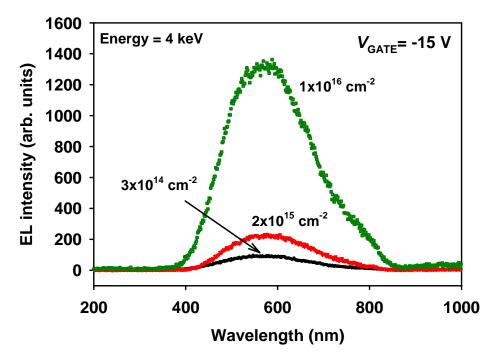

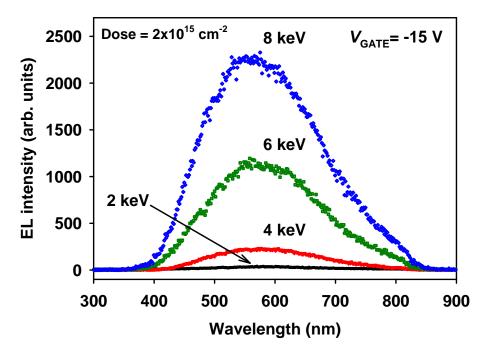

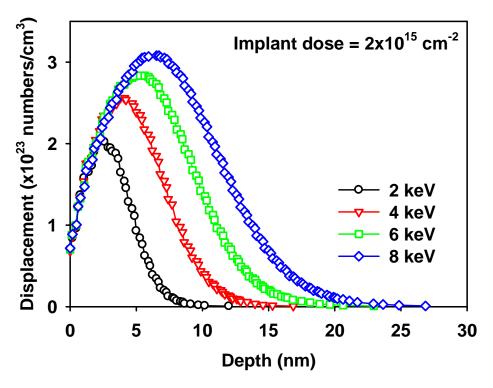

at 1.6 and 2.5 eV has been obtained from the light-emitting structures based on the Ge-ion-implanted SiO<sub>2</sub>. The EL mechanisms have been discussed. In addition, the effects of implant energy and dose on the EL behavior have been investigated. The enhanced EL intensity with the implant energy has been explained by the enhanced current conduction caused by the alteration of the nc-Ge distribution in the SiO<sub>2</sub> as well as the increase of implant-generated luminescence centers in the SiO<sub>2</sub>.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                | II      |

|-----------------------------------------------------------------|---------|

| SUMMARY                                                         | III     |

| TABLE OF CONTENTS                                               | VI      |

| LIST OF FIGURES                                                 | XII     |

| LIST OF TABLES                                                  | XX      |

| NOMENCLATURES                                                   | XXI     |

| CHAPTER 1 INTRODUCTION                                          | 1       |

| 1.1 Brief introduction to non-volatile memory devices           | 1       |

| 1.2 Brief introduction to Si-compatible optoelectronic devices  | 2       |

| 1.3 Nanocrystals                                                | 4       |

| 1.3.1 Roles of nanocrystals for next-generation non-volatile me | mories4 |

| 1.3.2 Roles of nanocrystals for Si-compatible optoelectronic de | vices6  |

| 1.3.3 Ge nanocrystals                                           | 7       |

| 1.4 Motivation                                                  | 7       |

| 1.5 Objective and scope of research                             | 11      |

| 1.6 Major contributions of the thesis                           | 12      |

| 1.7 Organization of the thesis                                  | 14      |

| CHAPTER 2 LITERATURE REVIEW                                     | 17      |

| 2.1 Introduction                                                | 17      |

| 2.2 Synthesis techniques for nc-Ge embedded in SiO <sub>2</sub> | 18      |

| 2.2.1 Ion implantation technique                                | 19      |

| 2.2.2 Other synthesis techniques                                | 21      |

| 2.2.3 Comparison of various nc-Ge synthesis techniques          | 25      |

| 2.3 Common characterization techniques                          | 27      |

| 2.3.1 Structural and material characterizations                               | 28             |

|-------------------------------------------------------------------------------|----------------|

| 2.3.2 Electrical characterizations.                                           | 35             |

| 2.3.3 Optoelectronic characterizations                                        | 37             |

| 2.4 Memory devices based on nanocrystals embedded in SiO <sub>2</sub>         | 38             |

| 2.4.1 Conventional floating-gate memory structure                             | 38             |

| 2.4.2 Nanocrystal-based non-volatile memory devices                           | 40             |

| 2.5 Light-emitting devices based on nanocrystals embedded in SiO <sub>2</sub> | 44             |

| 2.5.1 Overview of direct and indirect bandgap materials                       | 44             |

| 2.5.2 Photoluminescence from SiO <sub>2</sub> embedded with nanocrystals      | 45             |

| 2.5.3 Electroluminescence from SiO <sub>2</sub> embedded with nanocrystals    | 49             |

| 2.6 Summary                                                                   | 54             |

| CHAPTER 3 CURRENT TRANSPORT IN GE-IC IMPLANTED SIO <sub>2</sub> THIN FILMS    |                |

| 3.1 Introduction                                                              | 56             |

| 3.2 An overview of common conduction mechanisms                               | 57             |

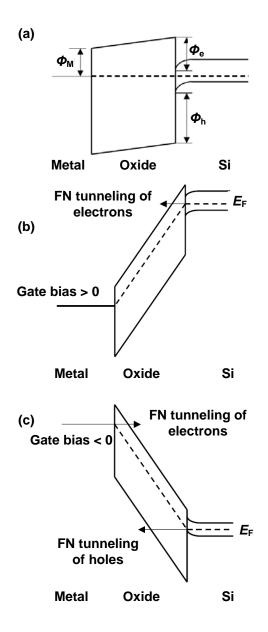

| 3.2.1 Fowler-Nordheim tunneling                                               | 58             |

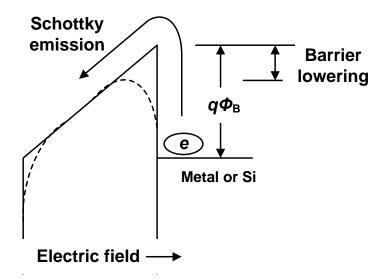

| 3.2.2 Schottky emission.                                                      | 61             |

| 3.2.3 Poole-Frenkel emission                                                  | 63             |

| 3.2.4 Ohmic conduction                                                        | 65             |

| 3.3 Sample fabrication and experimental details                               | 66             |

| 3.3.1 Fabrication of Ge-ion-implanted SiO <sub>2</sub> thin films             | 66             |

|                                                                               |                |

| 3.3.2 SIMS and TEM characterizations                                          |                |

| 3.3.2 SIMS and TEM characterizations                                          | 67             |

|                                                                               | 67<br>68       |

| 3.3.3 Fabrication of MOS structures                                           | 67<br>68<br>69 |

| 3.3.3 Fabrication of MOS structures                                           | 67<br>68<br>69 |

| 3.5 Current transport in SiO <sub>2</sub> with nc-Ge distributed in a narrow la<br>the SiO <sub>2</sub> surface |                        |

|-----------------------------------------------------------------------------------------------------------------|------------------------|

| 3.5.1 Characteristics of gate current density versus electric field                                             | 78                     |

| 3.5.2 Conduction mechanism in the high-field region                                                             | 84                     |

| 3.5.3 Conduction mechanism in the medium-field region                                                           | 87                     |

| 3.5.4 Conduction mechanism in the low-field region                                                              | 90                     |

| 3.5.5 Discussions                                                                                               | 91                     |

| 3.5.6 Conclusion                                                                                                | 103                    |

| 3.6 Current transport in SiO <sub>2</sub> with nc-Ge distributed throughout the                                 | e SiO <sub>2</sub> 104 |

| 3.6.1 Characteristics of gate current density versus electric field                                             | 104                    |

| 3.6.2 Conduction mechanism in the high-field region                                                             | 106                    |

| 3.6.3 Conduction mechanism in the low-field region                                                              | 108                    |

| 3.6.4 Discussions                                                                                               | 110                    |

| 3.6.5 Conclusion                                                                                                | 113                    |

| 3.7 Conduction modulation of SiO <sub>2</sub> embedded with nc-Ge caused by                                     |                        |

| illumination                                                                                                    |                        |

| 3.7.1 Overview                                                                                                  |                        |

| 3.7.2 Results and discussions                                                                                   |                        |

| 3.7.3 Conclusion                                                                                                |                        |

| 3.8 Summary                                                                                                     | 121                    |

| HAPTER 4 CHARGE TRAPPING AND CI<br>ETENTION IN GE-ION-IMPLANTED SIO <sub>2</sub> THIN FILMS                     |                        |

| 4.1 Introduction                                                                                                |                        |

| 4.2 Sample fabrication and experimental details                                                                 | 125                    |

| 4.2.1 Sample fabrication                                                                                        |                        |

| 4.2.2 Characterization techniques                                                                               |                        |

| 4.3 Charge trapping and retention in SiO <sub>2</sub> thin film with nc-Ge distri                               |                        |

| near the SiO <sub>2</sub> surface                                                                               |                        |

| 4.3.1 Device structure                                                                                          | 126                    |

|                                                                                                                 |                        |

| 5.2 Modeling of MOS capacitance                                                                         | 184 |

|---------------------------------------------------------------------------------------------------------|-----|

| 5.1 Introduction                                                                                        | 183 |

| CHAPTER 5 CAPACITANCE OF GE-ION-IMPLANTED THIN FILMS                                                    | _   |

| 4.7 Summary                                                                                             | 181 |

| 4.6.4 Conclusion                                                                                        | 180 |

| 4.6.3 Charge retention behavior                                                                         | 174 |

| 4.6.2 Charge trapping behavior                                                                          | 172 |

| 4.6.1 Experimental details                                                                              | 166 |

| 4.6 Role of lateral charge transfer in the charge retention                                             | 165 |

| 4.5.3 Conclusion                                                                                        | 164 |

| 4.5.2 Charge retention behavior                                                                         | 161 |

| 4.5.1 Charge trapping behavior                                                                          | 158 |

| 4.5 Influences of implant energy and dose on charge trapping and charetention behavior                  | _   |

| 4.4.5 Conclusion                                                                                        |     |

| 4.4.4 Charge retention behavior                                                                         |     |

| 4.4.3 Charge trapping behavior                                                                          |     |

| 4.4.2 Influence of annealing temperature on the local chemical proper Ge-ion-implanted SiO <sub>2</sub> |     |

| 4.4.1 Influence of annealing temperature on structural properties of C implanted SiO <sub>2</sub>       |     |

| 4.4 Influence of annealing temperature on charge trapping and charge retention behavior                 |     |

| 4.3.6 Conclusion                                                                                        | 140 |

| 4.3.5 Charge retention behavior                                                                         | 138 |

| 4.3.4 Influence of charging time                                                                        | 134 |

| 4.3.3 Influence of polarity and magnitude of charging voltage                                           | 130 |

| 4.3.2 Charge trapping behavior                                                                          | 128 |

| 5.3 Experimental measurement of MOS capacitance                                   | 189 |

|-----------------------------------------------------------------------------------|-----|

| 5.4 Results and discussions                                                       | 191 |

| 5.4.1 <i>C-V</i> characteristics of MOS structures with and without nc-Ge         | 191 |

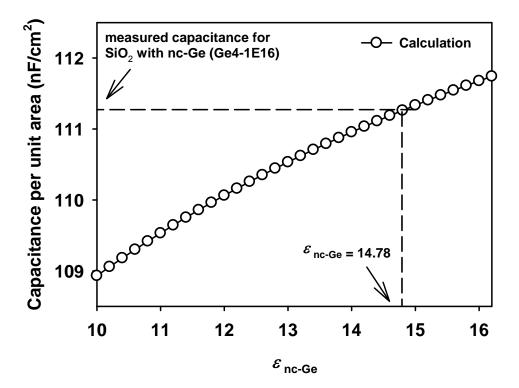

| 5.4.2 Static dielectric constant of nc-Ge                                         | 192 |

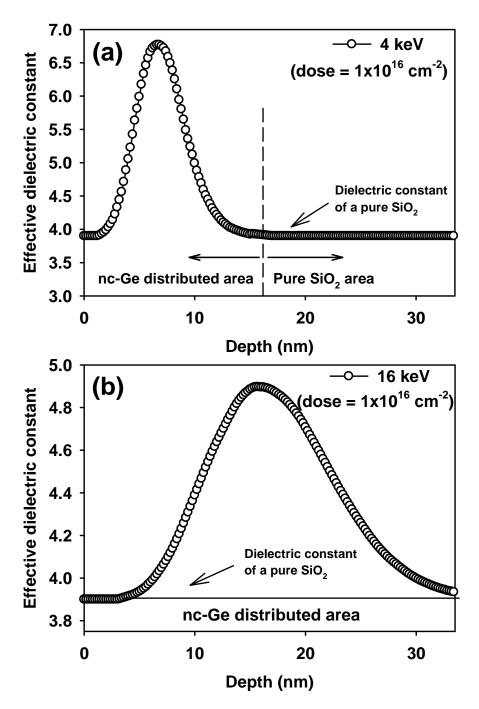

| 5.4.3 Influence of implant energy and dose on MOS capacitance                     | 198 |

| 5.4.4 Comparison between calculated and measured MOS capacitances                 | 201 |

| 5.5 Conclusion                                                                    | 203 |

| CHAPTER 6 ELECTROLUMINESCENCE FROM GE-I<br>IMPLANTED SIO <sub>2</sub> THIN FILMS  |     |

| 6.1 Introduction                                                                  | 205 |

| 6.2 Sample fabrication and experimental details                                   | 206 |

| 6.2.1 Sample fabrication                                                          | 206 |

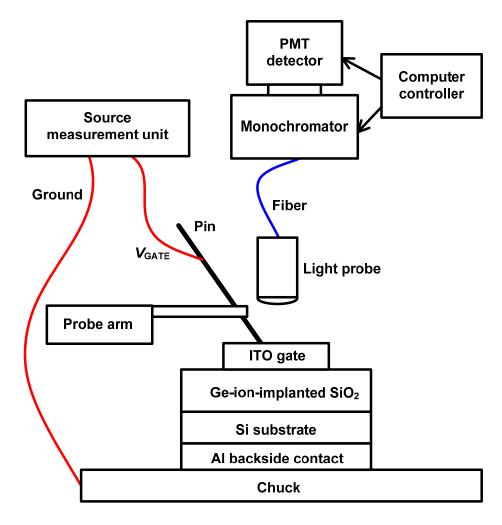

| 6.2.2 Electroluminescence characterization system                                 | 207 |

| 6.3 Visible electroluminescence                                                   | 209 |

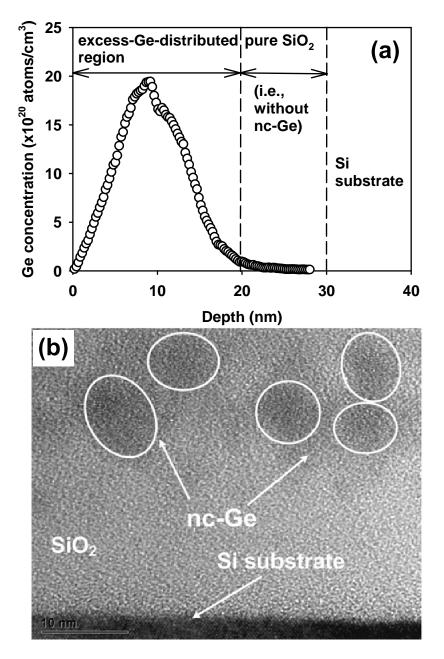

| 6.3.1 Structure of Ge-ion-implanted SiO <sub>2</sub> thin film                    | 209 |

| 6.3.2 EL spectra                                                                  | 211 |

| 6.3.3 Gate voltage dependence of gate current density and integrated El intensity |     |

| 6.3.4 EL mechanisms                                                               | 215 |

| 6.3.5 Conclusion                                                                  | 219 |

| 6.4 Influences of implant dose and energy on EL behavior                          | 219 |

| 6.4.1 Dependence of EL intensity on implant dose and energy                       | 220 |

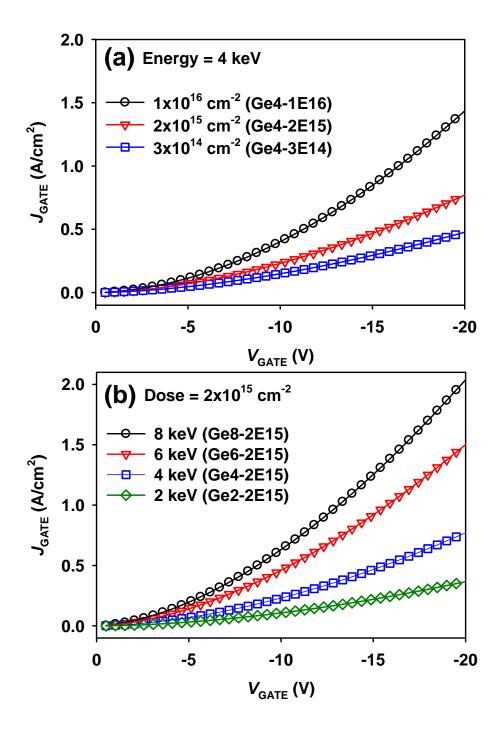

| 6.4.2 Dependence of current conduction on implant dose and energy                 | 222 |

| 6.4.3 Dependence of external quantum efficiency on implant dose and energy        | 226 |

| 6.4.4 Conclusion                                                                  | 233 |

| 6.5 Summary                                                                       | 233 |

| CHAPTER 7 CONCLUSION AND RECOMMENDATIONS                                          | 235 |

| 7.1 Conclusion23                                                                                               | 35             |

|----------------------------------------------------------------------------------------------------------------|----------------|

| 7.1.1 Current transport behavior                                                                               | 36             |

| 7.1.2 Charge trapping and charge retention behavior                                                            | 36             |

| 7.1.3 Calculation of MOS capacitance 23                                                                        | 37             |

| 7.1.4 EL behavior                                                                                              | 38             |

| 7.2 Recommendations23                                                                                          | 39             |

| 7.2.1 Synthesis of nc-Ge embedded in SiO <sub>2</sub> using other techniques23                                 | 39             |

| 7.2.2 Investigation of methods to improve the performance of devices base on Ge-ion-implanted SiO <sub>2</sub> |                |

| 7.2.3 Investigation of single-electron charging in nc-Ge                                                       | 40             |

| 7.2.4 Simulation of non-volatile memory cell based on nc-Ge24                                                  | 41             |

| 7.2.5 Development of an empirical formula for the dielectric constant of nano-composite systems 22             | 42             |

| 7.2.6 Development of Si-compatible integrated optoelectronic devices24                                         | 42             |

| 7.2.7 First-principle calculation of electronic properties of nc-Ge24                                          | 43             |

| LIST OF PUBLICATIONS24                                                                                         | 14             |

| BIBLIOGRAPHY24                                                                                                 | <del>1</del> 7 |

# LIST OF FIGURES

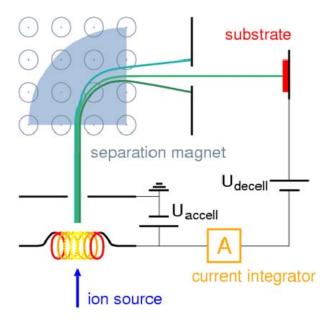

| Fig. 2-1 Illustration of the basic principle of the ion implantation process20                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

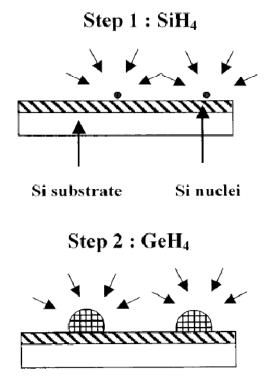

| Fig. 2-2 Schematics of the two-step technique to grow nc-Ge on SiO <sub>2</sub> surface (from Ref. [36])                                                                                                                                                     |

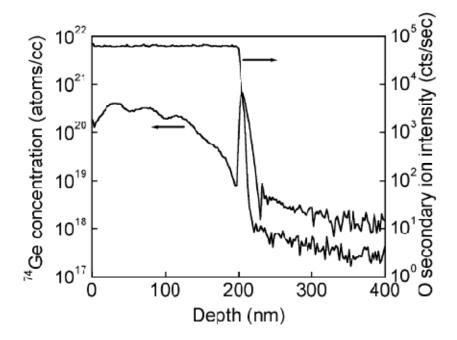

| Fig. 2-3 A typical SIMS depth profile of Ge in SiO <sub>2</sub> [108].                                                                                                                                                                                       |

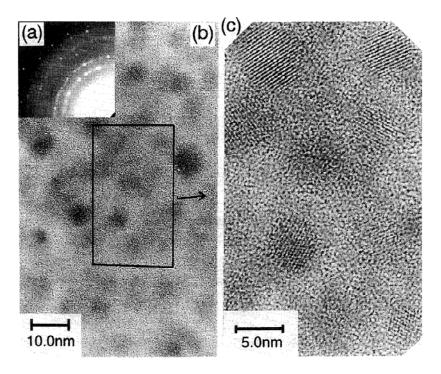

| Fig. 2-4 Electron diffraction pattern (a), and cross-sectional HRTEM image for a typical SiO <sub>2</sub> embedded with nc-Ge synthesized by the co-sputtering technique (from Ref. [65])                                                                    |

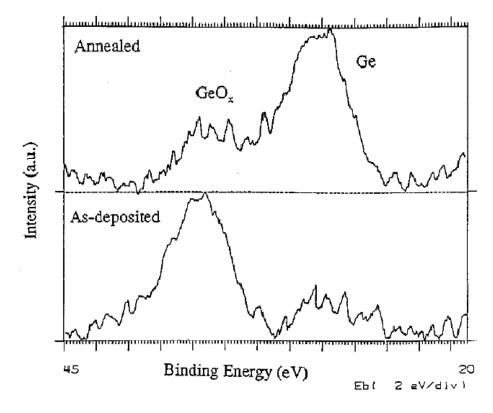

| Fig. 2-5 Typical XPS spectra for the as-deposited and annealed nc-Ge in SiO <sub>2</sub> (from Ref. [33])32                                                                                                                                                  |

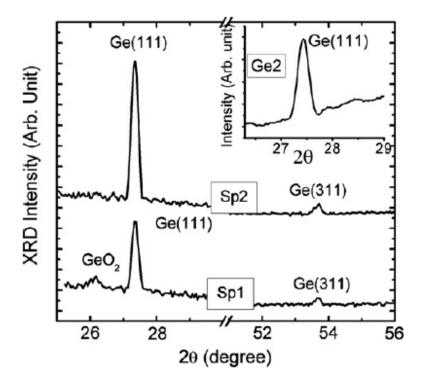

| Fig. 2-6 Typical XRD patterns showing the formation of (111) and (311) orientated nc-<br>Ge embedded in SiO <sub>2</sub> (from Ref. [90])34                                                                                                                  |

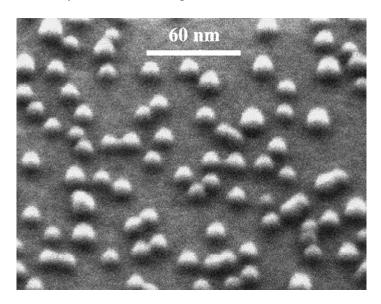

| Fig. 2-7 A typical SEM image of nc-Ge deposited on the SiO <sub>2</sub> surface (from Ref. [63])                                                                                                                                                             |

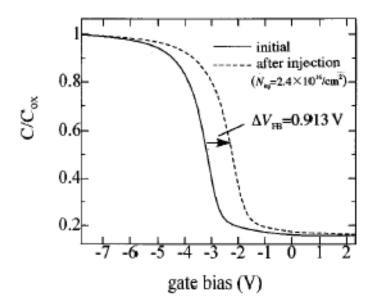

| Fig. 2-8 $C$ - $V$ characteristics showing the $\Delta V_{\rm FB}$ after the charge injection (from Ref. [47])                                                                                                                                               |

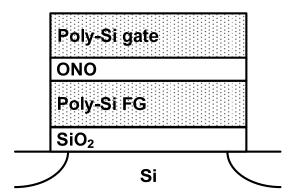

| Fig. 2-9. Schematic representation of a conventional FG non-volatile memory cell (from Ref. [19]). The ONO is oxide-nitride-oxide gate dielectric stack used as the control oxide.                                                                           |

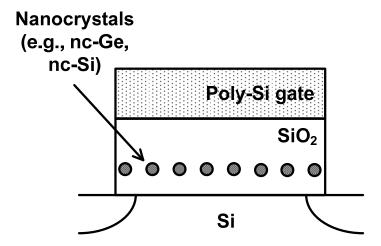

| Fig. 2-10 Schematic representation of a nanocrystal-based non-volatile memory cell (from Ref. [19])                                                                                                                                                          |

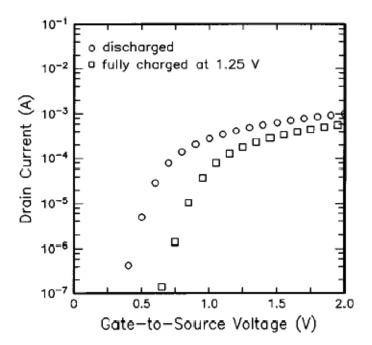

| Fig. 2-11 Typical transfer characteristics of the nanocrystal-based non-volatile memory under the program operation. The shift in threshold voltage due to the electron storage in nanocrystals is ~ 0.25 V (from Ref. [20])41                               |

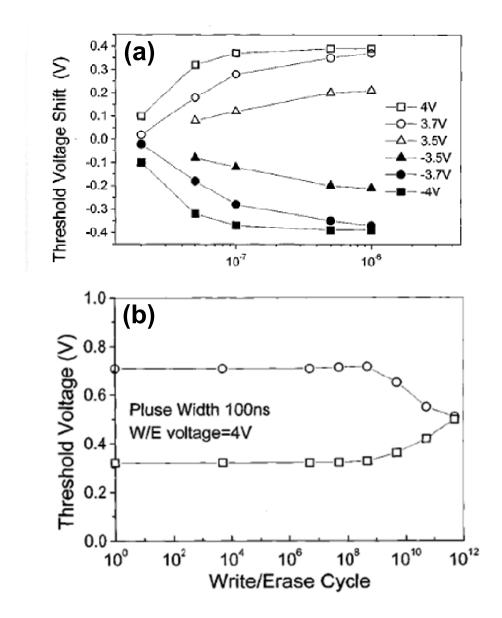

| Fig. 2-12 Typical memory performance of the non-volatile memory cell based on ne-Ge: (a) threshold voltage shifts under various the program / erase (P/E) time and voltage, and (b) endurance of the cell tested with +4 V/ -4 V P/E pulse (from Ref. [78]). |

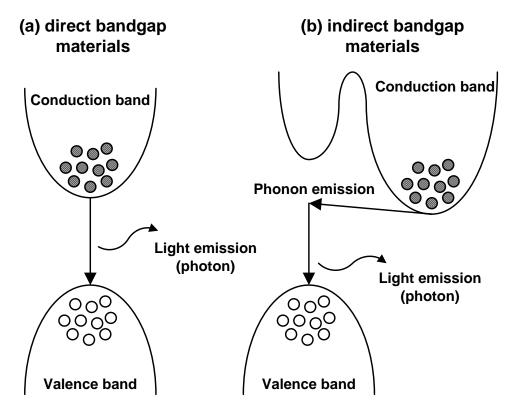

| Fig. 2-13 Schematic of band-to-band radiative transitions in (a) direct bandgap materials, and (b) indirect bandgap materials                                                                                                                                |

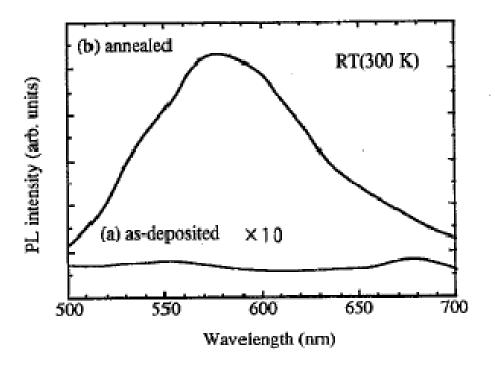

| Fig. 2-14 Typical PL spectra at the visible wavelength region (from Ref. [66])48                                                                                                                                                                             |

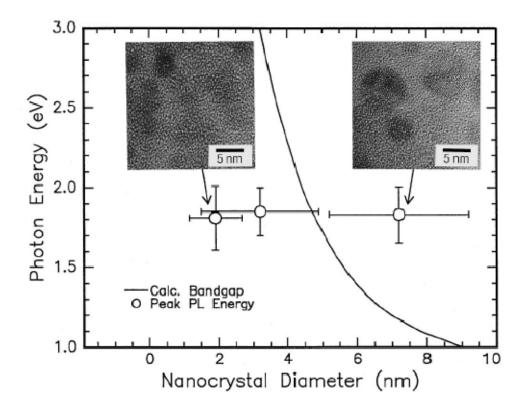

| Fig. 2-15 Comparison between PL peak energy with the calculated bandgap energy as a function of nanocrystal diameter for nc-Ge embedded in SiO <sub>2</sub> (from Ref. [177]). TEM images are also shown to confirm the nanocrystal diameter49               |

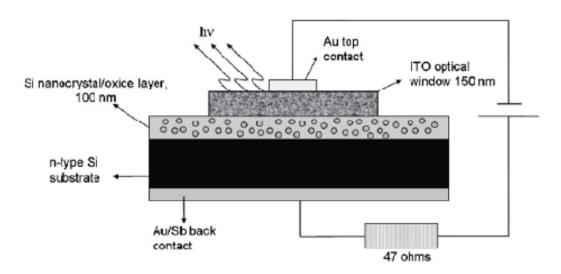

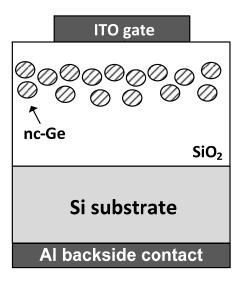

| Fig. 2-16 Typical schematic diagram of a MOSLED for the characterization of EL from the SiO <sub>2</sub> thin film embedded with nanocrystals (from Ref. [161])50                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2-17 Different EL spectra obtained from the Au / SiO2 / <i>p</i> -Si structure with nc-Ge embedded in SiO <sub>2</sub> under different bias conditions (from Ref. [52])                                                                                                                                     |

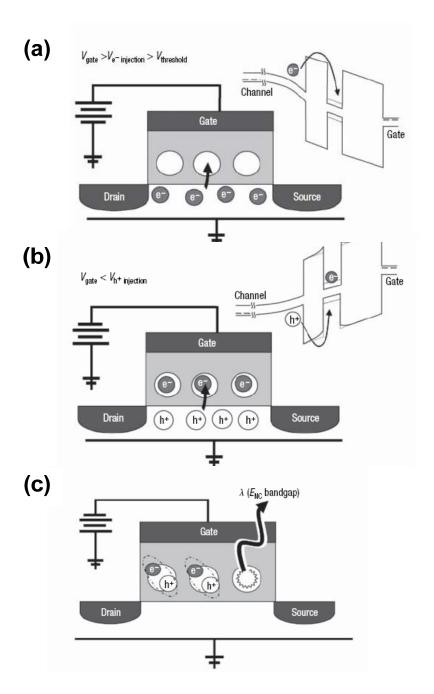

| Fig. 2-18. Schematic diagrams showing the carrier injection in a FELED (from Ref. [180]): (a) electrons are injected into nanocrystals under a positive pulse, (b) holes are injected into nanocrystals under a negative pulse, (c) recombination of electrons and holes in nanocrystals leads to light emission |

| Fig. 3-1 Energy-band diagram of a MOS structure (a) at zero bias, (b) with a large positive gate bias, and (c) with a large negative gate (after Ref. [183])59                                                                                                                                                   |

| Fig. 3-2 Energy band diagram showing the Schottky emission of electrons over the potential barrier in the presence of an electric field (after Ref. [191])                                                                                                                                                       |

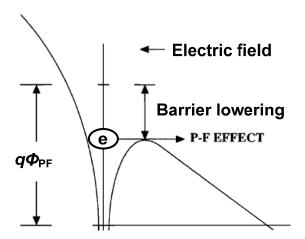

| Fig. 3-3 Energy band diagram showing the PF emission of an electron from a trap in the dielectric layer in the presence of an external electric field (from Ref. [194])                                                                                                                                          |

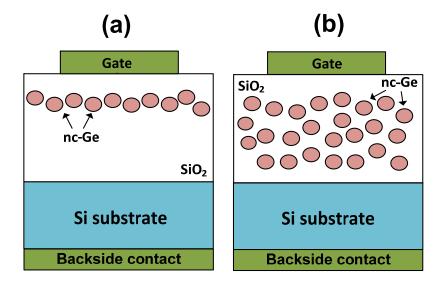

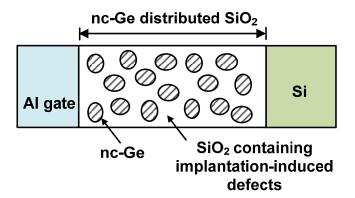

| Fig. 3-4 Schematic diagrams showing the MOS structure with (a) nc-Ge confined in one narrow layer near the surface of SiO <sub>2</sub> , and (b) nc-Ge distributed throughout the SiO <sub>2</sub> .                                                                                                             |

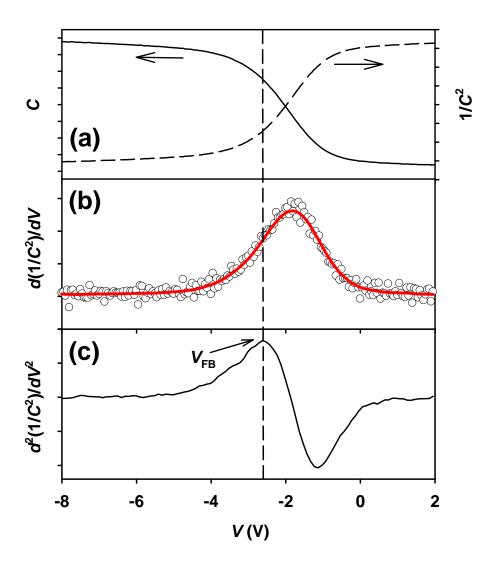

| Fig. 3-5 A differentiation technique to determine the $V_{\rm FB}$ from a $C\text{-}V$ curve. In (a), (b) and (c), plots of $C$ , $1/C^2$ , $d(1/C^2)/dV$ and $d^2(1/C^2)/dV^2$ are shown against $V$ . The $V_{\rm FB}$ is determined from this technique as a single sharp peak in (c)70                       |

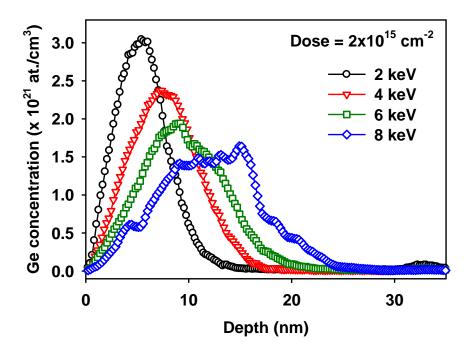

| Fig. 3-6 SIMS depth profiles of Ge ions in SiO <sub>2</sub> thin films for various implant energies after thermal annealing71                                                                                                                                                                                    |

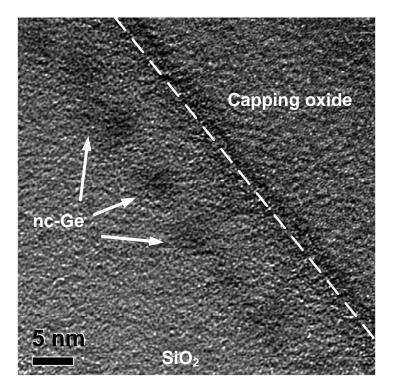

| Fig. 3-7 A cross-sectional TEM image for the annealed Ge4-2E15 sample showing a narrow layer of nc-Ge located close to the SiO <sub>2</sub> surface                                                                                                                                                              |

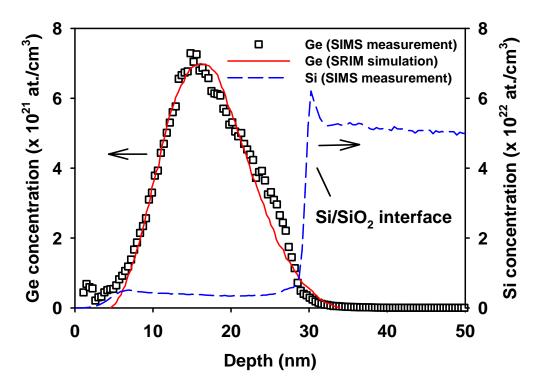

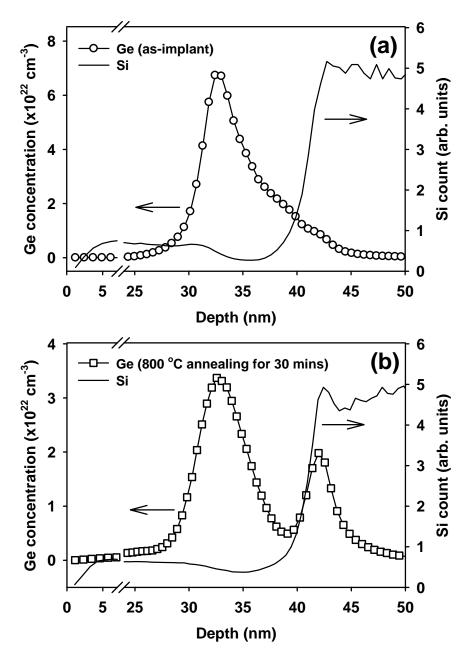

| Fig. 3-8 SIMS and SRIM depth profiles of Ge in SiO <sub>2</sub> thin film for the as-implanted Ge16-1E16 sample. The SIMS profile for Si is also shown to identify the Si / SiO <sub>2</sub> interface                                                                                                           |

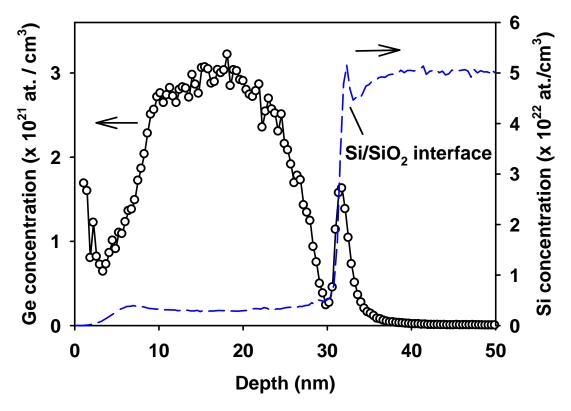

| Fig. 3-9 SIMS depth profile of Ge in SiO <sub>2</sub> for the Ge16-1E16 sample annealed at 800 °C for 1 hour                                                                                                                                                                                                     |

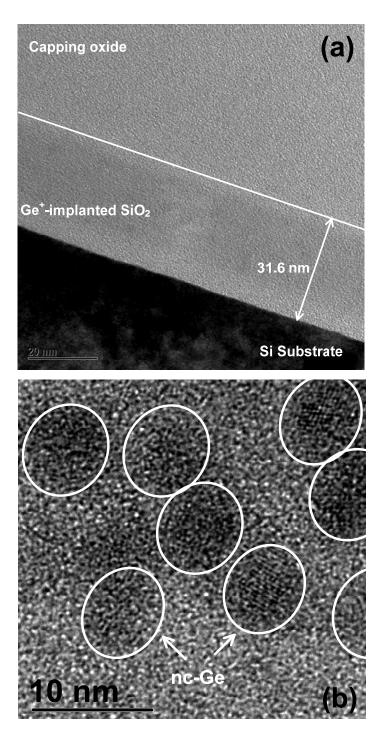

| Fig. 3-10 (a) A cross-sectional TEM image of the annealed Ge16-1E16 sample; (b) A high-resolution TEM image for the same sample showing the existence of nc-Ge distributed throughout the SiO <sub>2</sub>                                                                                                       |

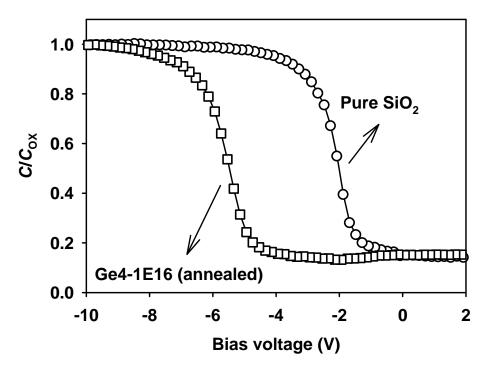

| Fig. 3-11 <i>C-V</i> characteristics for the pure SiO <sub>2</sub> and the annealed Ge4-1E16 sample79                                                                                                                                                                                                            |

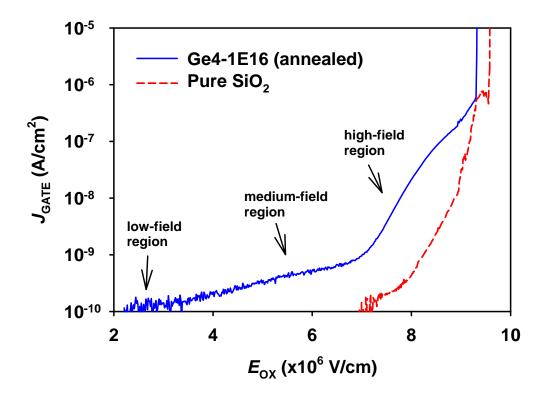

| Fig. 3-12 Room-temperature $J_{\text{GATE}}$ - $E_{\text{OX}}$ characteristics for the pure SiO <sub>2</sub> and the annealed Ge4-1E16 sample.                                                                                                                                                                   |

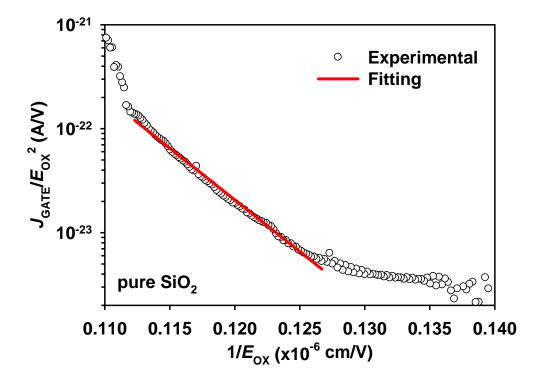

| Fig. 3-13 FN plot (i.e., semi-log plot of $J_{GATE}/E_{OX}^2$ versus $1/E_{OX}$ ) of the pure SiO <sub>2</sub> sample.                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

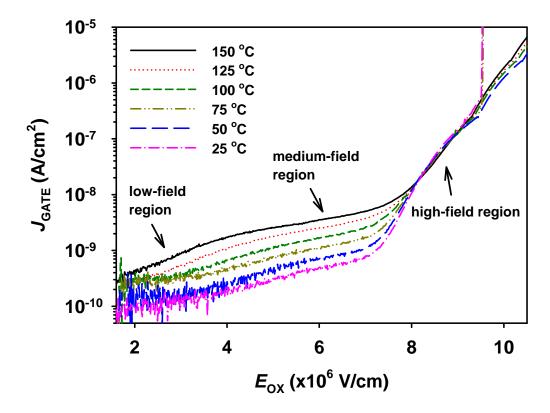

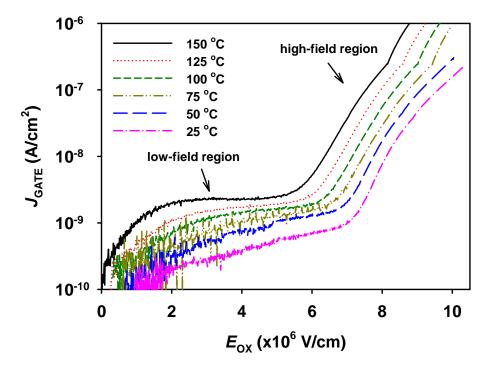

| Fig. 3-14 $J_{\text{GATE}}$ - $E_{\text{OX}}$ characteristics for the annealed Ge4-1E16 sample under various measurement temperature from 25 °C (room-temperature) to 150 °C84                                                                                                                                                                                                      |

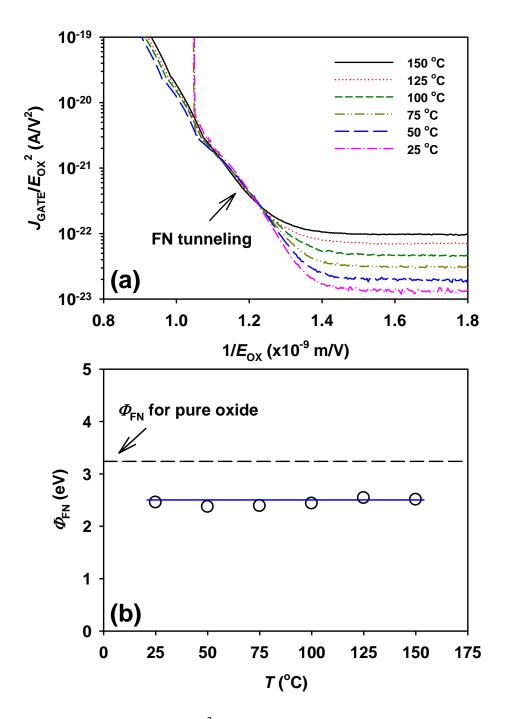

| Fig. 3-15 (a) FN plots of $J_{\text{GATE}}/E_{\text{OX}}^2$ versus $1/E_{\text{OX}}$ for the annealed Ge4-1E16 sample measured at various temperatures. The linear relationship in high-field region of the semi-log plots indicates the occurrence of FN tunneling. (b) The calculated effective barrier height $(\Phi_{\text{FN}})$ as a function of the measurement temperature. |

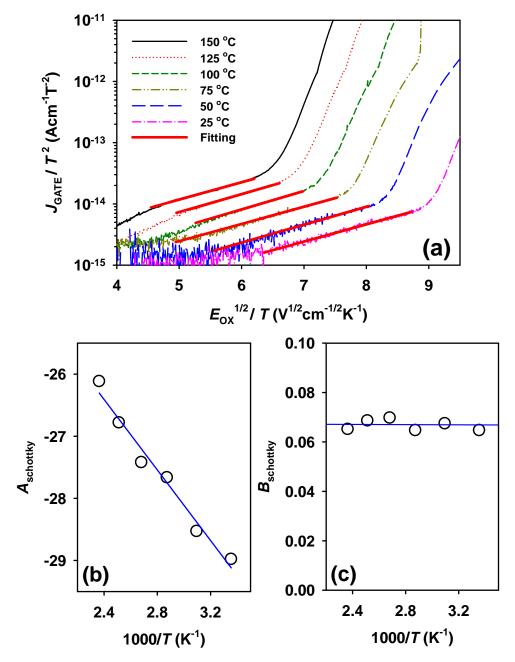

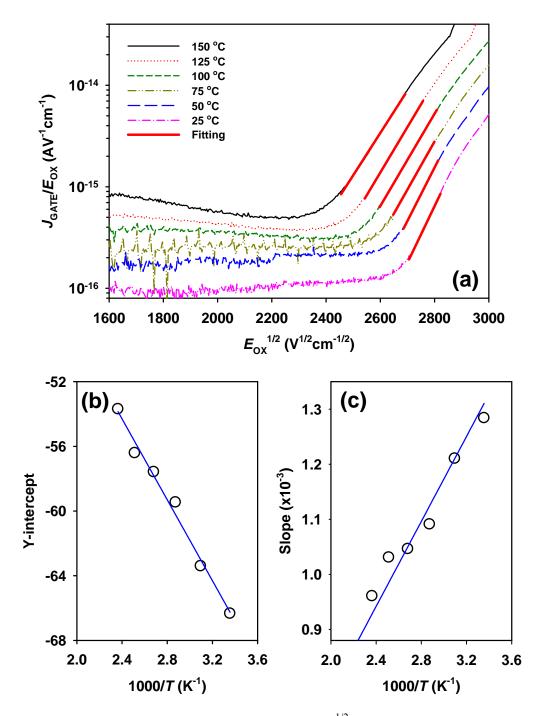

| Fig. 3-16 (a) Semi-log plots of $J_{\rm GATE}/T^2$ versus $E_{\rm OX}^{-1/2}/T$ for the annealed Ge4-1E16 sample. The fitting yields a straight line in the medium-field region for each temperature. In (b) and (c), the fitting parameters, $A_{\rm schottky}$ (i.e., y-intercept) and $B_{\rm schottky}$ (i.e., slope), as a function of $1000/T$ are shown                      |

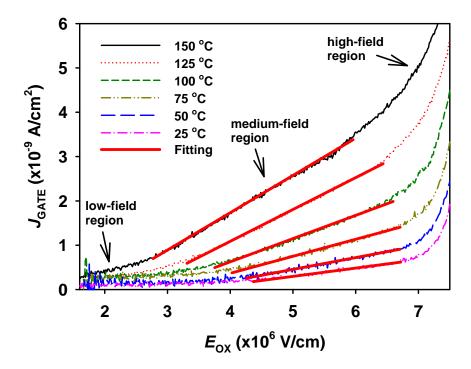

| Fig. 3-17 $J_{\text{GATE}}$ - $E_{\text{OX}}$ plots for the Ge4-1E16 sample. The fitting of the medium-field region indicates the linear relationship between $J_{\text{GATE}}$ and $E_{\text{OX}}$ for each temperature.                                                                                                                                                           |

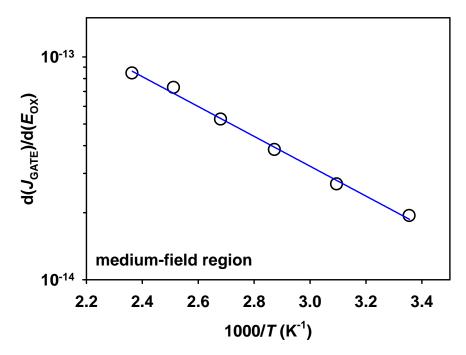

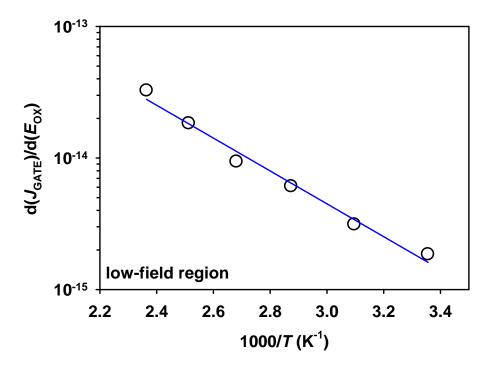

| Fig. 3-18 $d(J_{GATE})/d(E_{OX})$ as a function of $1000/T$ obtained from the fitting of the medium-field region in the $J_{GATE}$ - $E_{OX}$ characteristics90                                                                                                                                                                                                                     |

| Fig. 3-19 $d(J_{\text{GATE}})/d(E_{\text{OX}})$ as a function of 1000/ $T$ obtained from the fitting of the low-field region in the $J_{\text{GATE}}$ - $E_{\text{OX}}$ characteristics                                                                                                                                                                                             |

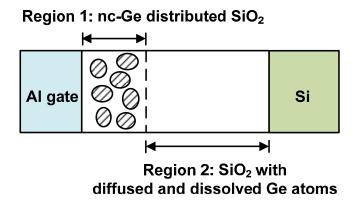

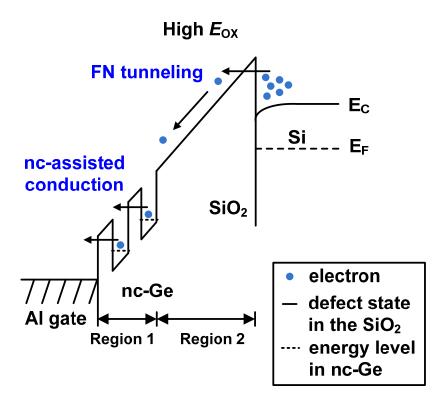

| Fig. 3-20 Schematic diagram of the two-region structure for the Ge-ion-implanted SiO <sub>2</sub> containing nc-Ge near the SiO <sub>2</sub> surface                                                                                                                                                                                                                                |

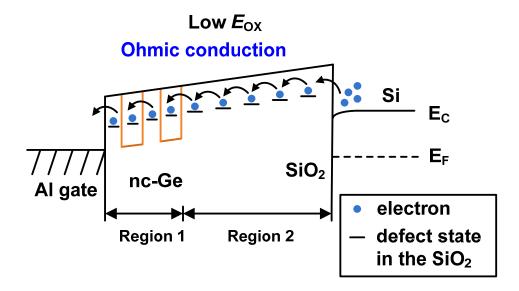

| Fig. 3-21 Energy band diagram of the Ge-ion-implanted $SiO_2$ under a low $E_{OX}$ (i.e., in the low-field region).                                                                                                                                                                                                                                                                 |

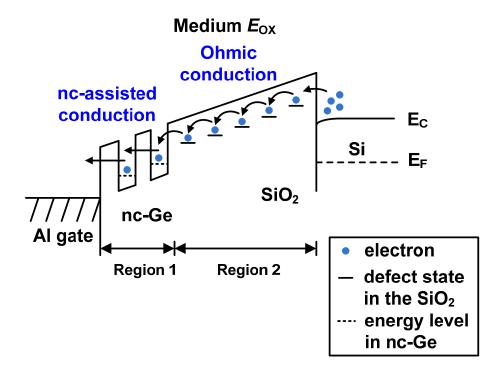

| Fig. 3-22 Energy band diagram of the Ge-ion-implanted $SiO_2$ under a medium $E_{OX}$ (i.e., in the medium-field region)                                                                                                                                                                                                                                                            |

| Fig. 3-23 Energy band diagram of the Ge-ion-implanted $SiO_2$ under a high $E_{OX}$ (i.e., in the high-field region).                                                                                                                                                                                                                                                               |

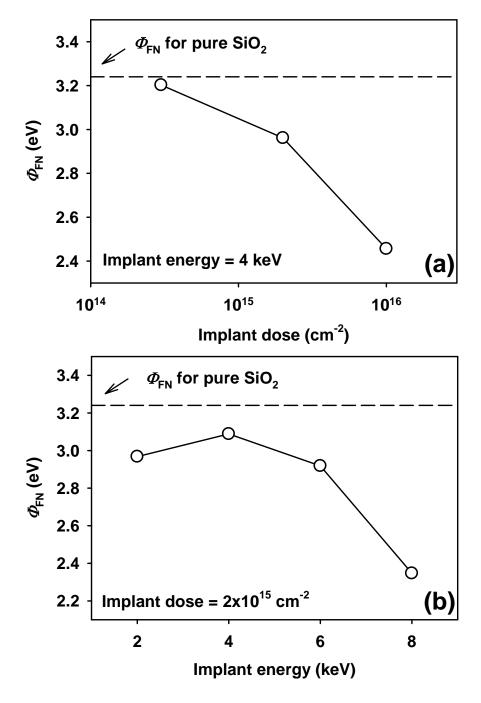

| Fig. 3-24 Effective FN tunneling barrier height ( $\Phi_{FN}$ ) as functions of (a) the implant dose, and (b) the implant energy for the SiO <sub>2</sub> thin films containing near-surface nc-Ge.                                                                                                                                                                                 |

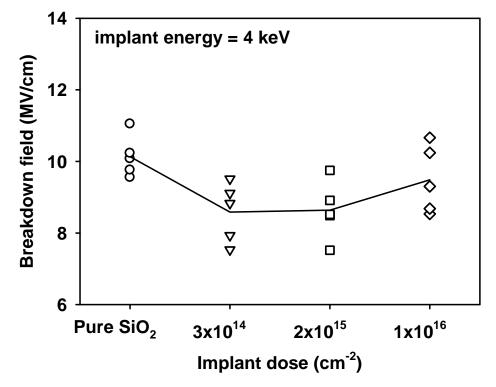

| Fig. 3-25 Breakdown fields for the pure SiO <sub>2</sub> and samples with different implant doses Each sample was measured 5 times on different pads                                                                                                                                                                                                                                |

| Fig. 3-26 $J_{\text{GATE}}$ - $E_{\text{OX}}$ characteristics for the annealed Ge16-1E16 sample under various measurement temperature from 25 °C (room-temperature) to 150 °C105                                                                                                                                                                                                    |

| Fig. 3-27 Semi-log plots of $J_{\rm GATE}/E_{\rm OX}$ versus $E_{\rm OX}^{-1/2}$ for the annealed Ge16-1E16                                                                                                                                                                                                                                                                         |

|      |     | sample measured at various temperatures. The fitting in the high-field region yields a straight line for each temperature. The temperature-dependent y-intercept and slope obtained from the fitting of PF plots are shown in (b) and (c), respectively                                                     |

|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

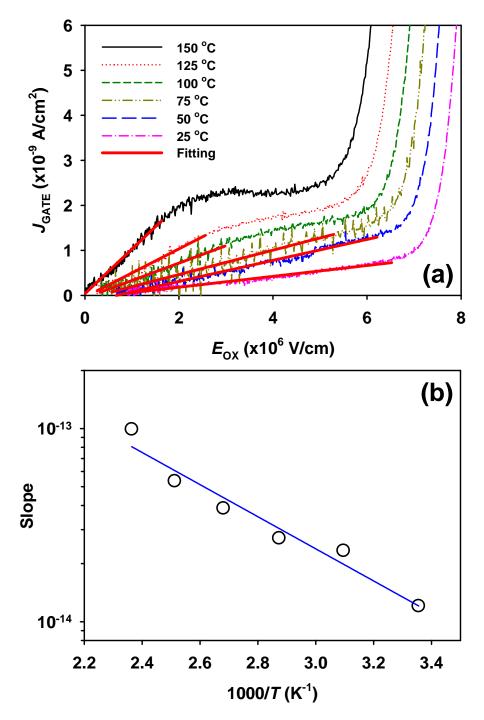

| Fig. | 3-2 | 8 Plots of $J_{\text{GATE}}$ versus $E_{\text{OX}}$ for the annealed Ge16-1E16 sample measured at various temperatures. The low-field region can be partially fitted by a straight line. In (b), the slope as a function of $1000/T$ obtained from the linear fitting is shown.                             |

| Fig. | 3-2 | 9 Schematic diagram showing the nc-Ge distributed throughout the SiO <sub>2</sub> thin film                                                                                                                                                                                                                 |

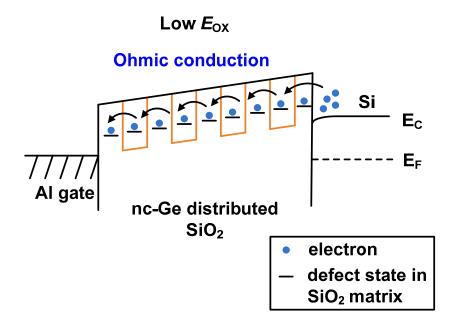

| Fig. | 3-3 | 0 Energy band diagram of the Ge-ion-implanted $SiO_2$ under a low $E_{OX}$ (i.e., in the low-field region).                                                                                                                                                                                                 |

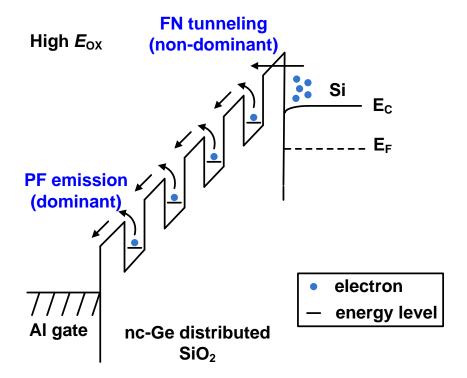

| Fig. | 3-3 | 1 Energy band diagram of the Ge-ion-implanted $SiO_2$ under a high $E_{OX}$ (i.e., in the high-field region).                                                                                                                                                                                               |

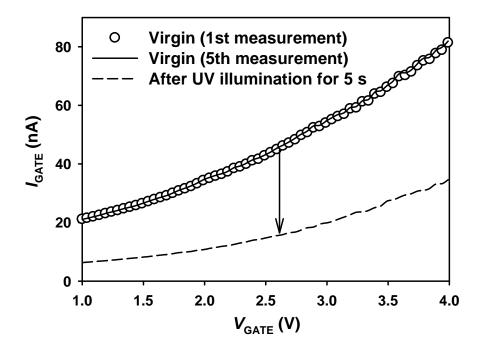

| Fig. | 3-3 | 2 Current-voltage ( $I$ - $V$ ) characteristics before and after UV illumination for 5 s. The repeated $I$ - $V$ measurements without UV illumination are also shown115                                                                                                                                     |

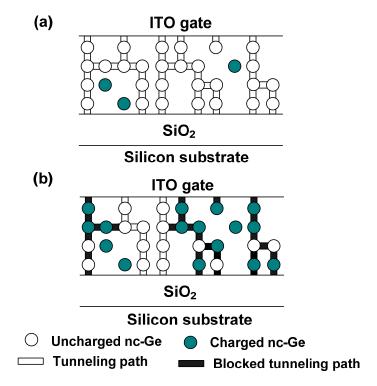

| Fig. | 3-3 | 3 A proposed model of the effect of charging and discharging in nc-Ge on the current conduction of the gate oxide. (a) Conductive paths formed by uncharged nc-Ge; and (b) blocked paths due to charging in nc-Ge                                                                                           |

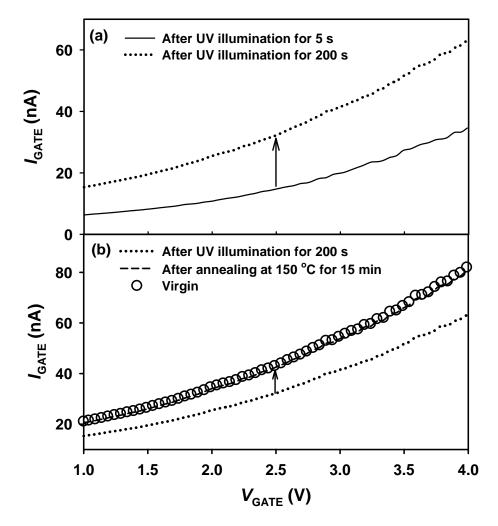

| Fig. | 3-3 | 4 (a) Partial recovery of the gate current after another UV illumination for 200 s from the situation of the UV illumination for 5 s. (b) Full recovery of the gate current after an annealing at 150 °C for 15 min in addition to the UV illumination for 200 s                                            |

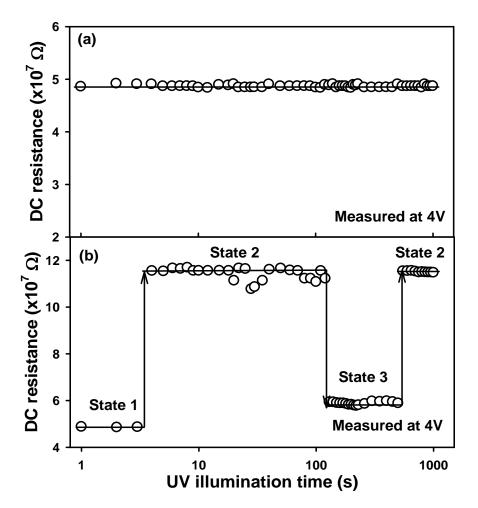

| Fig. | 3-3 | 5 Time-domain measurement of the DC resistance of the oxide: (a) without UV illumination; and (b) with UV illumination. The DC resistance was measured at a gate voltage of 4 V                                                                                                                             |

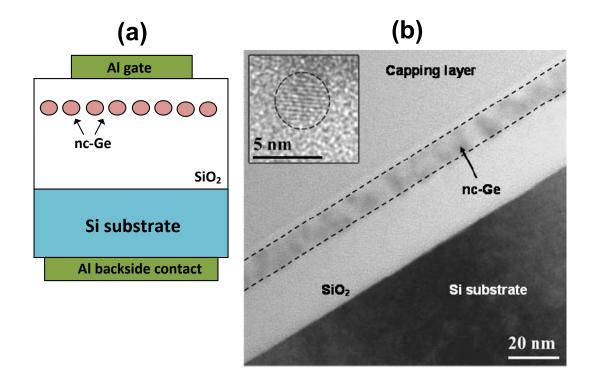

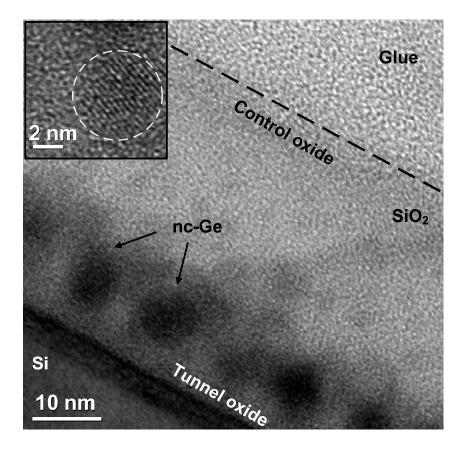

| Fig. | 4-1 | (a) Schematic diagram showing the MOS structure with nc-Ge confined in a narrow layer near Al gate, and (b) Cross-sectional TEM image showing a narrow layer of nc-Ge located in the surface region of the SiO <sub>2</sub> . The inset shows the TEM image of a single nc-Ge                               |

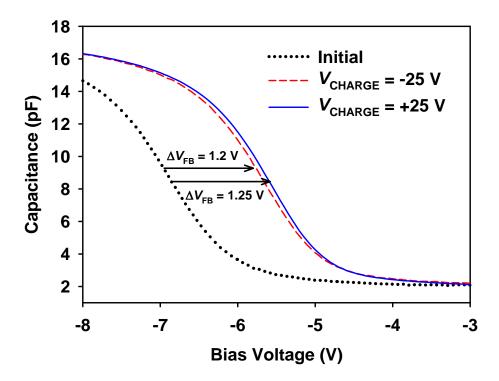

| Fig. | 4-2 | Shifts in the high-frequency (1 MHz) $C$ - $V$ characteristics after the charging at $V_{\text{CHARGE}} = +25 \text{ V}$ or $-25 \text{ V}$ for 1 s                                                                                                                                                         |

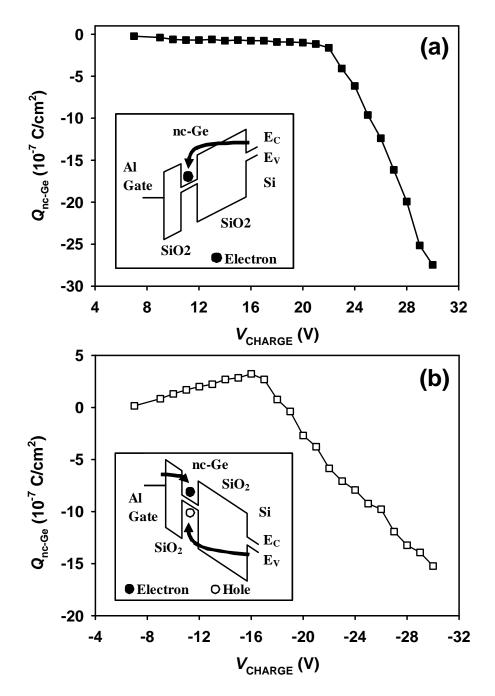

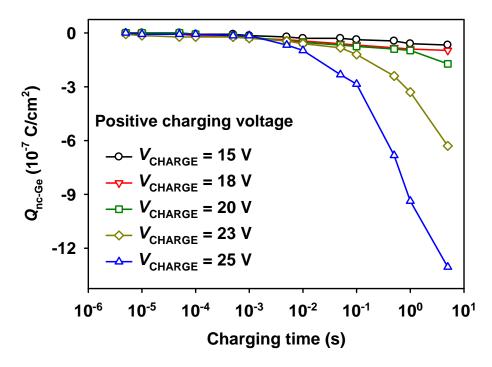

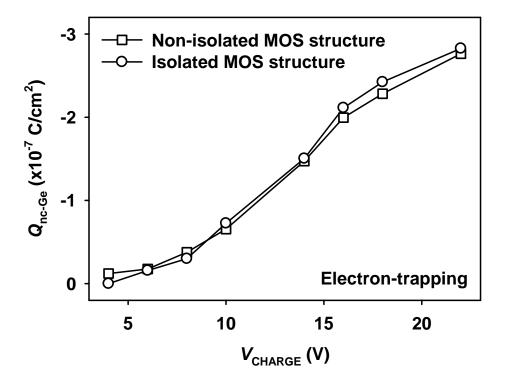

| Fig. | 4-3 | Density $(Q_{\text{nc-Ge}})$ of trapped charges as a function of the charging voltage $(V_{\text{CHARGE}})$ : (a) positive charging voltage; and (b) negative charging voltage. The charging time is fixed at 1 s. The insets show the charging mechanisms under a positive or negative $V_{\text{CHARGE}}$ |

| Fig. | 4-4 | Density $(Q_{\text{nc-Ge}})$ of trapped charges as a function of the charging time for different positive $V_{\text{CHARGE}}$                                                                                                                                                                               |

| Fig. 4-5 Density ( $Q_{\text{nc-Ge}}$ ) of trapped charges as a function of the charging time for different negative $V_{\text{CHARGE}}$                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

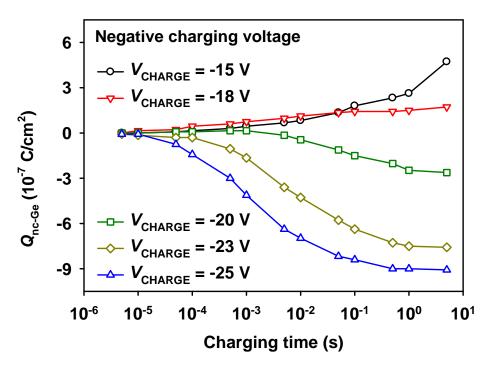

| Fig. 4-6 Charge retention characteristics for positive charging voltages (a) and negative charging voltages (b). The charging time is fixed at 1 s. The insets show the energy band diagrams during the retention experiment                                                                           |

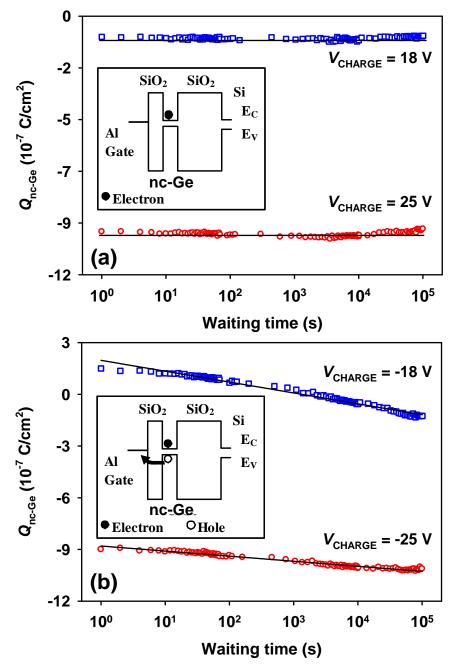

| Fig. 4-7 FWHMs and peak locations of the Ge distributions in the SiO <sub>2</sub> thin films as functions of annealing temperature obtained from the Gaussian fittings to the SIMS depth profiles.                                                                                                     |

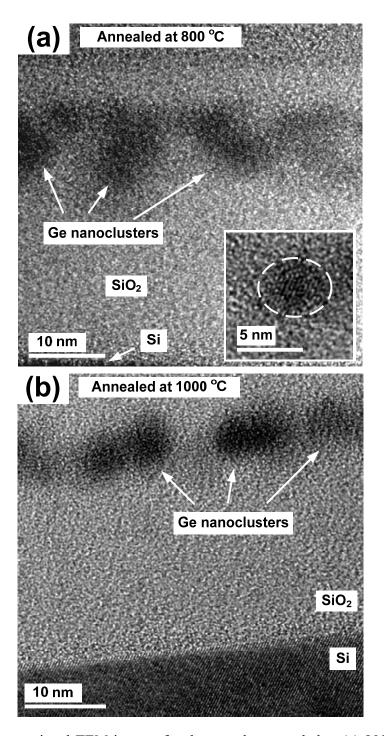

| Fig. 4-8 Cross-sectional TEM images for the samples annealed at (a) 800 °C and (b) 1000 °C, respectively                                                                                                                                                                                               |

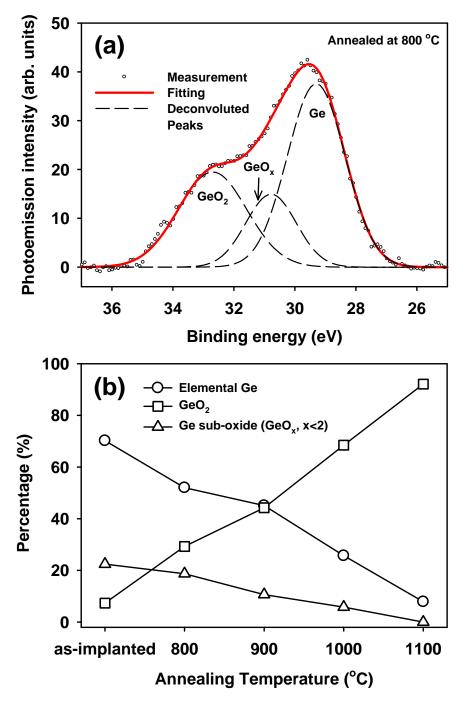

| Fig. 4-9 (a) Typical peak deconvolution of the Ge <i>3d</i> core level for the sample annealed at 800 °C; (b) Atomic percentages of elemental Ge, stoichiometric Ge oxide (GeO <sub>2</sub> ) and Ge sub-oxides (GeO <sub>x</sub> , x<2) as functions of annealing temperature                         |

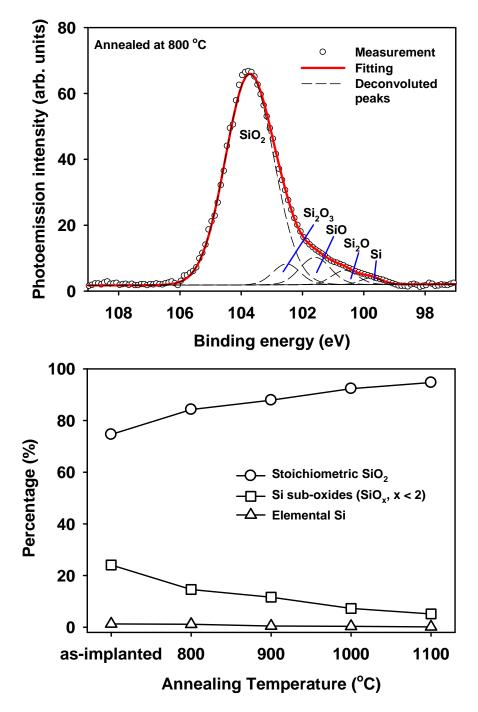

| Fig. 4-10 Typical peak deconvolution of the Si <i>2p</i> core level for the sample annealed at 800 °C; (b) Atomic percentages of stoichiometric SiO <sub>2</sub> , Si sub-oxides (SiO <sub>x</sub> , x<2) and elemental Si as functions of the annealing temperature 150                               |

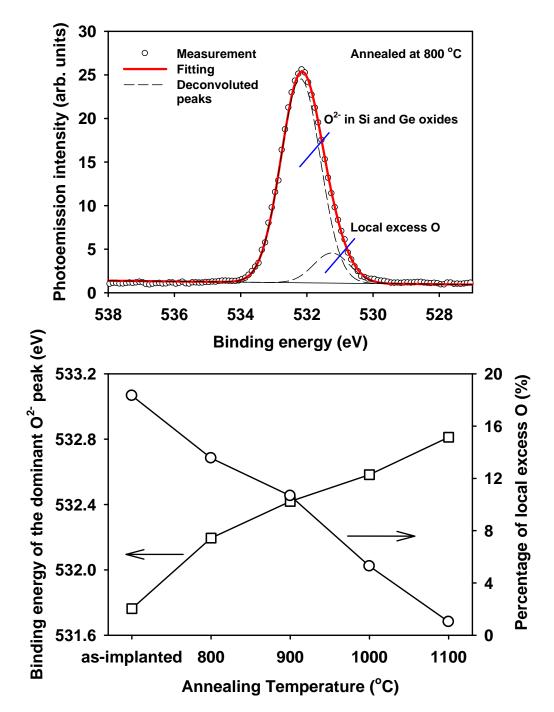

| Fig. 4-11 Typical peak deconvolution of the O <i>Is</i> core level for the sample annealed at 800 °C; (b) Binding energy of the dominant O <sup>2-</sup> peak and the percentage of local excess O atoms as functions of the annealing temperature151                                                  |

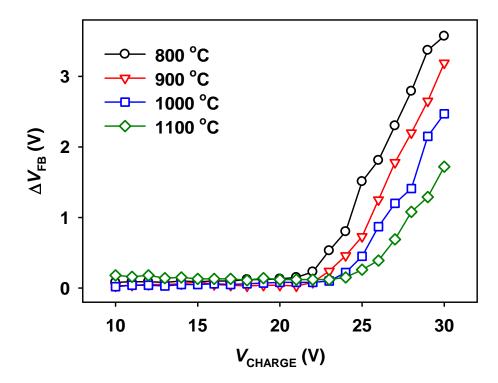

| Fig. 4-12 $\Delta V_{\rm FB}$ as a function of the positive $V_{\rm CHARGE}$ for different annealing temperatures. The charging duration is 1 s                                                                                                                                                        |

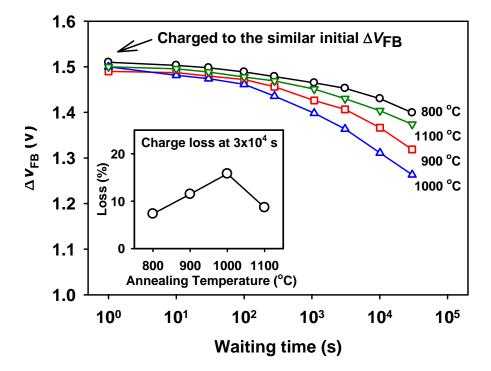

| Fig. 4-13 Charge retention behavior for different annealing temperatures. All the samples were charged to a similar level of initial $\Delta V_{\rm FB}$ . The inset shows the percentages of charge loss after $3\times10^4$ s for all the samples                                                    |

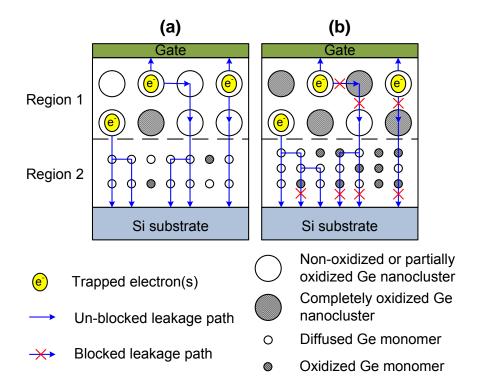

| Fig. 4-14 Schematic diagrams showing the two competing mechanisms that affect the charge retention: (a) formation of leakage paths by the Ge leakage sites (nc-Ge and Ge monomers); and (b) blocking of the leakage paths due to the oxidation of the Ge leakage sites.                                |

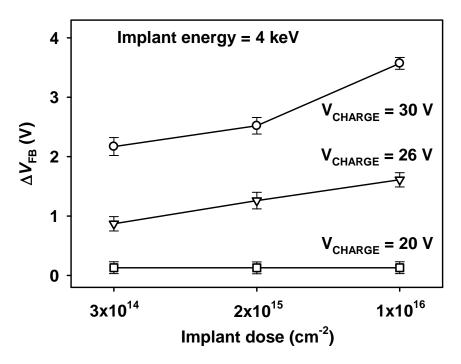

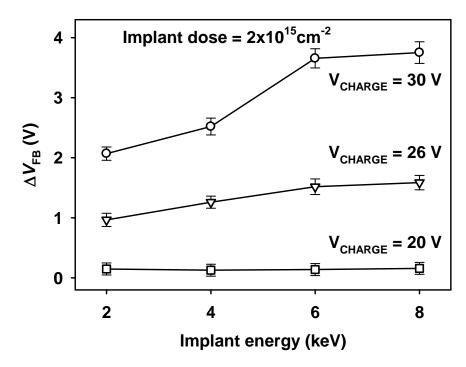

| Fig. 4-15 Influence of the implant dose on $\Delta VFB$ under various charging voltages159                                                                                                                                                                                                             |

| Fig. 4-16 Influence of the implant energy on the $\Delta V_{\rm FB}$ under various charging voltages.                                                                                                                                                                                                  |

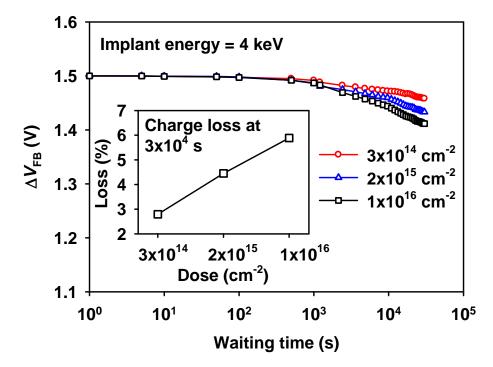

| Fig. 4-17 $\Delta V_{\rm FB}$ as a function of waiting time for samples with the same implant energy but different doses. All the samples were charged to the same level of initial $\Delta V_{\rm FB}$ . The insets show the charge loss after $3\times10^4$ s for different implantation conditions. |

| Fig. 4-18 $\Delta V_{\rm FB}$ as a function of waiting time for samples with the same implant dose                                                                                                                                                                                                     |

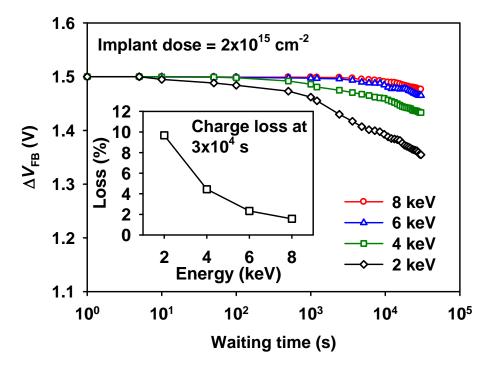

|          | but different energies. All the samples were charged to the same level of initial $\Delta V_{\rm FB}$ . The insets show the charge loss after $3\times10^4$ s for different implantation conditions.                                                                                                                      |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4-1 | 9 Schematic diagram showing two charge transfer paths: 1) leakage to Al gate / Si substrate, 2) lateral charge transfer                                                                                                                                                                                                   |

| Fig. 4-2 | 0 SIMS depth profiles of Ge in the as-implanted sample (a) and the annealed sample (b). The Si depth profiles are also shown to identify the oxide / Si interface.                                                                                                                                                        |

| Fig. 4-2 | 1 Cross-sectional TEM image showing a layer of nc-Ge embedded in the gate oxide near the Si substrate. The inset shows the TEM image of a single nc-Ge                                                                                                                                                                    |

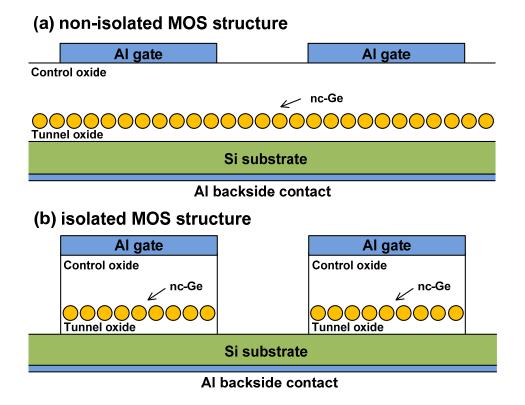

| Fig. 4-2 | 22 Schematic diagrams for the non-isolated (a) and the isolated MOS (b) structures                                                                                                                                                                                                                                        |

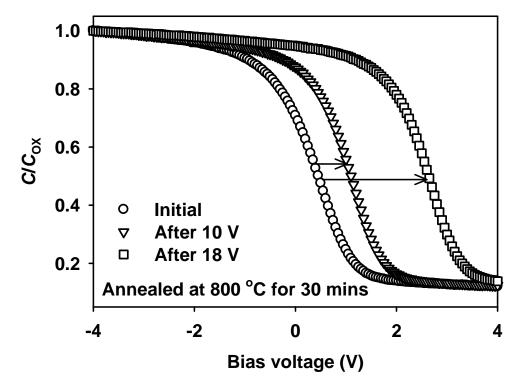

| Fig. 4-2 | 3 Shifts in the $C$ - $V$ characteristic caused by the charging at $V_{\text{CHARGE}} = 10$ and 18 V for 1 s                                                                                                                                                                                                              |

| Fig. 4-2 | 4 Density ( $Q_{nc-Ge}$ ) of trapped electrons as a function of $V_{CHARGE}$ for (a) the non-isolated and (b) isolated MOS structures. The charging time is 1 s174                                                                                                                                                        |

| Fig. 4-2 | 5 Density of trapped electrons ( $Q_{\text{nc-Ge}}$ ) as a function of the waiting time for the non-isolated (a) and isolated (b) MOS structures                                                                                                                                                                          |

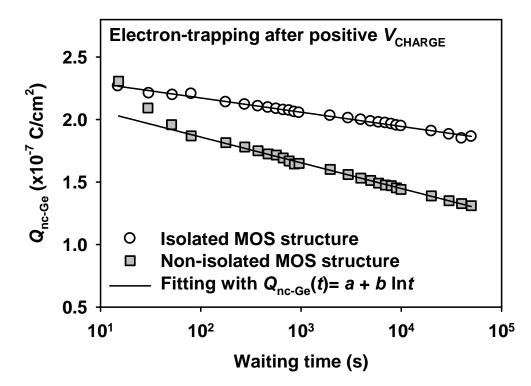

| Fig. 4-2 | 6 (a) Density of trapped electrons ( $Q_{\text{nc-Ge}}$ ) as a function of the waiting time for the non-isolated MOS structure. The charge decay due to Mechanism B is extrapolated; (b) Exponential charge decay corresponding to Mechanism A obtained from the difference between the two charge decay curves in (a)179 |

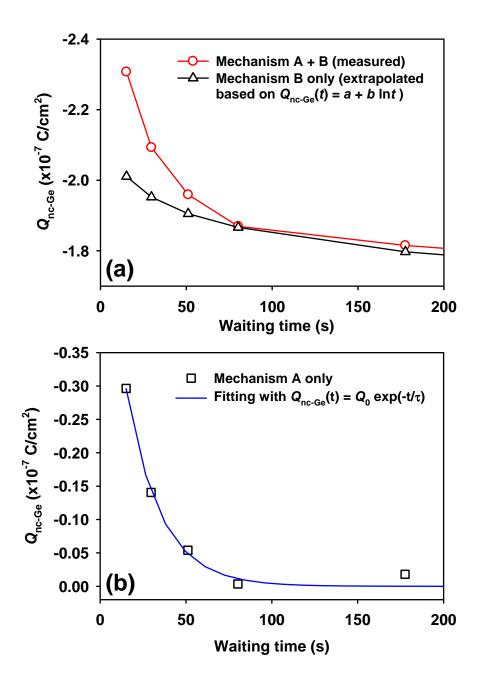

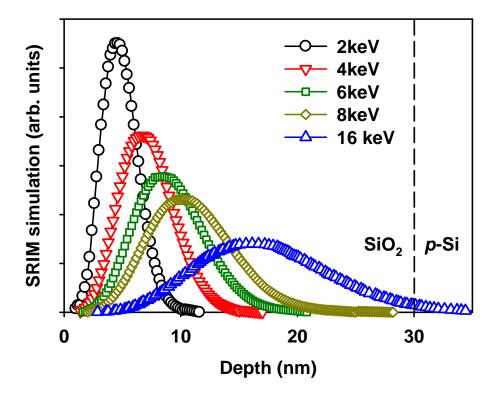

| Fig. 5-1 | SRIM simulation of the distribution of nc-Ge in the SiO <sub>2</sub> for different implant energies.                                                                                                                                                                                                                      |

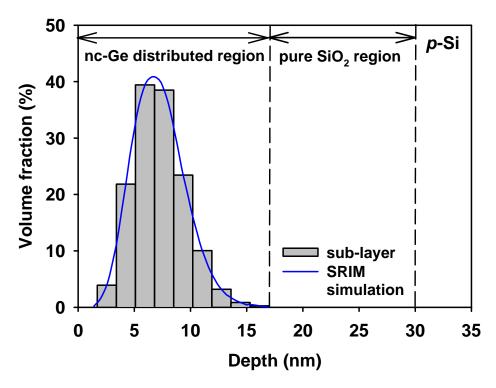

| Fig. 5-2 | A typical depth profile of volume fraction of nc-Ge in SiO <sub>2</sub> . The nc-Ge distributed region is divided into 10 sub-layers                                                                                                                                                                                      |

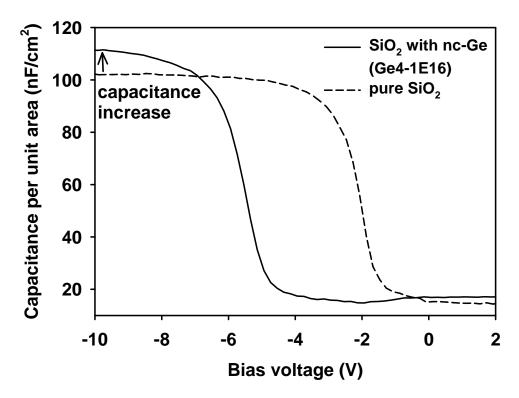

| Fig. 5-3 | Comparison of <i>C-V</i> characteristics between MOS structures with and without nc-Ge                                                                                                                                                                                                                                    |

| Fig. 5-4 | Calculated MOS capacitance as a function of $\varepsilon_{\text{nc-Ge}}$ for the Ge4-1E16 sample. Based on the measured MOS capacitance, the $\varepsilon_{\text{nc-Ge}}$ corresponding to the nc-Ge embedded in SiO <sub>2</sub> of the Ge4-1E16 sample can be estimated                                                 |

| Fig. 5-5 | Depth distribution of the effective dielectric constant of SiO <sub>2</sub> embedded with nc-Ge: (a) partial distribution of nc-Ge near the SiO <sub>2</sub> surface under the implant energy of 4 keV, and (b) full distribution of nc-Ge under the implant energy of 16 keV.                                            |

|          |                                                                                                                                                                                                                                                                                                                           |

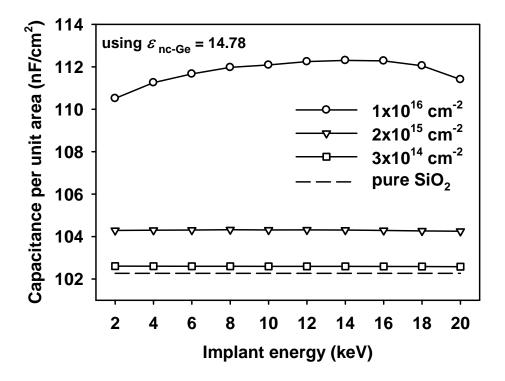

| Fig. 5-6 Influence of the implant energy on the calculated MOS capacitance 199                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

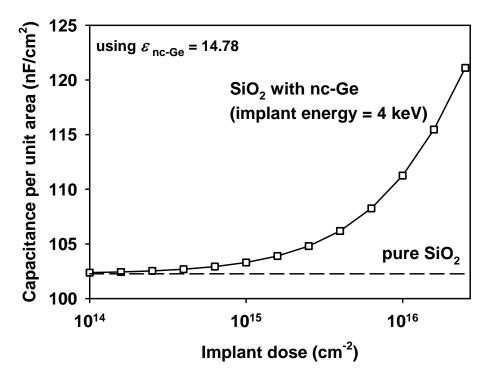

| Fig. 5-7 Influence of the implant dose on the calculated MOS capacitance200                                                                                                                                                                                                                                                     |

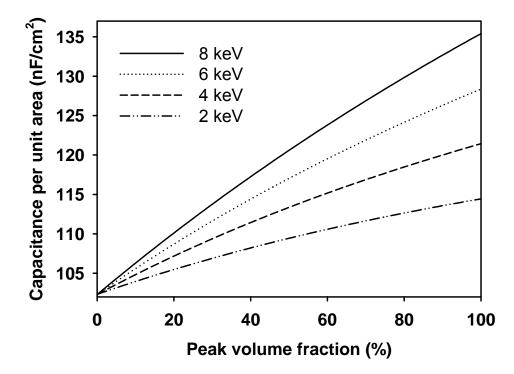

| Fig. 5-8 Calculated MOS capacitance as a function of the peak volume fraction of the nc-Ge in SiO <sub>2</sub> for different implant energies                                                                                                                                                                                   |

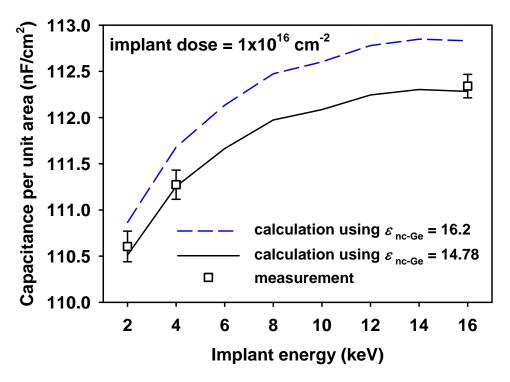

| Fig. 5-9 Calculated MOS capacitance using $\varepsilon_{\text{nc-Ge}} = 16.2$ (i.e., dielectric constant of the bulk crystalline Ge) and $\varepsilon_{\text{nc-Ge}} = 14.78$ as a function of the implant energy. The measured MOS capacitance is consistent with the calculation using $\varepsilon_{\text{nc-Ge}} = 14.78$ . |

| Fig. 6-1 Schematic diagram of the light-emitting device with a structure of ITO / Geion-implanted $SiO_2$ / $Si$ substrate / $Al$ backside contact                                                                                                                                                                              |

| Fig. 6-2 Schematic diagram for the setup of an EL characterization system208                                                                                                                                                                                                                                                    |

| Fig. 6-3 (a) Distribution of implanted Ge in SiO <sub>2</sub> obtained from SIMS measurement for the annealed Ge6-2E15 sample, and (b) Cross-sectional TEM image of nc-Ge embedded in SiO <sub>2</sub> for the annealed Ge6-2E15 sample210                                                                                      |

| Fig. 6-4 Typical EL spectra obtained from the Ge-ion-implanted $SiO_2$ thin film (Ge6-2E15 sample annealed at 800 °C for 1 hour) under different $V_{\rm GATE}$ 212                                                                                                                                                             |

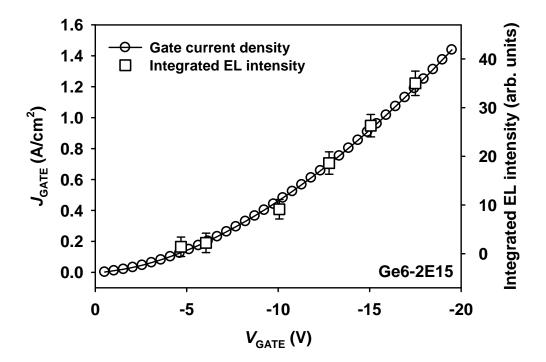

| Fig. 6-5 Dependence of the gate current density ( $J_{\text{GATE}}$ ) and the integrated EL intensity on the $V_{\text{GATE}}$ .                                                                                                                                                                                                |

| Fig. 6-6 A typical EL peak deconvolution for the annealed Ge6-2E15 sample under $V_{\rm GATE} = -15$ V showing the contribution of three EL bands                                                                                                                                                                               |

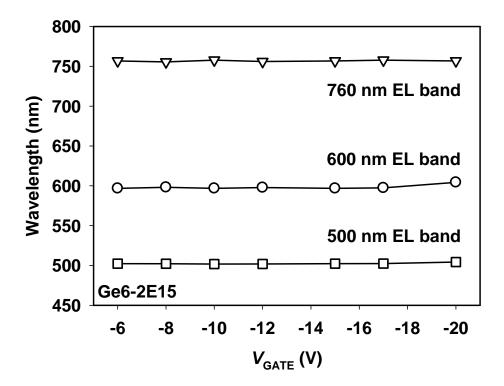

| Fig. 6-7 Evolution of the peak wavelength of each EL band with the $V_{\rm GATE}$ for the annealed Ge6-2E15 sample                                                                                                                                                                                                              |

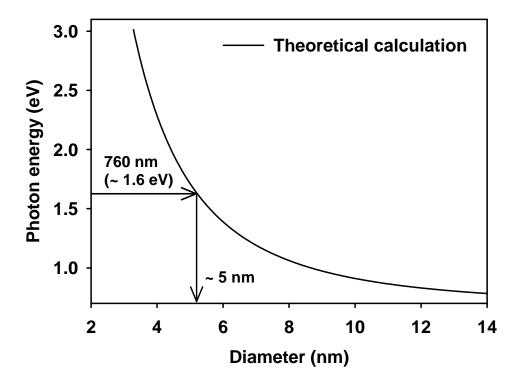

| Fig. 6-8 Calculated photon energy of excitons in nc-Ge as a function of the nanocrystal diameter based on the quantum confinement theory (from Ref. [260])                                                                                                                                                                      |

| Fig. 6-9 EL spectra corresponding to samples with different implant doses obtained under the constant voltage injection at $V_{\rm GATE}$ = -15 V. The implant energy is 4 keV                                                                                                                                                  |

| Fig. 6-10 EL spectra corresponding to samples with different implant energies obtained under the constant voltage injection at $V_{\rm GATE} = -15$ V. The implant dose is $2 \times 10^{15}$ cm <sup>-2</sup> .                                                                                                                |

| Fig. 6-11 Gate current density versus gate voltage ( $J_{\text{GATE}}$ - $V_{\text{GATE}}$ ) characteristics for (a) samples with a constant implant energy and various implant doses, and (b) samples with a constant implant dose and various implant energies223                                                             |

| Fig. 6-12 Depth profiles of the number of displacements in the Ge-implanted SiO <sub>2</sub> thin film for various implant energies obtained from the SRIM simulation225                                                                                                                                                        |

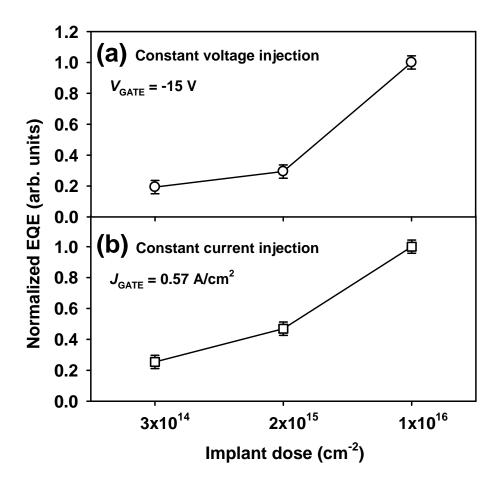

| Fig. 6 | 6-13 Dependence of the external quantum efficiency (EQE) of constant voltage injection at $V_{\text{GATE}} = -15 \text{ V}$ ; and (b) constant $J_{\text{GATE}} = 0.57 \text{ A/cm}^2$ . | ant current injection |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

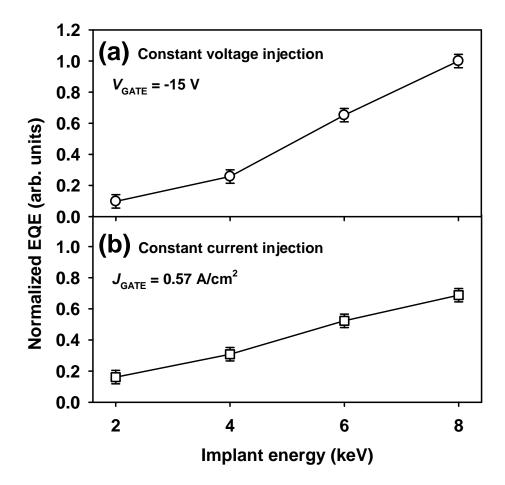

| Fig. 6 | 6-14 Dependence of the external quantum efficiency (EQE) or constant voltage injection at $V_{\text{GATE}} = -15 \text{ V}$ ; and (b) constant $J_{\text{GATE}} = 0.57 \text{ A/cm}^2$ . | ant current injection |

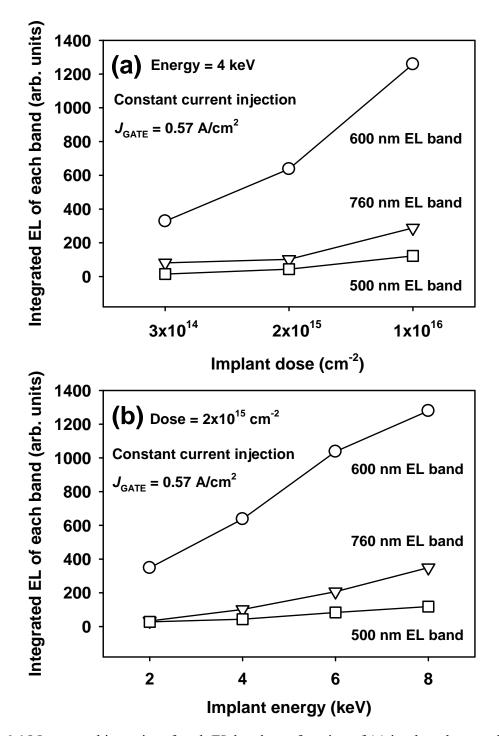

| Fig. 6 | 6-15 Integrated intensity of each EL band as a function of (a) implant energy. The EL measurements were conducted un injection at $J_{GATE} = 0.57 \text{ A/cm}^2$                       | der constant current  |

# List of Tables

# LIST OF TABLES

| Table 1 C | Comparison of various nc-Ge synthesis techniques                                                       |

|-----------|--------------------------------------------------------------------------------------------------------|

| Table 2 S | Summary of various implant conditions for the study of electrical properties.6                         |

| Table 3 S | summary of various implant conditions for the modeling of capacitance 190                              |

|           | Comparison between calculated and measured MOS capacitances for sample with various implant conditions |

#### Nomenclatures

### **NOMENCLATURES**

CMOS Complementary Metal Oxide Semiconductor

*C-V* Capacitance-Voltage

CVD Chemical Vapor Deposition

DRAM Dynamic Random Access Memory

EEPROM Electrical Erasable/Programmable Read Only Memory

EFM Electrostatic Force Microscopy

EL Electroluminescence

EMA Effective Medium Approximation

EPROM Erasable and Programmable Read Only Memory

EQE External Quantum Efficiency

FELED Field-Effect Light-Emitting Device

FET Field-Effect Transistor

FG Floating-Gate

FIB Focused Ion Beam

FN Fowler-Nordheim

FWHM Full Width at Half Maximum

GODC Germanium Oxygen Deficiency Center

HRTEM High Resolution Transmission Electron Microscopy

ITO Indium Tin Oxide

ITRS International Technology Roadmap for Semiconductor

*I-V* Current-Voltage

LPCVD Low Pressure Chemical Vapor Deposition

MBE Molecular Beam Epitaxy

#### Nomenclatures

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOSLED Metal Oxide Semiconductor Light Emitting Device

N<sup>2</sup>FC Nanyang NanoFabrication Center

NBOHC Non-Bridging Oxygen Hole Center

nc-Ge Ge nanocrystals

nc-Si Si nanocrystals

NOV Neutral Oxygen Vacancy

NVM Non-Volatile Memory

ONO Oxide Nitride Oxide

P/E Program / Erase

PECVD Plasma Enhanced Chemical Vapor Deposition

PF Poole-Frenkel

PL Photoluminescence

PLD Pulse Laser Deposition

PMT Photomultiplier Tube

RF Radio Frequency

RTA Rapid Thermal Annealing

SEM Scanning Electron Microscope

SET Single Electron Tunneling

SIMS Secondary Ion Mass Spectroscopy

SMU Source Measurement Unit

SRIM Stopping and Range of Ions in Matter

TCAD Technology Computer Aided Design

TEM Transmission Electron Microscopy

#### Nomenclatures

UHVCVD Very High Vacuum Chemical Vapor Deposition

ULSI Ultra Large Scale Integration

UV Ultra-Violet

VLSI Very Large Scale Integration

WORM Write Once Read Many Times

XPS X-ray Photoelectron Spectroscopy

XRD X-ray Diffraction

This thesis studies the electrical and optoelectronic properties of Ge-ion-implanted SiO<sub>2</sub> thin films embedded with Ge nanocrystals (nc-Ge) for applications in non-volatile memories and light-emitting devices. This chapter introduces the background, motivation, objective and major contributions of this thesis. Details of this study are presented in the following chapters.

## 1.1 Brief introduction to non-volatile memory devices

Non-volatile memory represents a class of solid-state memory whose contents are retained even if the electric power is turned off. That is in contrast to the volatile memory, e.g., dynamic random access memory (DRAM), which will lose the stored information without the electric power. The history of non-volatile memory started in mid-1960s with the invention of the first non-volatile memory cell by Kahng and Sze [1]. Since then, various non-volatile memory structures have been invented, including erasable and programmable read only memory (EPROM) [2], electrical erasable/programmable read only memory (EEPROM) [3], and Flash memory [4]. Starting from the mid-1990s, the development of Flash memory and the expansion of battery-supplied consumer electronic appliances such as mobile phones, digital music players and digital cameras have ignited the dramatic growth of the non-volatile memory market, which is dominated by the Flash memory. In 2009, the worldwide sales of Flash are predicted as \$15.9 billion US dollars, which accounts for 8% percent

of the total semiconductor sales [5]. Flash is also projected to grow over the next five years with an average annual growth of 17% until it reaches an estimated \$34.3 billion US dollars by 2014 [5].

The current Flash memory structure is based on the floating-gate (FG), which is a polycrystalline silicon layer completely surrounded by the gate dielectric of a field-effect transistor (FET). During the device operations, charges can be injected into or removed from the FG by the applied electric field. The amount of charges stored in the FG can be easily detected since it is directly proportional to the threshold voltage. The two most common types of Flash memory, NOR Flash [6] and NAND Flash [7, 8], are based on the FG design. According to the 2008 International Technology Roadmap for Semiconductors (ITRS), the FG-based Flash technology has reached the 40 nm node with a cell size of 0.0064  $\mu$ m² for the NAND Flash, and 50 nm node with a cell size of 0.025  $\mu$ m² for the NOR Flash [9]. Following the ITRS, several prototypes, such as the 120 mm² 16 Gb 4-level NAND flash using 43 nm technology [10], 16 Gb 16-level NAND Flash with a cell size of 0.006  $\mu$ m² using 70 nm technology [11], and the NOR Flash with a cell size of 0.024  $\mu$ m² using 45 nm technology [12], have been demonstrated.

# 1.2 Brief introduction to Si-compatible optoelectronic devices

Optical technology for the use of handling information has been around for several decades. For example, the optical fiber communication is an indispensable technique for dealing with the growing demand for data transfer, communications and network system. Another example is the success of various portable optical storage

mediums such as CD and DVD which offer low-cost and high-density information storage. Traditionally, several optoelectronic functional units, such as light source, modulator, switch and detector, are coupled electrically and/or optically with many other components to realize system functions needed for practical applications. Recently, the constantly growing demand of compact systems capable of performing new and increased numbers of operations has encouraged the integration of these optoelectronic devices with other optical and electronic circuits [13]. The optoelectronic integration can reduce the manufacturing cost and improve the system reliability. The future trend of optoelectronic integration would be the realization of optical interconnects for the chip-to-chip and intra-chip communication, because the traditional electrical interconnects based on metal wires are now suffering from substantial propagation delay, high power consumption, and low bandwidth as the line width of the wires reduce [14].

Si is the choice of material for modern microelectronics, and Si-based microelectronic devices, which are fabricated by the mainstream complementary metal-oxide-semiconductor (CMOS) technology, constitute over 95% of the market of semiconductor devices [15]. Thus, the optoelectronic integration on Si substrates using CMOS-compatible technology is the most cost-effective approach. Using CMOS-compatible technology also allows very large scale integration (VLSI) with great flexibility in device geometries including nanostructures, optical cavity and motion structures [16]. However, the current optoelectronic devices use a wide range of different materials, and most of them are not CMOS-compatible. For example, common light source and photodiodes are mainly based on Group III-V

semiconductor materials, while modulators and switches are based on LiNbO<sub>3</sub> or BaTiO<sub>3</sub> [17]. Therefore, to realize the CMOS-compatible optoelectronic integration on Si substrate, the fabrication of individual optoelectronic devices using existing CMOS technology is important.

# 1.3 Nanocrystals

Nanotechnology, which presents a collection of technologies that operates, analyzes and controls materials at the nano-scale regime, is beginning to be seen in products in our daily life [18]. The semiconductor nanocrystal, which consists of a few tens to a few tens of thousands of atoms aligned in a crystalline form and has a typical size of 1 – 10 nm, is one of the essential building blocks in nanotechnology. Recently, SiO<sub>2</sub> films embedded with Si nanocrystals (nc-Si) and Ge nanocrystals (nc-Ge) have attracted much attention for their promising applications in non-volatile memories as well as Si-compatible optoelectronic devices.

#### 1.3.1 Roles of nanocrystals for next-generation non-volatile memories

The modern electronic applications demand the down scaling of non-volatile memory devices in pursuit of larger capacity, smaller device area, lower power consumption and higher operating speed. However, the conventional FG design has a limited potential for the continued scaling of the device structures. The limitation mainly results from the extreme requirements on the tunnel oxide separating the FG and the Si substrate [19]. In a FG-based structure, the tunnel oxide has to be thin in order to achieve program / erase operations with fast speed and low voltage (i.e., low

power consumption). However, the reduction of tunneling oxide thickness causes the degradation of retention performance and raises reliability issues. To achieve data retention time of 10 - 20 year and a lifetime of  $10^5$  cycles as requested by the industry, the Flash manufacturers have to compromise at a tunnel oxide thickness of 7 - 9 nm which is expected to remain constant from 2007 to 2015 [9]. As a result, the performance of conventional FG-based non-volatile memory has only limited improvement with device scaling, and the semiconductor manufacturers and researchers are constantly exploring new device structures to replace conventional FG design.

To overcome the limitation in conventional FG-based memory design, the use of nanocrystals to replace conventional FG has been proposed by Tiwari *et al.* [20]. In a nanocrystal-based memory, discrete charge storage nodes made of nanocrystals are embedded in the gate dielectric (typically SiO<sub>2</sub>) of a field effect transistor. Each nanocrystal is surrounded by the gate dielectric and is located at a small tunneling distance away from the Si substrate. To program the device, electrons are injected from the inversion layer in the Si substrate into nanocrystals via tunneling when the control gate is positively biased with respect to the Si substrate. Due to the smaller bandgap of the nanocrystal material, i.e., Si or Ge, as compared to the surrounding SiO<sub>2</sub> barriers, long-term charge storage in the nanocrystal is achieved. Although each nanocrystal only stores a few electrons, the collective effect of many charged nanocrystals shifts the threshold voltage of the device. The nanocrystal-based memory has the potential to use a thinner tunnel oxide without sacrificing the performance of charge retention. Moreover, the nanocrystal-based non-volatile memory is more robust

and fault-tolerant due to the nature of discrete charge storage as well as the Coulomb blockage effect which limits the removal of an electron from the nanocrystal.

#### 1.3.2 Roles of nanocrystals for Si-compatible optoelectronic devices

The integration of photonic and optoelectronic functional units into mainstream microelectronic circuits using Si-based CMOS technology has generated much research interest. Many promising demonstrations, such as optical modulators [21, 22], switches [23, 24], detectors [25, 26], and low-loss waveguides [27, 28], have been reported. However, it still remains a challenge to build a CMOS-compatible light emitter. It is known that bulk crystalline Si and Ge are poor in light emission at room temperature, mainly because of their indirect bandgaps which result in a phonon-mediated recombination process with low probability. In addition, fast non-radiative processes such as Auger or free carrier absorption prevent the population inversion for silicon optical transitions at the high pumping rates needed to achieve optical amplification. Thus, a Si-compatible light emitter is still under extensive research.

Among many solutions to build a Si-compatible light emitter, the use of Group-IV nanocrystals (i.e., nc-Si or nc-Ge) embedded in SiO<sub>2</sub>, which was motivated by the early work on visible light emission from porous silicon [29, 30], has recently attracted great interest. The major reason for using nanocrystals is the three-dimensional quantum confinement effect which leads to the expansion of the optical bandgap as a result of the size reduction of nanocrystals [31]. That provides a possible way to relax the momentum conservation requirement and allows Group IV semiconductors with indirect bandgap to possess efficient light emission properties.

Besides, the defects induced by the nanocrystal synthesis techniques could also contribute to the light emission from SiO<sub>2</sub> embedded with nanocrystals.

#### 1.3.3 Ge nanocrystals

To meet the demand of design, development and eventually manufacturing of non-volatile memories as well as Si-compatible light-emitting devices based on Group-IV nanocrystals, extensive research must be carried out to understand the synthesis, physics and device behavior of nanocrystals embedded in SiO<sub>2</sub>. Although the initial research activities on Group-IV nanocrystals were mainly focused on nc-Si, nc-Ge is also of great interest. Bulk Ge has a smaller bandgap, smaller electron and hole effective masses and a larger dielectric constant as compared to bulk Si. In addition, in bulk Ge the direct gap ( $E_0 \sim 0.88$  eV) is close to the indirect gap ( $E_g \sim 0.75$  eV) [32]. Thus, it is considered that quantum size effects would appear more pronounced in nc-Ge than in nc-Si [33]. As a result, as compared to Si, Ge is a more promising choice of material for the nanocrystal-based applications in non-volatile memories and Si-compatible light-emitting devices. Many studies have demonstrated that the synthesis of nc-Ge embedded in SiO<sub>2</sub> is fully compatible with the CMOS technology.

#### 1.4 Motivation

In view of the important roles of nc-Ge in non-volatile memory devices and Sicompatible light-emitting devices, the electrical and optoelectronic properties of nc-Ge deserve more thorough investigation. Nc-Ge embedded in SiO<sub>2</sub> can be synthesized by

many techniques [34-38], which have their own advantages and disadvantages. Among them, Ge ion implantation into SiO<sub>2</sub> films, followed by the high temperature annealing, is deemed as one of the most promising candidates for producing electrically and chemically stable nc-Ge embedded in SiO<sub>2</sub>. The ion implantation technique is fully compatible with the existing CMOS technology and is able to control the nc-Ge concentration and depth distribution by adjusting the implant energy and Ge ion dose [39]. For example, an orderly 2-D array or a narrow distribution of nc-Ge in SiO<sub>2</sub> is usually required for the non-volatile memory device application [40], and that can be achieved by the use of low-energy (e.g., 2 – 8 keV) ion implantation. On the other hand, to produce nc-Ge dispersed in SiO<sub>2</sub> which is occasionally required by some optoelectronic applications [41], a higher implant energy could be used. Besides its flexibility, the ion implantation process also provides good homogeneity and good reproducible profiles. As a result, in this thesis we focus on SiO<sub>2</sub> thin films embedded with nc-Ge synthesized by a Ge ion implantation technique.

The conventional SiO<sub>2</sub> film has long been studied since the fabrication of the first metal-oxide-semiconductor field-effect transistor (MOSFET) in 1960 [42], and it is well accepted that the current transport in the SiO<sub>2</sub> system depends on many factors, e.g., the material composition, fabrication process, film thickness, trap density, and so on. However, the current transport behavior of Ge-ion-implanted SiO<sub>2</sub> thin films has not been studied in detail. Ge-ion-implanted SiO<sub>2</sub> thin films differ from the pure SiO<sub>2</sub> in many aspects: 1) nc-Ge are formed in the SiO<sub>2</sub> matrix [41, 43-45], 2) defects / traps are created in the bulk of oxide film in a way similar to those cases of Cs- and B-ion-implanted oxide films [46]. For the applications of non-volatile memory and light-

emitting devices, the Ge-ion-implanted  $SiO_2$  embedded with nc-Ge serves as a gate dielectric layer sandwiched by the gate electrode and the Si substrate. Since both the charge storage and the light emission are caused by the charge injection into the Ge-ion-implanted  $SiO_2$ , an understanding of the current transport behavior of the Ge-ion-implanted  $SiO_2$  is necessary.

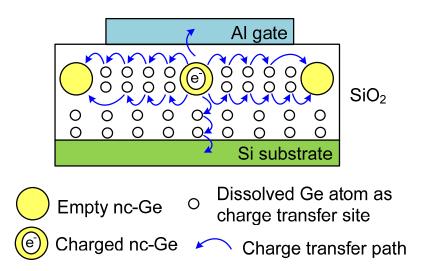

Besides the current transport behavior, the successful operation of non-volatile memory devices based on nc-Ge relies on the charge trapping and charge retention in the SiO<sub>2</sub> embedded with nc-Ge. Although the Ge-ion-implanted SiO<sub>2</sub> samples embedded with nc-Ge have been previously demonstrated to possess memory effects [43, 47, 48], their charge trapping and charge retention behavior has not been systematically studied. One of the advantages of the Ge ion implantation technique is the precise control of the density and depth distribution of the implanted ions by the process parameters such as implant energy, implant dose and annealing temperature. Thus, it is essential to understand the influences of these process parameters on the charge trapping and charge retention behavior. Besides, since the implanted Ge atoms can dissolve and diffuse in the SiO<sub>2</sub> matrix [49], excess Ge atoms are expected to be found in the oxide between adjacent nc-Ge particles as well as in the tunnel oxide separating the nc-Ge and the Si substrate. These dissolved Ge atoms could act as charge transfer sites and cause charge loss from the nc-Ge. It is important to understand how these dissolved Ge atoms affect the retention of charges trapped in nc-Ge.

For the Ge-ion-implanted SiO<sub>2</sub> thin films, due to the inclusion of nc-Ge in SiO<sub>2</sub>, the dielectric properties of SiO<sub>2</sub> will be modified. The possible contributing factors

include the depth and the distribution of nc-Ge in  $SiO_2$  and the change in the dielectric constant of nc-Ge as a result of the reduced size. As a consequence, the capacitance of the metal-oxide-semiconductor (MOS) structure is affected by the nc-Ge embedded in  $SiO_2$ . Experimentally, it is possible to measure the MOS capacitance using the conventional capacitance-voltage (C-V) technique. However, for the sake of design and modeling of memory structures based on nc-Ge, a modeling approach to determine the influence of nc-Ge on the MOS capacitance is essential. Such an approach is still not available in the literature.