### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

## Studies on high-frequency noise characteristics in deep submicron NMOSFETs

Zeng, Rong

2010

Zeng, R. (2010). Studies on high-frequency noise characteristics in deep submicron NMOSFETs. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/40925

https://doi.org/10.32657/10356/40925

Downloaded on 19 Apr 2025 16:03:56 SGT

#### Studies on High-frequency Noise Characteristics in Deep Submicron NMOSFETs

# ZENG RONG SCHOOL OF ELECTRICAL & ELECTRONIC ENGINEERING 2010

#### STUDIES ON HIGH-FREQUENCY NOISE CHARACTERISTICS IN DEEP SUBMICRON NMOSFETS

#### **ZENG RONG**

School of Electrical & Electronic Engineering

A thesis submitted to the Nanyang Technological University in fulfillment of the requirement for the degree of Doctor of Philosophy

2010

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to all those who gave me the possibility to complete this thesis.

I am deeply indebted to my supervisor Prof. Wang Hong who, stimulating suggestions and encouragement, helped me in all the time of research for and writing of this thesis. I am grateful to Prof. K. Radhakrishnan for his guidance and encouragement. I have furthermore to thank Dr. Daniel Lubrich who looked closely at the final version of the thesis for English style and grammar, correcting both and offering suggestions for improvement.

I would like to thank all my colleagues for their valuable comments and concern. I greatly appreciate my research colleagues Mr. Neo Wah Peng, Mr. Yuan Kai Hua, Mr. Tan Chee Leong, Mr. Yang Hong, Mr. Cheong Wai Chye, Ms. Bu Jing, Ms. Liu Yu Wei, Ms. Ng Chai Wah, Mr. Liu Zhi Hong and other research staffs and students for their assistance and helpful discussions.

I would like to specially thank our Clean Room and Characterization Lab technicians, Mr. Foo Tai Ho, Ms. Yong Puay Peng, Mr. Muhd Fauzi Bin Abdullah. All of them have offered invaluable help to my work and have made my stay at NTU enjoyable.

#### **Table of Contents**

Acknowledgments Table of Contents ii Summary **List of Figures** vii List of Tables ix Chapter 1 Introduction......1 CMOS technology for RFIC applications......1 1.1 1.2 Objectives......4 Major contributions......5 1.3 1.4 Organization of this thesis......8 Chapter 2 Theoretical investigation of noise in MOSFET and device physics ......9 2.1 Small signal model of MOSFET ......9 Sources of noise ......14 2.2 2.2.1 2 2 2 Thermal noise 15 2.2.3 2.2.4 2.2.5 Shot noise 20 2.2.6 Flicker noise 20 2.2.7 2.3 Noise parameters and noise two-port network ......22 2.4 Extraction of noise parameters......27 2.5 Gate oxide breakdown......30 2.5.1 2.5.2 2.6 Carrier heating and channel noise in sub-micron MOSFET......36 2.7 Summary......38 Chapter 3 Experiments......39 3.1 Devices.......39

| 3.2                            | Measurements                                                                                                      | 39             |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|

| 3.3                            | De-embedding                                                                                                      | 42             |

| 3.4                            | Summary                                                                                                           | 44             |

|                                | 4 Simplified Extraction of Channel Noise and Induced Gat<br>nicron RF MOSFETs for Fast Wafer Level RF Noise Measu |                |

| 4.1                            | Introduction                                                                                                      | 45             |

| <b>4.2</b> 4.2. 4.2. 4.2. 4.2. | <ul><li>2 Substrate network noise</li><li>3 Drain resistance noise</li></ul>                                      | 50<br>54<br>57 |

| 4.3                            | Experimental verification and discussion                                                                          | 60             |

| 4.4                            | Summary                                                                                                           | 64             |

|                                | 5 Effect of FN stress and gate oxide breakdown on high fre                                                        |                |

| 5.1                            | Introduction                                                                                                      | 69             |

| 5.2                            | Experiments                                                                                                       | 70             |

| 5.3                            | Results and Discussions                                                                                           | 70             |

| 5.4                            | Summary                                                                                                           | 86             |

|                                | 6 Impact of gate oxide breakdown location on high frequen                                                         |                |

| 6.1                            | Introduction                                                                                                      |                |

| 6.2                            | Experiments                                                                                                       |                |

| 6.3                            | Dependence of DC and RF noise performance on breakdo                                                              |                |

| 6.4                            | Results and discussions                                                                                           |                |

| 6.5                            |                                                                                                                   |                |

|                                | Design Consideration from Breakdown Location                                                                      |                |

| 6.6                            | Summary                                                                                                           |                |

|                                | · 7 An Experimental Study of Influence of Carrier Heating of Noise in Deep-Submicrometer NMOSFETs Via Body Bias   |                |

| 7.1                            | Introduction                                                                                                      | 107            |

| 7.2                            | Experiments                                                                                                       | 108            |

| 7.3                            | Effect of Reverse Body Bias on DC and RF Noise Perform 109                                                        | ance           |

| 7.4                            | Discussion                                                                                                        | 121            |

| 7.5     | Conclusions                        | 126 |

|---------|------------------------------------|-----|

| Chapte  | er 8 Conclusion and Recommendation | 128 |

| 8.1     | Conclusion                         | 128 |

| 8.2     | Recommendation for future works    | 129 |

| Author  | r's Publications                   | 131 |

| Bibliog | raphy                              | 135 |

#### **SUMMARY**

RF noise characteristics of deep sub-micrometer MOSFETs are investigated in this work.

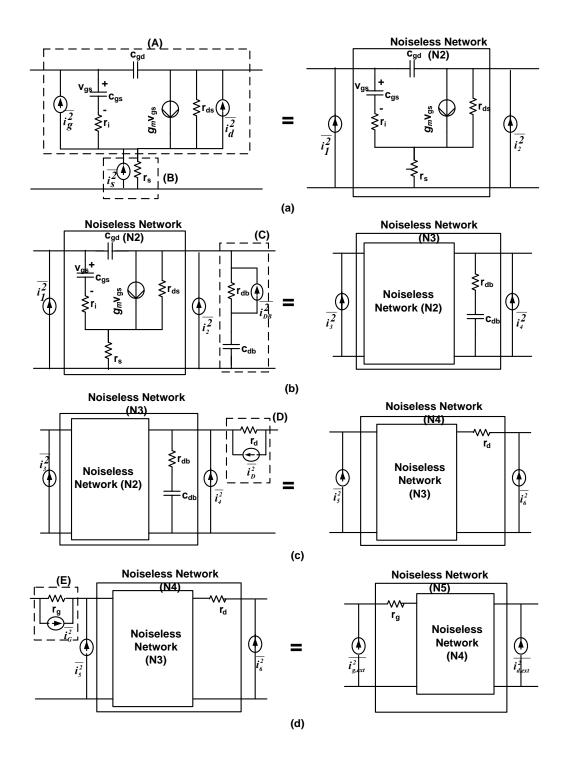

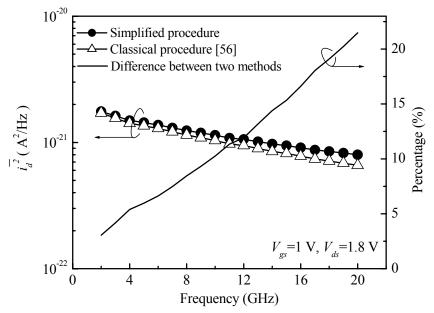

The direct matrix method to extract the channel thermal noise and induced gate noise is analyzed. In deep sub micron NMOSFETs, the contributions from some extrinsic elements are small and can be neglected. The procedure can therefore be simplified to a one-step matrix calculation. The obtained noise currents from the new method are in good agreement with those calculated from classical methods.

The impact of Fowler–Nordheim (FN) stress and oxide breakdown on high frequency noise characteristics in 0.18 µm NMOSFET has been studied. Noise characteristics of the devices at different leakage levels and breakdown hardness are compared. The results show a strong dependence of degradation of noise parameters on the gate leakage. The degradation mechanisms are analyzed by extraction of the channel and gate noise using a noise equivalent circuit model. It has been found that gate shot noise, which is commonly ignored in NMOSFETs, plays a dominant role in determining the high frequency noise in the post-oxide breakdown NMOSFETs.

The relation between the location of gate oxide breakdown in deep submicron MOSFETs and noise characteristics has been studied. RF Noise in the frequency range of 2 to 18 GHz of the devices with oxide breakdown at different locations are characterized and compared. The results show that

degradation of noise parameters subject to gate oxide breakdown is not only related to breakdown hardness but also the oxide breakdown path. For similar breakdown hardness, formation of the breakdown path closer to source side may result in a larger degradation of device RF noise performance.

RF noise in 0.18- $\mu$ m NMOSFETs concerning the contribution of carrier heating and hot carrier effect is characterized and analyzed in detail. A novel approach is used to modulate the channel carrier heating and number of hot carriers using body bias. We confirm qualitatively a negligible role of hot carrier effect on the channel noise in deep-sub micrometer MOSFETs. For a device under reverse body bias ( $V_b$ ), even though the increase in hot carrier population is clearly characterized by DC measurements, the device high-frequency noise is found to be irrelevant to the increase in the channel hot carriers. Experimental results show that the high-frequency noise is slightly reduced with the increase in body bias, and can be qualitatively explained by secondary effects such as the suppression of nonequilibrium channel noise and substrate induced noise. The reduction of minimum noise figure with the increase in body bias may provide a possible methodology to finely adjust the device high-frequency noise performance for circuit design.

#### **LIST of FIGURES**

| Figure 1.1 CMOS technology trend: cutoff frequency and $NF_{min}$ [1]3                                      |

|-------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Typical power curve of an amplifier with different noise floors                                  |

| [2]3                                                                                                        |

| Figure 2.1 The equivalent high-frequency small-signal model for                                             |

| MOSFETs11                                                                                                   |

| Figure 2.2 small-signal equivalent noise circuit of grounded substrate                                      |

| MOSFET21                                                                                                    |

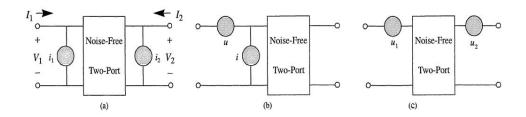

| Figure 2.3 Different representations of a noisy two-port network [20]22                                     |

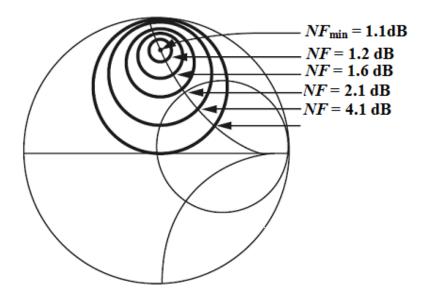

| Figure 2.4 Noise circles of a typical transistor. The noise circles are used to                             |

| display the complex relation between source impedance and noise                                             |

| figure26                                                                                                    |

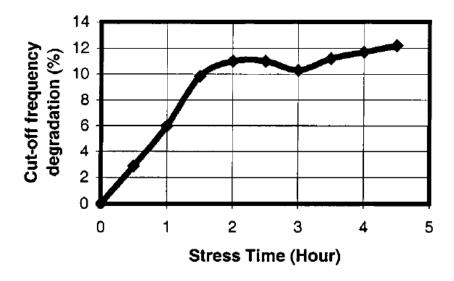

| Figure 2.5 Measured cut-off frequency degradation versus stress time [34]                                   |

| 31                                                                                                          |

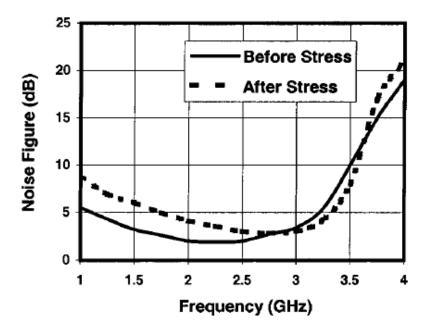

| Figure 2.6 Noise figure versus frequency before and after stress [34]31                                     |

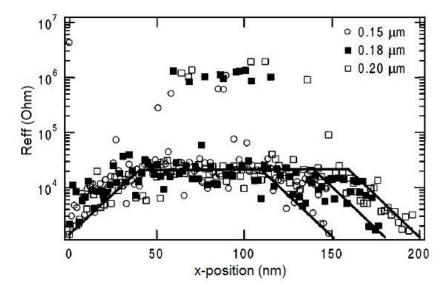

| Figure 2.7 Effective gate post breakdown resistance as a function of the                                    |

| breakdown spot location along the channel in three short-channel                                            |

| NMOSFETs [29]34                                                                                             |

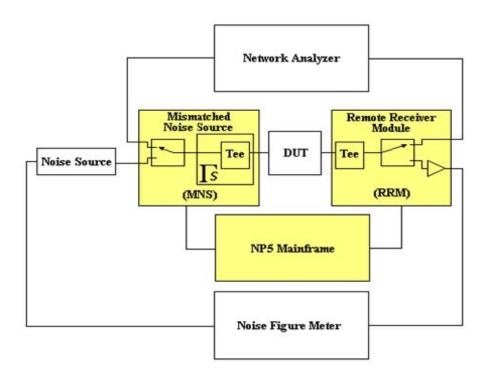

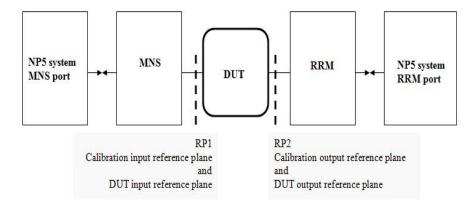

| Figure 3.1 NP5 system block diagram40                                                                       |

| Figure 3.2 Schematic for on-wafer noise calibration41                                                       |

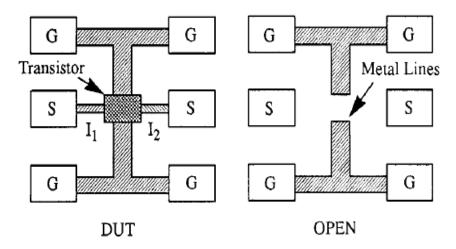

| Figure 3.3 Device and dummy layout for parasitics de-embedding [47]42                                       |

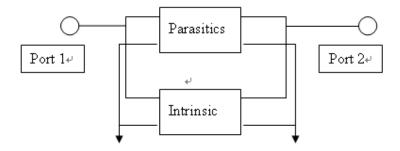

| Figure 3.4 Topology of the pads parasitics with the intrinsic transistor 43                                 |

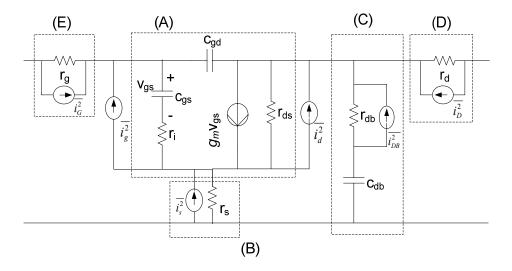

| Figure 4.1 Small signal equivalent noise circuit of substrate grounded                                      |

| MOSFET with five subnetworks: (A) the intrinsic part of the                                                 |

| transistor (B) the source resistance (C) the substrate network (D) the                                      |

| drain resistance and (E) the gate resistance network46                                                      |

| Figure 4.2 Network representation of the equivalent circuit: (A) the                                        |

| intrinsic part of the transistor (B) the source resistance (C) the                                          |

| substrate network (D) the drain resistance and (E) the gate resistance                                      |

| network49                                                                                                   |

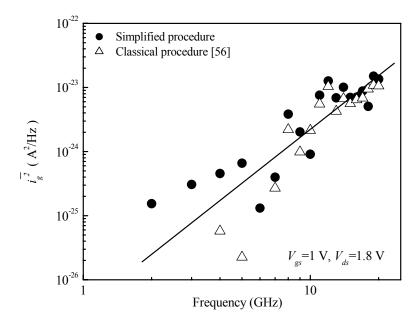

| Figure 4.3 Drain current thermal noise versus frequency at $V_g$ =1V,                                       |

| $V_{D}=1.8$ V65                                                                                             |

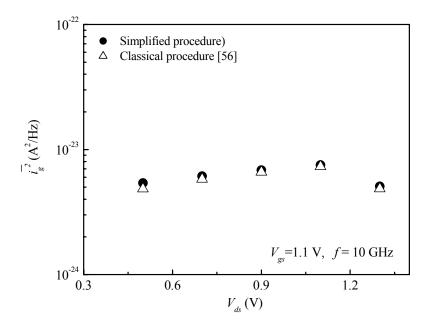

| Figure 4.4 Induced gate noise versus frequency at $V_g$ =1V, $V_D$ =1.8V66                                  |

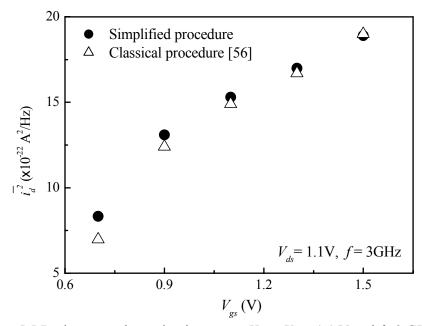

| Figure 4.5 Drain current thermal noise versus $V_{gs}$ at $V_{ds} = 1.1 \text{ V}$ and $f = 3$              |

| GHz66                                                                                                       |

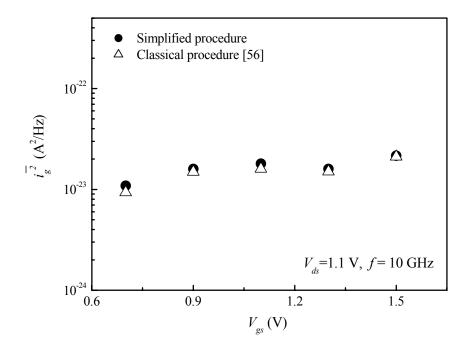

| Figure 4.6 Induced gate noise versus $V_{gs}$ at $V_{ds} = 1.1 \text{ V}$ and $f = 10 \text{ GHz} \dots 67$ |

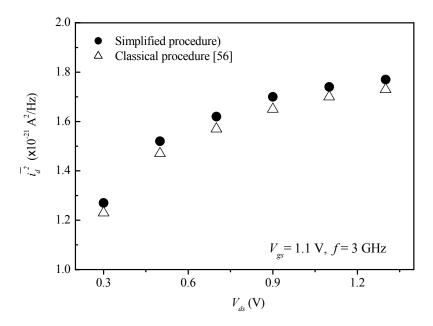

| Figure 4.7 Drain current thermal noise versus $V_{ds}$ at $V_{gs} = 1.1 \text{ V}$ and $f = 3$              |

| GHz67                                                                                                       |

| Figure 4.8 Induced gate noise versus $V_{ds}$ at $V_{gs} = 1.1 \text{ V}$ and $f = 10 \text{ GHz}$ 68       |

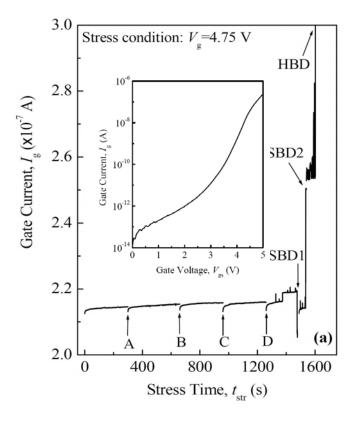

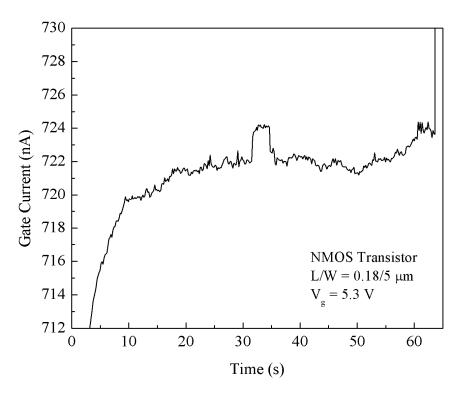

| Figure 5.1 Gate current as a function of stress time. The spikes shown in                                   |

| the pre-breakdown trace named as A to D are due to the interruptions                                        |

| during the stress, and SBD1, SBD2 and HBD are corresponding to the                                          |

| sequential soft and hard breakdowns in the device71                                                         |

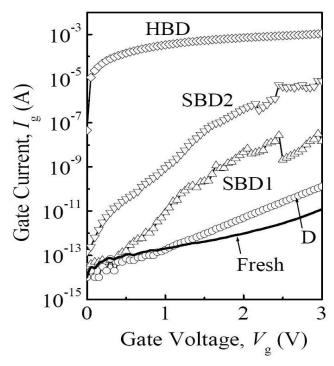

| Figure 5.2 Gate leakage measured at different stress interruptions73                                                         |

|------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.3 Fractional degradation of the saturation drain current                                                            |

| ( $\Delta I_{ m d,sat}$ $/$ $I_{ m d0,sat}$ ), transconductance ( $\Delta g_{ m m}$ $/$ $g_{ m m0}$ ), and threshold voltage |

| $(\Delta V_{\it th}  /  V_{\it th0})$ as a function of stress time. No drastic changes are induced                           |

| by the oxide breakdown events74                                                                                              |

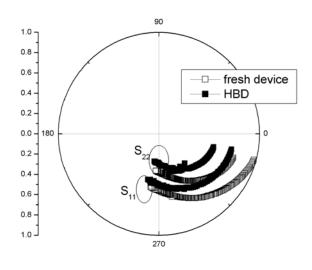

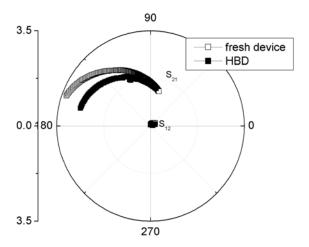

| Figure 5.4 Measured S-parameters before and after stress                                                                     |

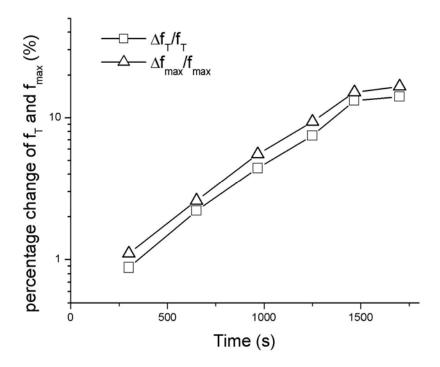

| Figure 5.5 Degradation of the cut-off frequency ( $\Delta f_T / f_T$ ) and maximum                                           |

| frequency ( $\Delta f_{\rm max}$ / $f_{\rm max}$ ) as a function of stress time77                                            |

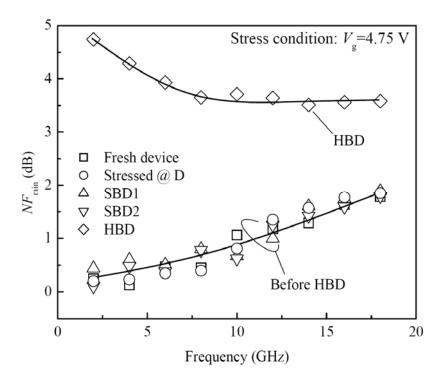

| Figure 5.6 $NF_{min}$ as a function of frequency measured during the stress79                                                |

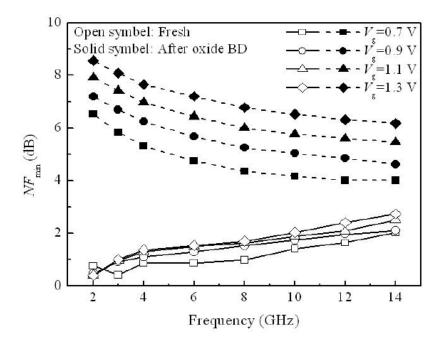

| Figure 5.7 De-embedded $NF_{min}$ of a 0.18 $\mu$ m n-MOSFET versus frequency                                                |

| as a function gate bias voltage measured before and after gate oxide                                                         |

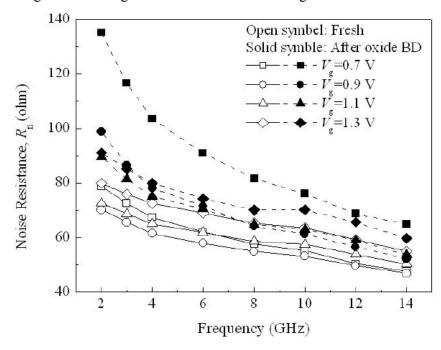

| breakdown80                                                                                                                  |

| Figure 5.8 De-embedded $R_n$ of a 0.18 $\mu$ m n-MOSFET versus frequency as a                                                |

| function gate bias voltage measured before and after gate oxide                                                              |

| breakdown                                                                                                                    |

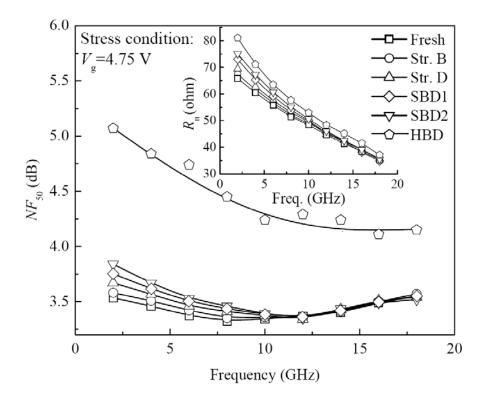

| Figure 5.9 $NF_{50}$ as a function of frequency measured at different stress                                                 |

| interruptions. Inset: comparison of noise resistance $(R_n)$ measured at                                                     |

| different stress interruptions including HBD82                                                                               |

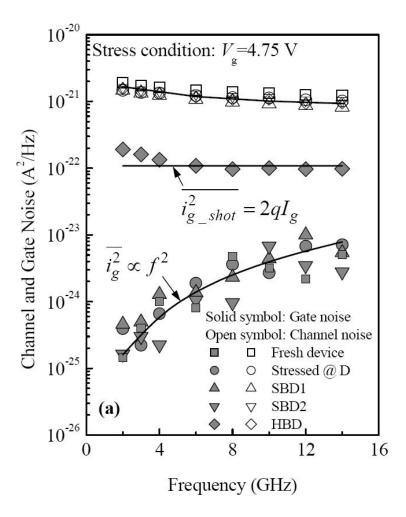

| Figure 5.10 Extracted drain (channel) thermal noise $i_d^2$ and gate noise                                                   |

| $\overline{i_g^2}$ for an NMOSFET at different stress stages85                                                               |

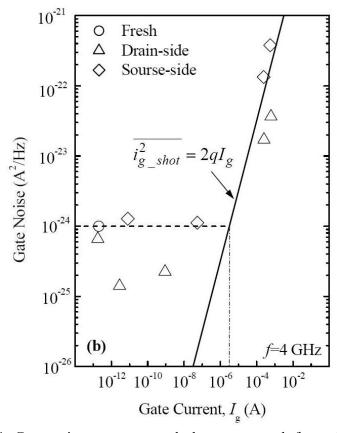

| Figure 5.11 Gate noise versus gate leakage extracted from devices with                                                       |

| different leakage levels (breakdown hardness) and breakdown                                                                  |

| locations. The stress voltage $V_{\rm g}$ is in the range of 4 to 5.3 V. The gate                                            |

| shot noise $\overline{i_{g-shot}^2} = 2qI_g$ is plotted in the figure for reference86                                        |

| Figure 6.1 Example of gate current versus time for a 5.3-V stress90                                                          |

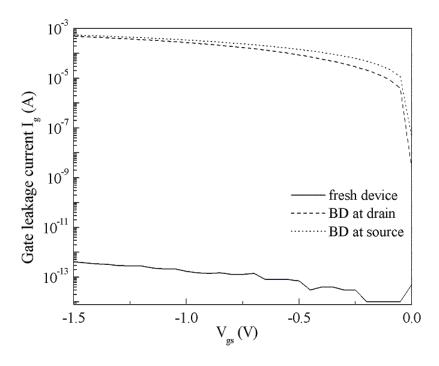

| Figure 6.2 Typical leakage current at gate for fresh and post-breakdown                                                      |

| devices. Gate-to-drain/source breakdowns shown in the figures93                                                              |

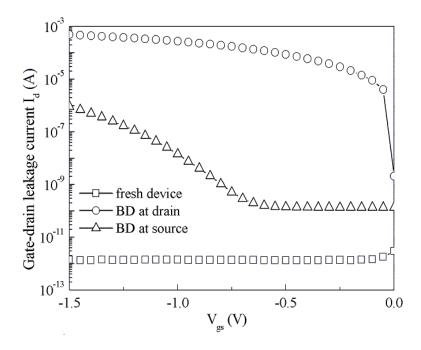

| Figure 6.3 Typical leakage current at drain for fresh and post-breakdown                                                     |

| devices93                                                                                                                    |

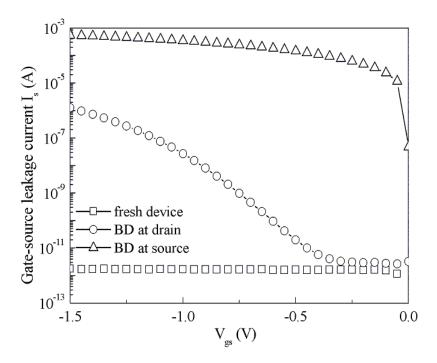

| Figure 6.4 Typical leakage current at source for fresh and post-breakdown                                                    |

| devices94                                                                                                                    |

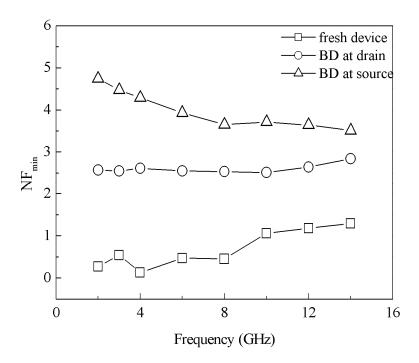

| Figure 6.5 De-embedded minimum noise figures ( $NF_{min}$ ) as a function of                                                 |

| frequency for fresh device and after drain/source breakdown with $V_{g}$                                                     |

| $= V_d = 1V$ 96                                                                                                              |

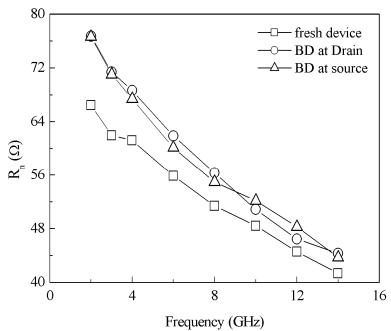

| Figure 6.6 Noise resistance $R_n$ as a function of frequency for fresh device                                                |

| and after drain/source breakdown with $V_g = V_d = 1V$ 98                                                                    |

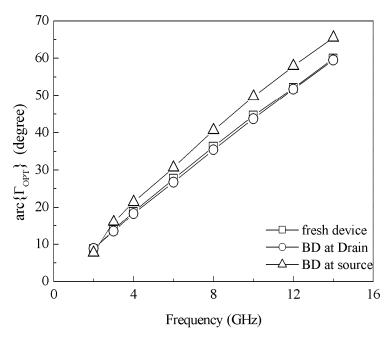

| Figure 6.7 Phase of optimum reflection coefficient $\Gamma_{opt}$ as a function of                                           |

| frequency for fresh device and after drain/source breakdown with $V_g$                                                       |

| $= V_d = 1V \dots 98$                                                                                                        |

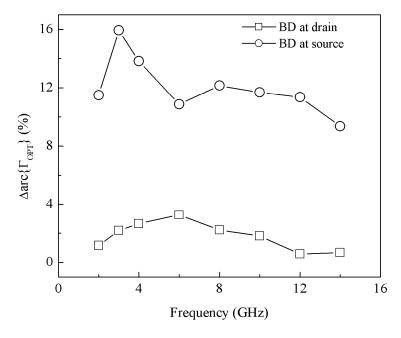

| Figure 6.8 Percentage of change of phase of $\Gamma_{opt}$ as a function of frequency                                        |

| before and after device breakdown at source and drain side99                                                                 |

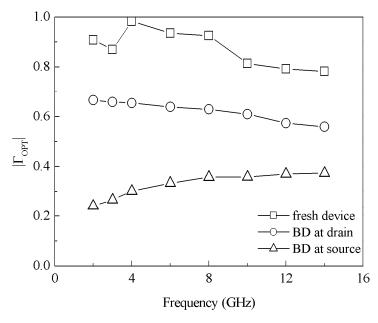

| Figure 6.9 Magnitude of optimum reflection coefficient $\Gamma_{opt}$ as a function of frequency for fresh device and after drain/source breakdown with $V_g$                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $= V_d = 1$ V                                                                                                                                                                                                                                                  |

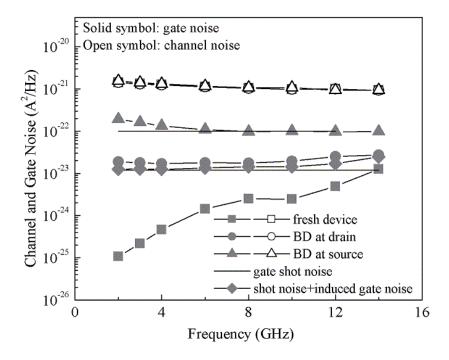

| Figure 6.11 Extracted drain (channel) thermal noise $\overline{i_d^2}$ and gate noise $\overline{i_g^2}$ for                                                                                                                                                   |

| the NMOSFETs with oxide breakdown at source and drain side. The gate shot noise $\frac{1}{i_{g\_shot}^2} = 2qI_g$ is plotted in the figure for reference103                                                                                                    |

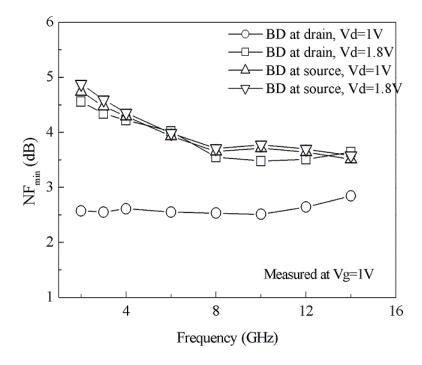

| Figure 6.12 De-embedded minimum noise figures ( $NF_{min}$ ) as a function of frequency for device after drain/source breakdown with $V_g = 1V$ and $V_d = 1V \& 1.8V$                                                                                         |

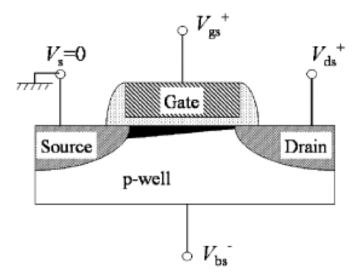

| Figure 7.1 Schematic representation of an NMOSFET under reverse body bias used in the experiments described in this study                                                                                                                                      |

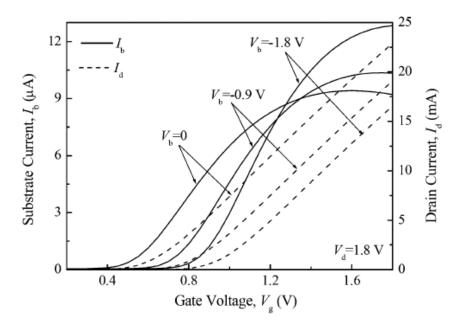

| Figure 7.2 Substrate $(I_b)$ and drain $(I_d)$ currents as functions of gate voltage $V_g$ with different substrate voltages $V_b$ as the parameter. The drain voltage $V_d$ is 1.8 V                                                                          |

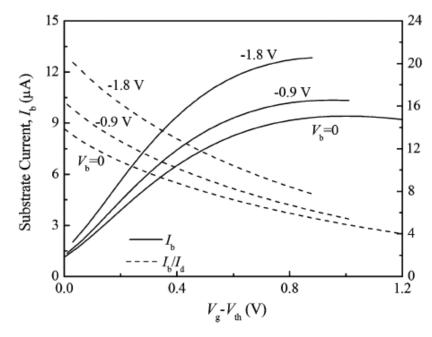

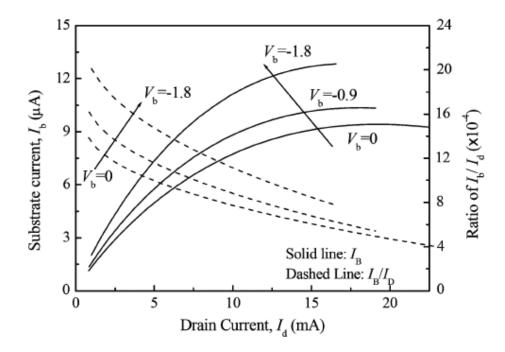

| Figure 7.3 Plot substrate current $I_b$ and ratio of $I_b/I_d$ versus $V_g - V_{th}$ 111 Figure 7.4 Plot substrate current $I_b$ and ratio of $I_b/I_d$ versus $I_d$ to exclude the body effect. The increase in $I_b$ and $I_b/I_d$ suggests the carrier heat |

| via negative body bias                                                                                                                                                                                                                                         |

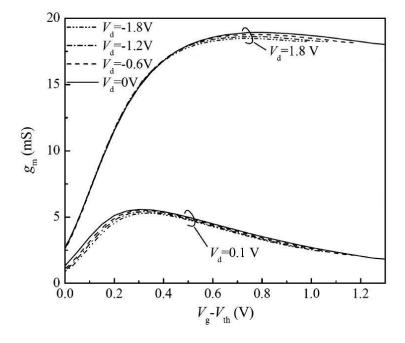

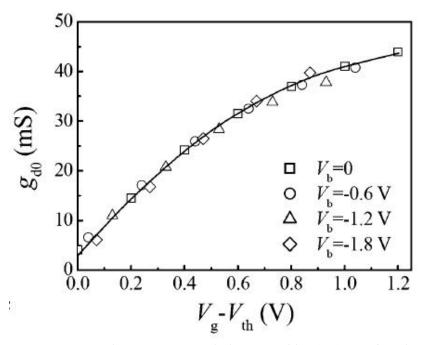

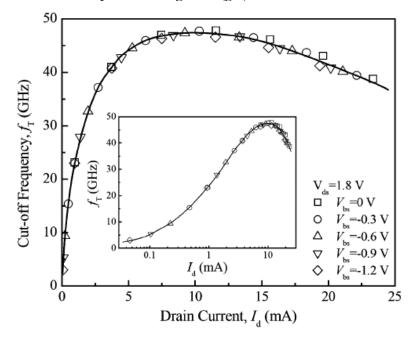

| $-V_{th}$ with different body bias                                                                                                                                                                                                                             |

| $V_b$                                                                                                                                                                                                                                                          |

| The $V_{ds}$ was set to 1.8 V during the measurements. Inset: Plot the same curve in a log scale of $I_d$ to illustrate the low $I_d$ region                                                                                                                   |

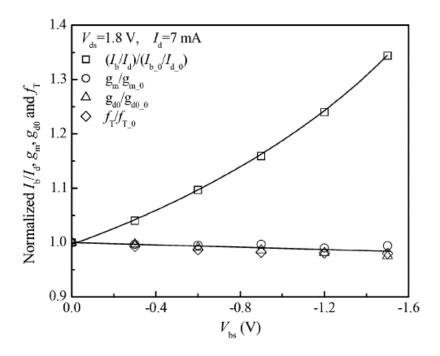

| increase in body bias. The increase in $ V_b $ results in drastic increase in the ratio of $I_b$ / $I_d$ with negligible impact on the other parameters114                                                                                                     |

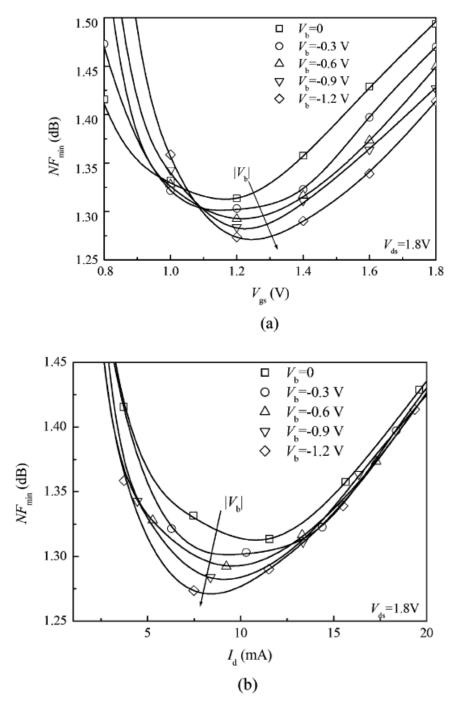

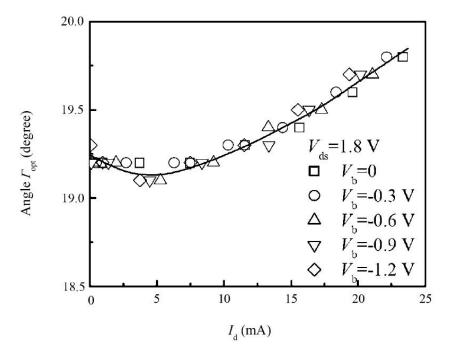

| Figure 7.9 Minimum noise figure $NF_{min}$ versus gate bias: (a) $V_{gs}$ and (b) drain current $I_d$ as function of body bias. A slight decrease in $NF_{min}$ with the increase of $ V_b $ is measured                                                       |

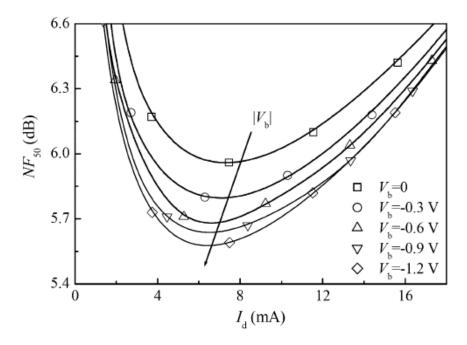

| Figure 7.10 Noise figure at 50- $\Omega$ generator impedance $NF_{5\theta}$ as a function drain current $I_d$ . Increase of $ V_b $ from 0 to 1.2 V results in ~0.4-dB reduction of $NF_{5\theta}$                                                             |

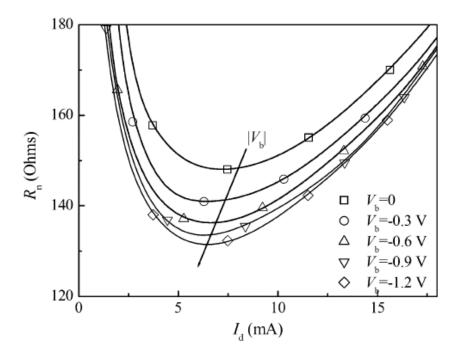

| Figure 7.11 Noise resistance $R_n$ versus drain current $I_d$ as a function of body bias $V_b$                                                                                                                                                                 |

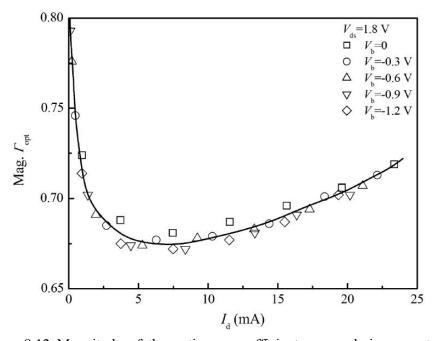

| Figure 7.12 Magnitude of the optimum coefficient versus drain current at 2 GHz as a function of body bias                                                                                                                                                      |

| as a function of body bias121                                                                                                                                                                                                                                  |

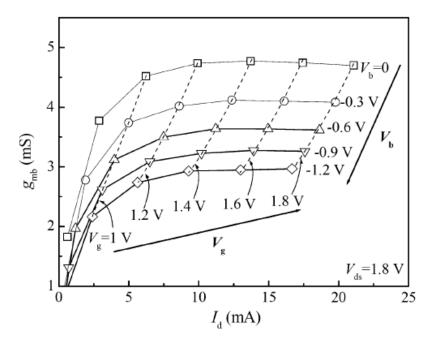

| Figure 7.14 Bulk transconductance ( $g_{ml}$    | b) as a function of $I_d$ for different $V_b$ . |

|-------------------------------------------------|-------------------------------------------------|

| Reduction of $g_{mb}$ from ~4.7 to 2.9 $n$      | $dS$ when $ V_b $ is increased from 0 to        |

| 1.2V                                            | 123                                             |

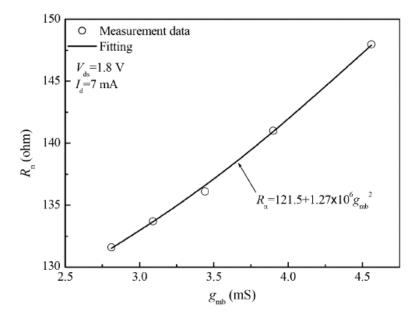

| Figure 7.15 Plotting $R_n$ versus $g_{mb}$ show | s a parabolic relation. The values              |

| $R_n$ and $g_{mb}$ were extracted from Fig      | gures 7.11 and Figure 7.14 at $I_d = 7$         |

| mA for different V <sub>b</sub>                 |                                                 |

#### **LIST of TABLES**

| Table 4.1 Typical drain and source resistances                             | 52 |

|----------------------------------------------------------------------------|----|

| Table 4.2 The Z-parameters and extracted $r_d$ and $r_s$ of two RF devices |    |

| Table 4.3 Extracted parameters from small signal equivalent circuits       | 57 |

| Table 5.1 Element values extracted for an operation point in saturation    | 75 |

#### **Chapter 2 Introduction**

#### 1.1 CMOS technology for RFIC applications

RF integrated circuits in CMOS (Complementary metal–oxide–semiconductor) technologies have a strong presence in the commercial world. For applications such as wireless Local Area Network (LAN) and Bluetooth, they are dominant, and in areas such as Global System for Mobile (GSM) cellular transceivers and Global Positioning System (GPS) receivers, they are making inroads. Driving force for this are advances in CMOS fabrications.

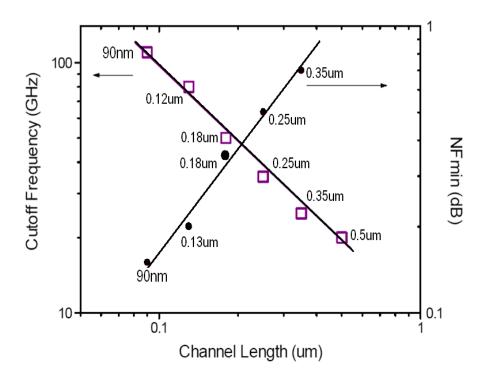

Modern CMOS technologies have resulted in deep submicron transistors with higher transit frequencies and lower noise figures. The cut-off frequency of NMOSFETs can be higher than 100Ghz at a channel length of 90nm, while the minimum noise figure can be as low as 0.1dB (Figure 1.1). This advanced performance of deep sub-micron MOSFETs is attractive for high-frequency (HF) integrated circuit (IC) design. Designers have already started to explore the use of CMOS technology in radio-frequency (RF) circuits. Furthermore, great advances in CMOS technology have made possible the development of system-on-a-chip design, where digital, mixed-signal base-band and HF transceiver blocks are integrated on a single chip. In addition, by eliminating expensive packaging and processing silicon wafers in high volume, cost can be greatly reduced. Other advantages like the low power consumption of MOSFETs make them suitable for portable applications.

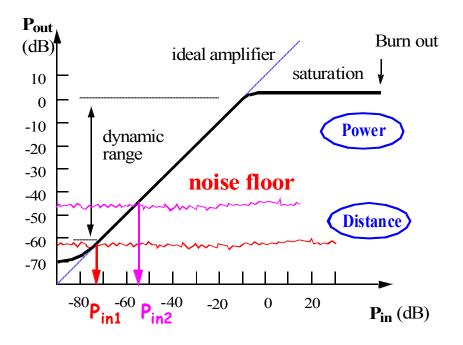

However, when transistors operate at high frequencies, noise generated within the device itself will play an increasingly important role in the overall sensitivity characteristics, dynamic range and signal-to-noise ratio of a system. Figure 1.2 shows a typical output curve of an amplifier. The minimum input power that can be recognized by the amplifier system is decided by the noise floor present in the system. The noise floor is the measure of the signal created from the sum of all the noise sources and unwanted signals within a measurement system. The lower the noise floor, the higher the sensitivity of the system is and the wider the dynamic range of the amplifier is. Low noise design is one of the key issues in most of the RF circuits. To reduce design cycles and to achieve first time success in implementation, acurate modelling of noise is a prerequisite.

A majority of the RF integrated circuits used in wireless systems are very sensitive to device parameter variations. In addition, compared to their long-channel counterparts, deep sub-micron MOSFETs are reported to have a strong enhancement in thermal noise. Lack of understanding of noise in deep submicron MOSFETs presents a substantial barrier to the modelling of MOSFETs and implementation of RF circuit design. It is indispensable to understand the physical phenomena of noise in deep sub-micron MOSFET and to incorporate this information into the models.

Figure 2.1 CMOS technology trend: cutoff frequency and NF<sub>min</sub> [1]

Figure 2.2 Typical power curve of an amplifier with different noise floors [2]

#### 1.2 Objectives

Thermal noise is a major source of noise in MOSFETs. Knowledge of the channel thermal noise and induced gate noise is required in most noise analysis and studies of MOSFETs, hence significant efforts have been made to extract them. Generally the procedure involves the extraction of small-signal parameters separately at each bias point followed by complex matrix computations. Part of the research work presented in this thesis is on methods to quickly calculate noise currents in deep-sub micrometer MOSFETs without the need to extract small-signal parameters.

To minimize the switching power dissipation of integrated circuits, the supply voltages have been steadily reduced as a result of scaling. In order to maintain performance and control short channel effects, a reduction in the transistor oxide thickness is required to provide sufficient current drive at the reduced supply voltages. At the 65nm technology node, CMOS processes will have oxide thicknesses of 1.2nm to 1.6nm. Since electric fields in the gate oxide are expected to rise with scaling, the long-term reliability of thin oxides becomes an important concern in modern, deep-submicron devices. The gate oxide wear-out and eventual breakdown is considered to be one of the major reliability issues for deep submicron MOSFETs. However, the effect of device degradation on the RF noise in NMOSFETs has not yet been fully addressed. In this work, the relationship between the MOSFET degradation and stress is discussed.

Several authors have shown that the most severe breakdowns are those located near the source/drain overlap regions [3]. The impact of the oxide breakdown on the device operation is thus controlled by two breakdown variables: the hardness and the location. It has been found that the drastic increase of device high frequency noise after gate oxide breakdown can be attributed to the significant increase in the contribution of gate shot noise. However, it was still unclear how hard breakdown in a sub-micron MOSFET can influence operation of low noise RF circuits. Part of the research work in this thesis is on the relation between the location of breakdown in deep sub-micron MOSFET and noise characteristics.

As compared to long channel devices, different RF noise behavior in deep-submicron MOSFET has been observed. Different theories have been proposed to explain these phenomena but many remain controversial. The mechanisms of noise currents in MOSFETs are not yet well understood. The experimental evaluation of the effect of carrier heating on channel noise in sub micrometer MOSFETs is carried out to gain a fundamental understanding of RF noise in NMOSFETs.

#### 1.3 Major contributions

The work described in this thesis was motivated by the desire to understand the mechanism of MOSFET noise and the impact of device degradation, such as gate oxide breakdown, on RF noise characteristics. The major contributions are summarized as follows:

5

Chapter 1: Introduction

(i) A new procedure is introduced to quickly evaluate the channel and induced gate noise currents in deep sub-micron MOSFET devices. The method only requires extracting the gate resistance. Noise parameters ( $NF_{min}$ ,  $R_n$ , and  $G_{opt}$ ) are measured and noise currents are then obtained using one simple matrix calculation, without the need to deduce additional device parameters. The extracted noise currents calculated with our method are comparable to those obtained using classic network matrix methods.

- (ii) The microwave noise performance of NMOSFET during FN stress and subsequent breakdown is studied. Degradation of high frequency noise characteristics in 0.18 μm NMOSFET induced by gate oxide breakdown is characterized in the frequency range of 2 to 14 GHz. Noise characteristics of the devices with different breakdown hardness are compared. A serious degradation of microwave noise performance is observed. The degradation mechanisms are analyzed by extraction of the channel and gate noise using a noise equivalent circuit model. It is found that gate shot noise, which is commonly ignored in the as-processed NMOSFET, plays a dominant role in determining the microwave noise performance in the post-oxide breakdown NMOSFET.

- (iii) The relationship between the breakdown location and RF noise degradation of deep sub-micron devices is addressed. The results for the dependence of device DC and high-frequency noise performance on breakdown location are provided. The results show the effect on degradation of noise

Chapter 1: Introduction

parameters from the gate leakage (breakdown hardness) and the breakdown location.

(iv) The impact of body bias on RF noise behavior in deep-sub micrometer NMOSFETs is investigated to understand if carrier heating and hot carrier effects are the root causes of the excess channel thermal noise observed in short-channel MOSFETs. Using a novel approach that modulates the channel carrier heating and the number of hot carriers through reverse body bias without causing significant changes to other device parameters, the postulation of enhancement of high-frequency noise in deep-sub micrometer MOSFETs due to channel carrier heating is directly assessed. We confirm qualitatively a negligible role of hot carrier effect on the channel noise in deep-sub micrometer MOSFETs. For a device under reverse body bias (Vb), even though the increase in hot carrier population is clearly characterized by dc measurements, the device high-frequency noise is found to be irrelevant to the increase in the channel hot carriers. Experimental results show that the high-frequency noise is slightly reduced with the increase in  $|V_b|$ , and can be qualitatively explained by secondary effects such as the suppression of non-equilibrium channel noise and substrate induced noise. The reduction of  $NF_{\min}$  and  $R_n$  with the increase in  $|V_b|$ may provide a possible methodology to finely adjust the device high-frequency noise performance for circuit design.

#### 1.4 Organization of this thesis

The following chapters provide extensive and detailed information about MOSFET noise both in terms of device physics and detailed modeling and analysis.

The theoretical background related to the device noise properties and device physics is investigated in Chapter 2. Small signal and noise modeling and parameter extraction method used in the research are presented. In addition a literature review is conducted. In Chapter 3, noise measurement methodology is addressed and the devices used in the research are introduced. A simplified noise currents extraction method is discussed in Chapter 4. In Chapter 5, effect of FN stress and gate oxide breakdown on high frequency noise is analyzed. In Chapter 6, the relation between RF noise and gate oxide breakdown location in deep sub-micron MOSFETs is examined. Carrier heating on channel noise in deep sub-micron NMOSFETs via body bias is studied in Chapter 7. Finally, in Chapter 8, the conclusion is presented and recommendations for future work are proposed.

#### **Chapter 3 Theoretical investigation of noise in**

#### **MOSFET** and device physics

#### 2.1 Small signal model of MOSFET

MOSFET models are widely used for modern electronic design work. There is a large economic incentive to get the design working without any iteration. Complete and accurate models allow a large percentage of designs to work the first time.

Small-signal or linear models are used to evaluate stability, gain, noise and bandwidth, etc. The small-signal condition for a transistor can be described as follows. A dc operating point is specified by a dc bias condition (i.e.  $V_{ds}$ ,  $V_{gs}$  and  $V_{bs}$ ), and small signals (ac signals) are superimposed to such a dc condition [4]. Under the small-signal condition, a MOSFET can be described by a small-signal equivalent circuit with lumped elements. The terminal voltages ( $V_{gs}$ ,  $V_{ds}$  and  $V_{bs}$ ) are assumed to change by a small amount. The resulting changes in currents are analyzed to derive the parameters for each path (gate-to-drain, gate-to-source, drain-to-source, etc.). The small signal equivalent circuit can be obtained by combining all the parameters together [5].

Different equivalent circuits have been proposed in the literature. Generally, two kinds of models are widely made use of: commercial MOS compact models such as BSIM4 [6], MOS model 9, 11 [7], or EKV (developed by C. C. Enz, F. Krummenacher, and E. A. Vittoz) [8] with or without

consideration of parasitic components; and the equivalent circuit derived from classical MESFET models (T-model or  $\pi$ -model). One crucial difference between these two kinds of models is the method to extract circuit elements values.

For the commercial compact model, a set of model equations are used to describe the behavior of the device. A simulation result is the evaluation of the equations given the values of the model parameters. The extraction of the model parameters is from the process of optimization. First, the initial model parameters are preset. The optimizer is used to adjust the initial model parameter values in an iterative process. The algorithm of the optimization process works follows:

1. The simulation goals are preset before the simulation and optimization. The simulation goals usually the RMS error between a set of measured parameters (for example: S-parameters, noise parameters) and the simulated parameters from the model.

$$RMSerror = \sqrt{\frac{\sum_{i=1}^{n} \left[ \left( sim_{i} - mea_{i} \right)^{2} / N \right]}{\left( \sum_{i=1}^{n} meas_{i}^{2} \right) / N}}$$

where:

$sim_i$  = the i<sup>th</sup> simulated data point;

$meas_i$  = the i<sup>th</sup> measured data point;

N =the total number of data points.

2. The optimizer invokes the simulator to obtain a set of simulated data

corresponding to the measured data used in the extraction process. This step is called function evaluation.

- 3. The optimizer compares the simulated and measured data and calculates the RMS error between them.

- 4. Based on the results, the optimizer calculates a new set of model parameter values and again compares the simulated and measured data. This process continues with another function evaluation until the RMS error between the simulated and measured data either falls within a specified range, or no further improvement is possible. Most of the extraction procedure is completed by the software. In most cases this is very time consuming.

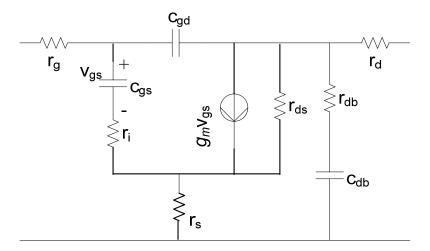

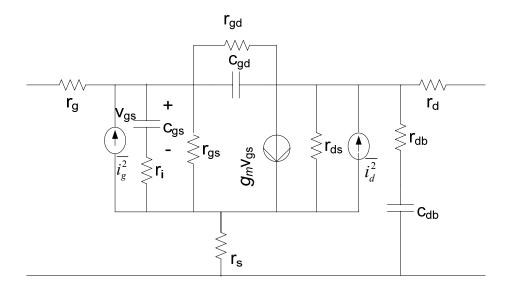

Figure 3.1 The equivalent high-frequency small-signal model for MOSFETs

As a counterpart, an equivalent circuit is comprised of a set of lumped circuit elements (R, L, C and current/voltage controlled current or voltage sources, etc.). The high frequency model used in this work is based on the

classical MESFET model proposed in [9]. Figure 2.1 shows the equivalent circuit for a grounded substrate MOSFET operating in the saturation region. In this model the circuit elements associated with the substrate and source are excluded because in the experiments as well as in most high-frequency applications the substrate is always effectively short-circuited to the source. When the excitation signal appears either at the drain or gate, the substrate spreading bulk resistance between the source and the substrate has a negligible effect in activating the substrate controlled current generator. The equivalent circuit can be divided into two parts:

- 1. the intrinsic elements,  $g_m$ ,  $r_{ds}$ ,  $C_{gs}$ ,  $C_{gd}$ ,  $r_i$ , which are functions of the biasing conditions;

- 2. the extrinsic elements,  $r_g$ ,  $r_s$ ,  $r_d$ ,  $r_{db}$ ,  $C_{db}$ , which are weakly dependent on the biasing conditions.

In this model,  $C_{gs}$  is the gate-to-source capacitance and  $C_{gd}$  is gate-to-drain capacitance. The bulk spreading resistance is designated as  $r_{db}$ , the drain-source resistance rds.  $g_m$  represents the device transconductance. The resistance  $r_i$  represents the effective channel resistance seen by the signal flowing from gate to source. It consists of the distributed resistance of the channel and spreading bulk resistance capacitively coupled to the channel, and is responsible for the real part of intrinsic input y-parameter. This element is important to input impedance matching in analogue circuit designs. The  $r_d$ ,  $r_s$ ,  $r_g$  are respectively the drain-to-channel resistance (including contact resistance),

source-to-channel resistance (including contact resistance) and gate-metal resistance.

By taking y-parameters of the equivalent circuit in the linear region, the extracted terminal resistances  $(r_d, r_s, r_g)$  for  $V_{ds}$ =0 V are: [10]

$$r_{g} = \left| \frac{\text{Re}\{Y_{12}\}}{\text{Im}\{Y_{11}\} \text{Im}\{Y_{12}\}} \right|$$

$$r_{d} = \left| \frac{\text{Re}\{Y_{21}\} - \text{Re}\{Y_{12}\}}{\text{Im}\{Y_{12}\}^{2}} \right| ,$$

$$r_{s} = \left| \frac{\text{Re}\{Y_{11}\}}{\text{Im}\{Y_{11}\}^{2}} - r_{g} - \frac{C_{gd}^{2}}{C_{gg}^{2}} r_{d} \right| \frac{C_{gg}^{2}}{C_{gs}^{2}}$$

(2.1)

where  $Y_{\square}$  are the y-parameters of the equivalent circuit, Re  $\{\}$  and Im  $\{\}$  denote for the real and imaginary part of the matrix elements,  $C_{gg}$  is the total gate capacitance and is given by:

$$C_{gg} = \left| \frac{\text{Im}(Y_{11})}{\omega} \right|. \tag{2.2}$$

In most of the MOS transistor applications at RF, the transistor is biased in the saturation region in order to achieve higher voltage gain and a larger dynamic range. The rest of the parameters will be extracted from the y-parameters in the saturation region. Since only the imaginary parts are needed for determining the intrinsic capacitances, the extraction method for  $C_{gg}$  can also be applied to the saturation region [8].  $C_{gs}$  and  $C_{gd}$  can be determined from the y-parameters in the saturation region:

$$C_{gd} = \left| \frac{\text{Im}(Y_{12})}{\omega} \right| .$$

$$C_{gs} = C_{gg} - C_{gd}$$

(2.3)

To extract the equivalent admittance of the substrate coupling network, the series resistances  $r_g$  and  $r_d$  are subtracted from input and output ports followed by transforming the Z-matrix into the Y-matrix. Thus:

$$Y' = (Z')^{-1} = (Z + \begin{bmatrix} r_g & 0 \\ 0 & r_d \end{bmatrix})^{-1}, \tag{2.4}$$

where Z is the Z-parameter matrix of the whole device in the saturation region.

The equivalent substrate admittance  $Y_{\text{sub}}$  is derived as

$$Y_{sub} = \frac{1}{r_{db} + \frac{1}{j\omega C_{db}}} = Y_{22} - j\omega C_{gd} - g_{ds}.$$

(2.5)

Here  $g_{ds}$  is extracted from the value of  $(\frac{1}{\text{Re}(Y_{22})} - r_s)^{-1}$  at low frequency («1 GHz).

#### 2.2 Sources of noise

#### 2.2.1 Definition of noise

The general definition of noise is "loud, confused, or senseless shouting or outcry" or "any sound that is undesired or interferes with one's hearing of something" [11]. In electronics, noise is usually referred to as an opposite term to the signal. Thus noise can be defined as "everything except for the desired signal" [12]. Several types of noise sources are observed in electron devices, such as thermal, shot, generation-recombination, and flicker noise. A MOSFET mainly contains three noise types: thermal noise, flicker noise and shot noise.

#### 2.2.2 Thermal noise

The random thermal motion of electrons inside a piece of conductive material leads to a temporary agglomeration of carriers at one of the ends of the material. From a macroscopic standpoint this means that the potential on one end will be more negative than the potential on the other end. Hence a potential difference appears, the thermal noise voltage. While its mean value is zero, its polarity and magnitude are fluctuating.

#### 2.2.3 Thermal noise in electron devices

At any temperature above absolute 0 K, the motion of the electrons will produce random instantaneous currents. These currents will produce random instantaneous voltages, and this leads to noise power. The random fluctuation of electrons in a resistance rises as the temperature increases. This is because the electron velocities and the frequency of collisions increase with higher temperatures. The noise voltage is expressed as an auto correlation of the instantaneous voltage over a time period T [13]:

$$\langle v^2 \rangle = \lim_{T \to \infty} \frac{1}{2T} \int_{-T}^T v^2(t) dt . \tag{2.6}$$

Nyquist's theorem [14] states that for linear resistances in thermal equilibrium at temperature T, the current of voltage fluctuations are quite independent of the conduction mechanisms, type of material, and shape and geometry of the resistor. The generated noise depends exclusively upon the value of the resistance and its temperature T (given in Kelvins [15]).

Therefore, under open-circuit conditions the noise voltage spectral density is a constant quantity given by [13]

$$S_{v_n} = \frac{\overline{v_n^2}}{\Delta f} = 4kTR$$

(V<sup>2</sup>/Hz). (2.7)

Under short-circuit condition, the noise current spectral density is a constant quantity, given by [13]

$$S_{i_n} = \frac{\overline{i_n^2}}{\Delta f} = \frac{4kT}{R} = 4kTG$$

(A<sup>2</sup>/Hz), (2.8)

where G denotes the conductance and k is Boltzmann's constant.  $\Delta f$  is the bandwidth within which the noise is measured.

#### **2.2.4** Thermal noise in MOSFETs

Historically MOS devices have been used for low frequency applications due to the limited carrier mobility of silicon. Consequently, the most important noise source was channel thermal noise and flicker noise. At high frequencies, channel thermal noise is still the key noise source. In addition other thermal noise sources, such as induced gate noise and parasitic resistance thermal noise become important.

Commonly sources of high frequency noise are classified as intrinsic and extrinsic. The noise originating within the active region of a MOS device channel is defined as intrinsic noise. It includes channel thermal noise and induced gate noise. Channel thermal noise is associated with carriers within the channel. According to Nyquist's theorem and the gradual channel

approximation, the short circuit thermal noise current at drain terminal  $\overline{i_d^2}$  is given by [16]

$$\overline{i_d^2} = 4kT\gamma g_{d0}\Delta f , \qquad (2.9)$$

where k is the Boltzmann constant, T is the absolute temperature, and  $g_{d\theta}$  is the channel conductance at zero drain source voltage.  $\gamma$  is a bias dependent factor. For long channel devices, the value of 2/3 holds when the MOSFET is in the saturation region, and the value of 1 is valid in the linear region [16]. This model agrees well with long channel MOSFETs down to 1.7  $\mu$  m. Substantial increases have been observed in  $\gamma$  for MOSFETs with shorter channel lengths owing to both velocity saturation and hot electrons. A simple thermal noise model has been proposed to account for these two effects by [103]

$$\gamma \cong \gamma_L (1 + \frac{1}{G} \frac{v_{sal} \tau_f}{L_{eff}}) \tag{2.10}$$

where  $v_{sat}$  is the saturation velocity,  $\tau_f$  is a relaxation time (of the order of ps) used as a fitting parameter, G is the normalized  $G_m/I_D$  ratio, and  $\gamma_L$  is the  $\gamma$ -factor for the long-channel device. This noise model assumes that the carrier velocity is saturated and that the lateral field is equal to the critical field all along the channel from source to drain. These assumptions are questionable, but it can cover device operation regions from weak to strong inversions and fit the measured data over different biases and geometries.

Induced gate noise is another type of intrinsic noise. At moderately higher frequencies, the random motion of the free carriers in the channel

generates not only an output drain current noise, but also an input gate current noise due to the capacitive coupling effect via the gate-channel capacitance.

The gate current noise is approximately given by [17]

$$\overline{i_g^2} = 4kT\beta \frac{(\omega C_{gs})^2}{g_{d0}} \Delta f, \qquad (2.11)$$

where  $C_{gs}$  is the gate-source capacitance of the MOSFET. Similar to factor  $\gamma$ ,  $\beta$  is also dependent on basic transistor parameters and bias conditions. It is equal to 4/3 for a long-channel device in saturation. Since induced gate noise also originates from the random motion of the carriers in the channel, the two noise currents  $\overline{i_d^2}$  and  $\overline{i_g^2}$  are correlated and the correlation can be described by [16]

$$c = \frac{\overline{i_g i_d^*}}{\sqrt{\overline{i_g^2} \cdot \overline{i_d^2}}}, \qquad (2.12)$$

where *c* is the correlation factor.

Aside from the intrinsic noise sources, various parasitic elements will contribute to the overall noise measured at the terminals of the devices at high frequencies. These types of noise source elements are classified as extrinsic noise sources.

MOSFET poly gate resistivity is usually very large. Even though a silicide process is normally adopted to form the gate, reducing the gate resistance becomes more difficult when the gate length is further. The resistive gate contributes to thermal noise at the gate node. The mean-square noise current of the gate resistance is described by [16]

$$\overline{i_G^2} = 4kT\Delta f / r_g, \qquad (2.13)$$

where  $\overline{i_g^2}$  represents the current noise source of gate resistance, and  $r_g$  is the effective noise resistance of the gate. Because of the distributed effect of gate resistance,  $r_g$  is given by [16]

$$r_g = \frac{R_{g-sh}}{3} \left(\frac{W_g}{L_g}\right),\tag{2.14}$$

where  $R_{g-sh}$  is gate sheet resistance,  $W_g$  is the width of the gate, and  $L_g$  is the gate length. Equation (2.12) is only valid when the gate is connected at one end.

The source and drain parasitic resistors also contribute to thermal noise.

These noise contributions are modeled by the following equations: [16]

$$\frac{\overline{i_s^2} = 4kT\Delta f / r_s}{\overline{i_D^2} = 4kT\Delta f / r_d},$$

(2.15)

where  $\overline{i_s^2}$  and  $\overline{i_D^2}$  represent the current noises of source and drain resistances. The noises generated by the source and drain resistances are also important. However, they are a strong function of the materials used to form the source/drain as well as processing. If not designed properly, their contribution to the noise figure of the whole device can be significant.

It is known that distributed substrate resistance is another noise source [18]. An accurate calculation of this noise source is complex, whereas it can be simply expressed as [16]

$$\overline{i_{dB}^2} = 4kT\alpha \frac{d}{W}g_{mb}^2 \Delta f \tag{2.16}$$

where  $\alpha$  is a constant, d is the space size between gate and bulk contact, W is the gate width, and  $g_{mb}$  is the bulk transconductance which depends on the bulk to source voltage  $V_{BS}$ .

#### 2.2.5 Shot noise

Shot noise was first described by Schottky in 1918 [19] as:

$$\langle i^2 \rangle = 2qI_0 \Delta f \,, \tag{2.17}$$

where  $I_0$  is the DC current flowing across the device and q is the charge of an electron. It is white noise and occurs when quantized carriers cross barriers with random spacing as in Schottky diodes or p-n junctions.

The arrival of one unit charge at a boundary is independent from the time at which the previous unit arrived or the next unit will arrive. Therefore, two conditions are required for shot noise to occur: a flow of direct current and a potential barrier over which the carriers are crossing. Thus linear devices do not generate shot noise.

The only source of shot noise in a MOSFET is associated with the current tunnelling through the gate oxide, which is negligible in most cases.

#### 2.2.6 Flicker noise

In principle, flicker noise is a low-frequency noise and it mainly affects the low frequency performance of the device, so it can be ignored at very high frequency. However, the contribution of flicker noise should be considered in designing some radiofrequency (RF) circuits such as mixers, oscillators, or frequency dividers that up-convert the low-frequency noise to higher frequency and deteriorate the phase noise or the signal-to-noise ratio. Typically this frequency ranges from 100 Hz to 10 kHz.

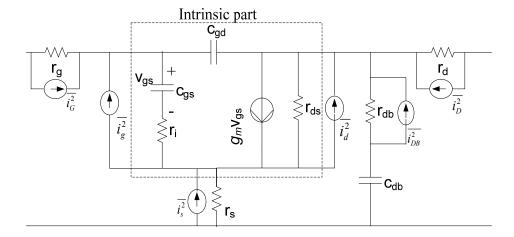

#### 2.2.7 Equivalent noise circuit model

From the above analysis, thermal noise is the major contributor for the origin of high-frequency noise in the MOSFET drain current. After including all the thermal noise sources into the small signal model in Figure 2.1, Figure 2.2 shows the small-signal equivalent noise circuit of the grounded substrate MOSFET.

Figure 3.2 small-signal equivalent noise circuit of grounded substrate MOSFET

#### 2.3 Noise parameters and noise two-port network

A noisy two-port may be described by a noise-free two-port and two current noise sources in three different representations as shown in Figure 2.3. These two noise sources are usually correlated with each other.

A matrix formulation for the representation  $C_Y$  in Figure 2.3(a) is given by [21]:

$$C_{Y} = \frac{1}{2\Delta f} \begin{bmatrix} \langle i_{1}i_{1}^{*} \rangle & \langle i_{1}i_{2}^{*} \rangle \\ \langle i_{2}i_{1}^{*} \rangle & \langle i_{2}i_{2}^{*} \rangle \end{bmatrix}. \tag{2.18}$$

Figure 3.3 Different representations of a noisy two-port network [20]

Based on the *Y*-parameters of the two-port and the noise source information ( $i_1$ ,  $i_2$  and their correlation term  $\langle i_1 i_2^* \rangle$ ), we may evaluate the noise parameters of the two-port by transforming the noisy two-port to a noise-free two-port with a noise current and a noise voltage sources at the input side of the two-port (Figure 2.3(b)). The correlation matrix  $C_A$  is given by [21]:

$$C_{A} = \frac{1}{2\Delta f} \begin{bmatrix} \langle uu^{*} \rangle & \langle ui^{*} \rangle \\ \langle iu^{*} \rangle & \langle ii^{*} \rangle \end{bmatrix}. \tag{2.19}$$

The correlation matrix  $C_Z$  of the impedance representation in Figure 2.3(c) is given by [21]:

$$C_Z = \frac{1}{2\Delta f} \begin{bmatrix} \langle u_1 u_1^* \rangle & \langle u_1 u_2^* \rangle \\ \langle u_2 u_1^* \rangle & \langle u_2 u_2^* \rangle \end{bmatrix}. \tag{2.20}$$

The three representations can be transformed into each other by simple transformation operations.  $C_A$  and  $C_Y$  are correlated by equation [21]:

$$C_{\nu} = T_{\nu} C_{\mu} T_{\nu}^{\dagger}, \tag{2.21}$$

where the † in  $T_Y^{\dagger}$  denotes Hermitian conjugation (transpose and complex conjugate) and the transformation matrix  $T_Y$  is given by [21]

$$T_{Y} = \begin{bmatrix} -Y_{11} & 1 \\ -Y_{21} & 0 \end{bmatrix}, \tag{2.22}$$

where  $Y_{II}$  and  $Y_{2I}$  are Y-parameters of the two-port network. A set of matrices covering all possible transformations can be found in [21].

For applications in noise analysis, interconnections of two two-ports either in parallel, in series or in cascade are of particular interest. The resulting correlation matrices can be determined by [21]

$$C_Y = C_{Y1} + C_{Y2}$$

(parallel)

$C_Z = C_{Z1} + C_{Z2}$  (Series) (2.23)

$C_A = A_1 C_{A2} A_1^+ + C_{A1}$  (Cascade)

Any network A can be decomposed into a few basic two-ports. These basic two-port networks then consist of only a few elements and the noise currents and electrical matrices ( $C_A$ ,  $C_Z$  or  $C_Y$ ) of each element are easily

calculated or measured. Once all matrices are known, the basic two-ports are successively interconnected so that network A is obtained. As an example, in the equivalent circuit in Figure 2.2, the network can be divided into five basic two-ports: intrinsic part, gate resistance, source resistance, substrate network and drain resistance. The matrices of the parasitic elements (gate/source/drain resistance and substrate network) can be calculated. With knowledge of the intrinsic noise currents, the noises currents of the whole equivalent circuit can be calculated by the above direct matrix analysis or vice versa.

The noise power spectral density is widely used in noise modelling and circuit design as a measure for the noise output in a device. However, in measurements, the RF noise is usually characterized by several other parameters: the minimum noise factor (or minimum noise figure), the input referred noise resistance and the optimum source admittance at which the minimum noise figure is obtained. It is necessary to connect these parameters with the RF noise characteristics of the device.

Noise figure (NF) is a measure of degradation of the signal to noise ratio. It has been defined in a number of different ways. The most commonly accepted definition is

Noise figure

$$(NF) = \frac{SNR_{in}}{SNR_{out}}$$

, (2.24)

where  $SNR_{in}$  and  $SNR_{out}$  are the signal-to-noise ratios measured at the input and output, respectively. It is also called the noise factor with the term noise figure applied to  $10log_{10}$  (noise factor).

The noise figure is a measure of how much the SNR degrades as the signal passes through a system. If a system has no noise, then  $SNR_{out}$ = $SNR_{in}$ , regardless of the gain. This is because both the input signal and the input noise are amplified or attenuated by the same factor and no additional noise is introduced. Therefore the noise figure of a noiseless system is equal to 1. On the other hand a noisy system degrades the SNR, yielding NF>1. A low noise figure means that very little noise is added by the network. The concept of noise figure only fits networks (with at least one input and one output port) that process signals.

The noise figure of a two-port network is given by [20]

$$NF = NF_{\min} + \frac{R_n}{G_s} [(G_s - G_{opt})^2 + (B_s - B_{opt})^2,$$

(2.25)

where  $G_s$  is the source conductance,  $B_s$  is the source susceptance,  $G_{opt}$  is the optimized source conductance,  $B_{opt}$  is the optimized source susceptance. From (2.23), it is shown that the four noise parameters – the minimum noise figure  $(NF_{min})$ , the optimum source (input) impedance for the  $NF_{min}$ , and the equivalent noise resistance  $(R_n)$  which characterizes how the noise figure increases if the source impedance deviates from the optimum value – will decide how noisy a two-port network will be.  $NF_{min}$ ,  $R_n$ , and  $G_{opt}$  are frequently referred to as the "noise parameters", and it is their determination which is called "noise characterization". When  $G_s$  is plotted on a Smith chart for a set of constant noise factors NF, the results are "noise circles" (Figure 2.4). Noise

circles are a convenient format to display the complex relation between source impedance and noise figure.

Figure 3.4 Noise circles of a typical transistor. The noise circles are used to display the complex relation between source impedance and noise figure.

The correlation matrix  $C_A$  can be calculated from the four measured noise parameters [20]:

$$C_{A} = \begin{pmatrix} R_{n} & \frac{F_{\min} - 1}{2} - R_{n} \cdot Y_{opt}^{*} \\ \frac{F_{\min} - 1}{2} - R_{n} Y_{opt} & R_{n} |Y_{opt}|^{2} \end{pmatrix}, \tag{2.26}$$

where the asterisk denotes the complex conjugate.

# 2.4 Extraction of noise parameters

The induced gate noise, channel noise, and their correlation in MOSFETs can be extracted by using the following steps from measured noise parameters ( $NF_{min}$ ,  $R_n$ , and  $G_{opt}$ )[22].

1). Calculate the correlation matrix  $C_{Adev}$  of the intrinsic device from measured noise parameters of the device [22]

$$C_{Adev} = \begin{bmatrix} R_{n,dev} & \frac{NF_{\min,dev} - 1}{2} - R_{n,dev} (Y_{opt,dev})^* \\ \frac{NF_{\min,dev} - 1}{2} - R_{n,dev} (Y_{opt,dev}) & R_{n,dev} |Y_{opt,dev}|^2 \end{bmatrix}.$$

(2.27)

2). Calculate the four-port admittance matrix  $Y_{extr}$  of the extrinsic part in the RF transistor model by excluding  $C_{GS}$ ,  $C_{GD}$ ,  $g_m$ ,  $R_{DS}$ , and  $R_i$  [23]

$$Y_{extr} = \begin{bmatrix} Y_{ee} & Y_{ei} \\ Y_{ie} & Y_{ii} \end{bmatrix}, \tag{2.28}$$

where the submatrixes  $Y_{ee}$ ,  $Y_{ei}$ ,  $Y_{ie}$ , and  $Y_{ii}$  are  $2\times 2$  matrixes.

- 3). Calculate the two-port admittance  $Y_{intr}$  of the intrinsic part in the RF transistor model.

- 4). Calculate a matrix **D** as follows [22]:

$$D = -Y_{ei}(Y_{ii} + Y_{intr})^{-1}. (2.29)$$

5). Convert the noise correlation matrix  $C_{Adev}$  to its admittance form  $C_{Ydev}$  by using [22]

$$C_{Ydev} = T_Y C_{Adev} T_Y^{\dagger}. \tag{2.30}$$

where the † in  $T_Y^{\dagger}$  denotes Hermitian conjugation (transpose and complex conjugate) and the transformation matrix  $T_Y$  is given by

$$T_{Y} = \begin{bmatrix} -Y_{11,dev} & 1\\ -Y_{21,dev} & 0 \end{bmatrix}. \tag{2.31}$$

6). Calculate the admittance noise correlation matrix  $C_{Yextr}$  of the extrinsic part by [24]

$$C_{Yextr} = kT(Y_{extr} + Y_{extr}^{\dagger})$$

$$Or C_{Yextr} = 2kT\Re(Y_{extr}),$$

(2.32)

where T is the device temperature,  $\Re()$  denotes for the real part of the matrix elements and partition  $C_{Yextr}$  as [22]

$$C_{Yextr} = \begin{bmatrix} C_{ee} & C_{ei} \\ C_{ie} & C_{ii} \end{bmatrix},$$

where the submatrixes  $C_{ee}$ ,  $C_{ei}$ ,  $C_{ie}$ , and  $C_{ii}$  are 2×2 matrixes.

7). Calculate the admittance correlation matrix  $C_{Yintr}$  of the intrinsic part in the RF transistor model from [22]

$$C_{Y_{\text{int}r}} = D_i (C_{Y_{dev}} - C_{ee}) D_i^{\dagger} - C_{ie} D_i^{\dagger} - D_i C_{ei} - C_{ii}, \qquad (2.33)$$

where  $D_i = D^{-1}$ .

8). Convert  $Y_{intr}$  to its chain representation  $A_{intr}$  using the conversion formula [22]:

$$A_{\text{int}r} = \frac{-1}{Y_{21,\text{int}r}} \begin{bmatrix} Y_{22,\text{int}r} & 1\\ Y_{11,\text{int}r} Y_{22,\text{int}r} - Y_{12,\text{int}r} Y_{21,\text{int}r} & Y_{11,\text{int}r} \end{bmatrix},$$

(2.34)

9). Convert  $C_{Yintr}$  to its chain matrix form  $C_{Aintr}$  by using [22]

$$C_{A \text{int} r} = T_A C_{Y \text{int} r} T_A^{\dagger}, \tag{2.35}$$

where  $T_A$  is given by

$$T_A = \begin{bmatrix} 0 & A_{12,\text{int}\,r} \\ 1 & A_{22,\text{int}\,r} \end{bmatrix}. \tag{2.36}$$

10). Calculate the noise parameters  $NF_{min}$ ,  $Y_{opt}$ , and  $R_n$  of the intrinsic part in the RF transistor model from the noise correlation matrix  $C_{Aintr}$  by using (2.35), where  $\Im$ () stands for the imaginary part of elements and j is the imaginary unit [22].

$$NF_{\min} = 1 + \frac{1}{kT_0} (\Re(C_{12A, \text{int } r} + \sqrt{C_{11A, \text{int } r} C_{22A, \text{int } r} - (\Im(C_{12A, \text{int } r}))^2})$$

$$Y_{opt} = \frac{\sqrt{C_{11A,intr}C_{22A,intr} - (\Im(C_{12A,intr}))^2} + j\Im(C_{12A,intr})}{C_{11A,intr}}$$

And

$$R_n = \frac{C_{11A,\text{int}r}}{2kT_0} \,. \tag{2.37}$$

11). Calculate the power spectral density of the channel noise  $\overline{i_d^2}$ , induced gate noise  $\overline{i_g^2}$ , and their correlation  $\overline{i_g i_d^*}$  from [22]

$$\frac{\left|i_{d}\right|^{2}}{\Delta f} = 4kT_{0}R_{n}\left|Y_{21,\text{int }r}\right|^{2} \tag{2.38}$$

$$\frac{\left|\bar{l}_{g}\right|^{2}}{\Lambda f} = 4kT_{0}R_{n} \times \left\{\left|Y_{opt}\right|^{2} - \left|Y_{11,\text{int }r}\right|^{2} + 2\Re\left[\left(Y_{11,\text{int }r} - Y_{cor}\right)Y_{11,\text{int }r}^{*}\right]\right\}$$

(2.39)

And

$$\frac{\overline{i_g i_d^*}}{\Delta f} = 4kT_0 (Y_{11, \text{int } r} - Y_{cor}) R_n Y_{21, \text{int } r}^*$$

(2.40)

where  $Y_{cor}$  is given by

$$Y_{cor} = \frac{NF_{\min} - 1}{2R_{in}} - Y_{cor} \tag{2.41}$$

# 2.5 Gate oxide breakdown

#### 2.5.1 Gate oxide breakdown and noise

Gate-oxide breakdown is defined as the time when a cluster of connected bonds, beginning from a "seed" at one interface of the gate-oxide, reaches the opposite interface [25]. Defects within the gate oxide are usually called traps. Gate-oxide breakdown begins when traps form in the gate-oxide. At first the traps are non-overlapping and thus do not conduct, but as more and more traps are created in the gate-oxide, traps start to overlap creating a conduction path [26]. Once these traps form a conduction path from the gate to the channel, breakdown occurs [26]. This type of breakdown is called Soft Breakdown (SBD). Once there is conduction, new traps are created by thermal damage, which in turn allows for increased conductance [27]. The cycle of conduction leading to increased heat and increased heat leading to increased conduction leads to thermal runaway [27] and finally to a lateral propagation of the breakdown spot [28]. The silicon within the breakdown spot starts to melt,

and oxygen is released, and a silicon filament is formed in the breakdown spot [27]. This type of breakdown is called Hard Breakdown (HBD).

Figure 3.5 Measured cut-off frequency degradation versus stress time [34]

Figure 3.6 Noise figure versus frequency before and after stress [34]

The gate oxide wear-out and eventual breakdown is considered as one of the major reliability issues for deep-sub micrometer MOSFETs [29]. The impact of gate oxide breakdown on device I-V characteristics has been the subject of numerous studies over the past few decades. Oxide breakdown in the devices with relatively thick (>10 nm) oxides used in earlier technologies normally results in a catastrophic failure of the circuit after SBD or HBD. In [38], it has been shown that even soft breakdown can produce a strong decrease of the drain current and transconductance in MOSFETs with small W. This is due to the formation of a localized oxide damaged region likely trapping negative charge over a large portion of the channel width, around the soft breakdown conductive path. However, recent studies on advanced devices with thin gate oxide reveal that the oxide breakdown does not cause the device to fail destructively, and the circuit may still continue to function properly after breakdown [30, 31, 36]. In some cases, even if a hard breakdown (HBD) has occurred, this may not necessarily cause a failure of the circuit. In [106], it was found that a region of the channel surrounding the breakdown spot is physically damaged by the high current and can no longer carry current from drain to source. The radius of the damaged region can be evaluated between 1.4 and 1.8 μm. This result shows that devices having large W/L ratio can be still operative after breakdown. Hence, if the functioning of the circuit is chosen as the only reliability criterion, then it may be possible to relax oxide reliability requirements [36].

On the other hand, the improved high frequency performance of deep submicron MOSFETs in conjunction with the capability of very large scale integration (VLSI) provides a great opportunity to use Si MOSFET for low noise radio frequency integrated circuits (RFICs) or microwave monolithic integrated circuits (MMICs). The impact of gate oxide breakdown on the RF characteristics of NMOSFET has attracted some attention [32, 33, 34]. It has been shown that the cut-off frequency and noise factors are degraded after stress (Figure 2.5 and 2.6). 1/f noise level in the MOSFET clearly increases after gate oxide breakdown. It is said that holes injected in the oxide can be a dominant source of the noise degradation [107]. Recently it has suggested that NMOSFETs noise at 2 GHz may not be thermal in origin. [35]

# 2.5.2 Gate oxide breakdown and location

The results of HBD and SBD are quite different, and thus they will manifest themselves differently when they occur in transistors will thus be dealt with separately.

Figure 3.7 Effective gate post breakdown resistance as a function of the breakdown spot location along the channel in three short-channel NMOSFETs [29]

After HBD has occurred, there is a current path from the gate to the channel. The current path is generally characterized by a gate post-breakdown resistance defined as  $R_{eff} = V_G/I_G$  [36]. The current through the gate is orders of magnitude larger than before breakdown. Thus to characterize the effects of HBD it becomes important to be able to find  $R_{eff}$ . In [20], the authors show that  $R_{eff}$  is dependent on the position of the breakdown along the length of the transistor. For a  $0.2\mu m$  long transistor the post-breakdown resistance versus the position of the breakdown is shown in Figure 2.7. In regions in which the breakdown occurs over the source and drain extensions,  $R_{eff}$  increases linearly. Otherwise, if the breakdown occurs over the channel,  $R_{eff}$  is relatively constant. The linear increase in  $R_{eff}$  over the source/drain extensions is due to the resistance of the length of the n-doped region in the extension where the

breakdown occurred. When the breakdown happens over the channel, it is as if current is injected from the gate through the breakdown path into the channel which then continues to the drain and the source. Regarding the magnitude of the current, it has been shown that after HBD near the source or drain, there is an increase of two orders of magnitude when the transistor is on, and an increase of six orders of magnitude when the gate voltage is near 0V [26]. In addition, increases of gate current of many orders of magnitudes, depending on the state of the transistor, have been observed [24]. The specific increase in current depends on many factors including the size of the transistor, and the size and location of the breakdown.

Unlike HBD, apart from increased leakage current in it's off state, SBD generally does not affect the performance of the transistor much [37]. With technologies that have thin  $t_{ox}$  the gate tunnelling leakage is large enough that any increase in gate current due to SBD in the transistor's on-state are not important. However, when the transistor is off, and if SBD occurs near the drain extension there is an increase in Gate-Induced Drain Leakage (GIDL) of five orders of magnitude. This increase in GIDL is due to the negative charge trapping in the oxide over the overlap region. SBD at other locations of the gate has very minimal effect on the operation of the transistor. Also, as the drain extension forms a much smaller percentage of the total transistor length, long-channel transistors are less likely to have any SBD effects, SBD does however affect circuit performance for transistors with low W/L. Since the gate area is very small, the SBD region composes a considerable portion of the gate area.

Under such circumstances, the transconductance  $g_m$  of the transistor drops by 50% and the saturation current falls to 30% of its original value [38].

# 2.6 Carrier heating and channel noise in sub-micron MOSFET

Hot carriers can be trapped at the Si-SiO2 interface or within the oxide itself and hence interface states are generated in the process, forming space charges (volume charges) that increase over time as more carriers are trapped. These trapped charges shift some of the characteristics of the device, such as its threshold voltage ( $V_{th}$ ).

Injected carriers that do not get trapped in the gate oxide become gate current. On the other hand, the majority of the holes from the e-h pairs generated by impact ionization flow back to the substrate, comprising a large portion of the substrate's drift current. Excessive substrate current may therefore be an indication of hot carrier degradation. In gross cases, abnormally high substrate current can upset the balance of carrier flow and facilitate latch-up.

Hot-carrier effects are among the main concerns when shrinking FET dimensions into the deep sub micrometer regime. Experiments have shown that, in short-channel devices, the measured drain current noise is much higher than the one predicted by the long-channel model. The most popular explanation for the excess channel thermal noise observed in sub micrometer MOSFETs is based on the postulation of carrier heating and hot carriers. It is expected that the increase of mobility with reduced gate bias enhances carrier velocity and

consequently the value of the noise factor  $\gamma$  since high  $\gamma$  is due to phenomena like velocity saturation and hot electrons [32].

However, recent modeling results reported from different research groups [39, 40] do not support the above postulation. Scholten et al. [29] suggest that it is possible to predict the excess noise without invoking carrier heating based on a surface-potential-based compact MOS model with improved descriptions of carrier mobility and velocity saturation. Chen and Deen [30] demonstrated that the excess channel noise in deep-sub micrometer MOSFETs could be modeled by considering channel length modulation. Furthermore, simulation based on a non-stationary transport model [41] suggests that the source side of the channel is responsible for most of the excess noise. This obviously does not support the explanations related to carrier heating and velocity saturation where the drain side of the channel is associated with these phenomena. It is noted that all the aforementioned studies were based on complicated RF modeling, and some ambiguities could arise during the definition of device models and parameter extraction. This, in turn, influences the direct understanding of the various physical origins of RF noise in sub micrometer devices. To date, however, solid evidence of the dependence of channel noise on carrier heating is still lacking.

On the other hand, recent studies on deep-sub micrometer MOSFETs with reverse body bias  $(V_b)$  reveal that a reverse  $V_b$  increases the electric field of the drain–substrate junction which then induces secondary impact ionization by the enhanced heating of holes [42, 43, 44]. This then substantially increases the

population of high-energy (hot) carriers. This was confirmed by Monte Carlo simulation [45] and light emission measurement [46]. The carrier heating in sub micrometer NMOSFETs by reverse  $V_b$  provides a possible means to directly verify the contribution of carrier heating to channel noise by modulating the number of high-energy electrons.

# 2.7 Summary

In this chapter, a small signal equivalent circuit of RF MOSFETs is introduced. The small signal modeling methods are reviewed. This is followed by a detailed description of a procedure to extract the parameters in the equivalent circuit. Noise sources in electronic devices are investigated. Three major noise sources exist in MOSFETs, thermal noise, shot noise and flicker noise. The physical origins are studied and their manifestations in MOSFETs are presented with equations to describe their behaviors. Noise parameters are defined, which are used to describe noise performances of a device. After that, noise two-port networks and direct matrix operations are used to extract noise currents in MOSFETs directly from noise and small-signal measurements. In the final part, previous work on the relationship of gate oxide breakdown and noise, gate oxide breakdown and location, hot carrier heating and hot carrier effect and channel noise is reviewed.

**Chapter 4 Experiments**

3.1 Devices

The devices used for the tests in this work are n-MOSFETs fabricated using a commercial dual gate oxide process with shallow trench isolation (STI). The N-MOSFETs had 16 or 8 gate fingers with a drawn channel length and width of 0.18 µm and 5 µm respectively. The gate oxide was ~29 Å thick

containing ~1% nitrogen, grown via rapid thermal oxidation and N<sub>2</sub>O annealing.

3.2 Measurements

Device characterizations were carried out using a semi-auto Cascade probe station. An HP4156B semiconductor parameter analyzer was used for DC measurements. Device S-parameters were measured using an HP8510B

network analyzer with a frequency of up to 50 GHz.