# This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Heterogeneous multi-core systems for bioinformatics

Adrianto Wirawan

2010

Adrianto, W. (2010). Heterogeneous multi-core systems for bioinformatics. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/42096

https://doi.org/10.32657/10356/42096

Downloaded on 13 Mar 2024 17:28:07 SGT

# HETEROGENEOUS MULTI-CORE SYSTEMS FOR BIOINFORMATICS

by

#### Adrianto Wirawan

Supervisor: Dr. Kwoh Chee Keong and Dr. Bertil Schmidt

Division of Information Systems School of Computer Engineering Nanyang Technological University

A thesis submitted to the Nanyang Technological University in fulfillment of the requirement of the degree of Doctor of Philosophy

**July 2009**

## STATEMENT OF ORIGINALITY

| I hereby certify that the content of this thesis is the not been submitted for higher degree to any other | • •       |

|-----------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

| Date                                                                                                      | Signature |

#### **ABSTRACT**

The bioinformatics research area is now faced with an obstacle of ever-increasing biological data to verify their biological discovery. As data increases, so does the workload for managing, processing and analysing this data. Combined with the inherent complexity of biological problems, traditional approaches results in long run-time and huge memory requirements. The emergence of accelerator technologies such as multicore architectures provides the opportunity to achieve significant improvements in execution time for many bioinformatics applications, compared to sequential general-purpose platforms. Using multi-cores to solve large scale bioinformatics applications, such as sequence analysis, is therefore a promising and challenging research field, since large-scale computational bioinformatics problems can benefit much from this kind of processing power.

In order to implement efficient and scalable code for this type of architecture, a shift of paradigm in applications development and novel programming techniques are required. In this thesis, we investigate algorithms and techniques on how to efficiently map bioinformatics applications onto a heterogeneous multi-core system, the Cell Broadband Engine (Cell/BE). In particular, we have focused on the following important and widely used applications, i.e. alignment of long DNA sequences, Smith-Waterman algorithm, BLASTP algorithm and pairwise distance matrix computations, which is an integral part of the multiple sequence alignment algorithms such as ClustalW.

Aligning long DNA sequences is a common and often repeated task in molecular biology. We have developed a novel, efficient and scalable parallel algorithm for very long DNA sequence alignment on a heterogeneous multi-core system, the Cell Broadband Engine.

Our implementation utilizes two types of parallelization techniques: (i) SIMD vectorization within a processor and (ii) wavefront parallelization between processors. We have also introduced a partitioning scheme to overcome the local storage limitation of the Synergistic Processor Elements (SPEs) as well as a direct SPE to SPE DMA transfer communication technique. Performance evaluation shows that our implementation achieves almost linear speedup and leads to significant computational time savings for large datasets.

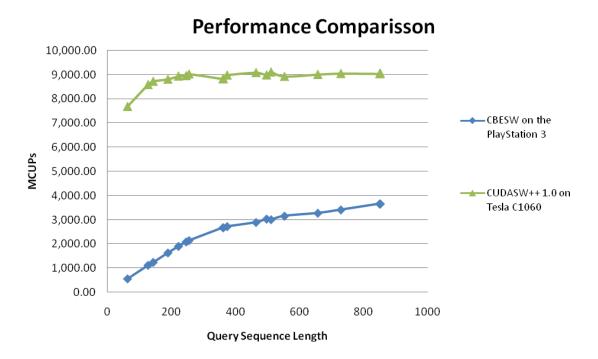

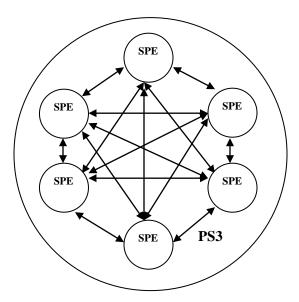

Next, we have demonstrated how the PlayStation® 3, powered by the Cell Broadband Engine, can be used as a computational platform to accelerate the Smith-Waterman algorithm, a method for optimal pairwise sequence alignment. For large protein datasets, our implementation on the PlayStation® 3 provides a significant improvement in running time compared to other implementations such as SSEARCH, Striped Smith-Waterman and CUDA-SW.

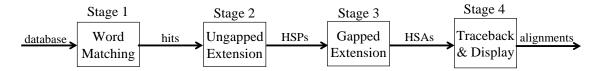

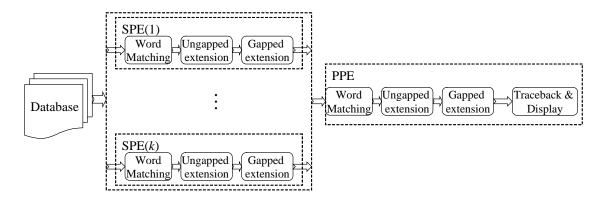

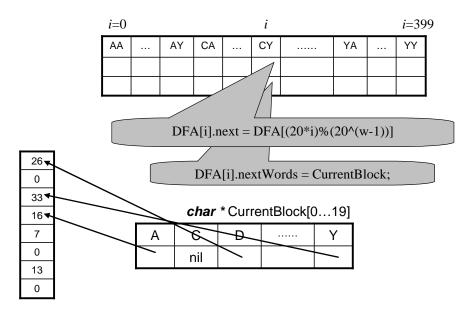

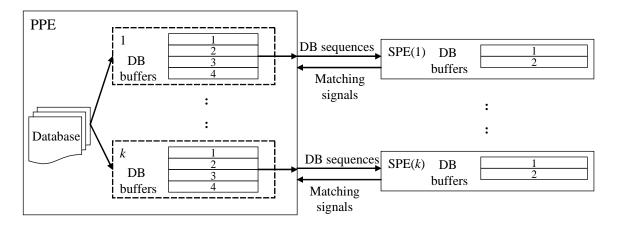

Furthermore, we have developed a novel implementation to accelerate a heuristic protein sequence database scanning algorithm, the BLASTP heuristic, on to a heterogeneous multi-core system, the Cell Broadband Engine. To our knowledge, this is the first ever reported parallelization of BLASTP on a heterogeneous multi-core system. We have also introduced a new parallel communication pattern, in which the Power Processor Element (PPE) coordinates the data transfer. Furthermore, we have utilized a data structure similar to compressed *deterministic finite-state automaton* (DFA) to fit the codeword lookup data in the SPEs. The BLASTP implementation on a Playstation®3 leads to significant runtime savings compared to corresponding sequential implementations.

Finally, we have developed an efficient parallel implementation that accelerates the distance matrix computation used in multiple sequence alignments on the x86 and Cell Broadband Engine architecture, a homogeneous and heterogeneous multi-core system, respectively. By taking advantage of multiple processors as well as SIMD vectorization, we are able to achieve speedups of two orders of magnitude compared to the publicly available implementations utilized in multiple sequence alignment algorithms. We have also compared the performance of our implementation on the Playstation®3 with other accelerator technologies, i.e. reconfigurable accelerators, such as FPGAs, and GPUs with CUDA programming model.

#### **ACKNOWLEDGEMENT**

First and foremost, I would like to thank God for His grace and blessings throughout the entire study.

I wish to express my deepest gratitude to my PhD supervisor Dr. Kwoh Chee Keong and Dr. Bertil Schmidt, for their valuable guidance, assistance and advice throughout the entire study. Their continuous encouragement and motivational support have been the driving force behind this study.

I would also like to thank Mr. Gerrit Voss, Mr. Tan Chee Hian, Mr. Nim Tri Hieu, Mr. Liu Yongchao and Mr. Zhang Huiliang and all others who have supported my research.

Last but not least, I would like to thank all my family and friends for their endearing love and faithful support.

#### **AUTHOR'S PUBLICATION**

#### **Journal Papers**

- 1. <u>A. Wirawan</u>, C.K. Kwoh, B. Schmidt: *Multi Threaded Vectorized Distance Matrix Computation on the Cell/BE and x86/SSE2 Architectures*, Bioinformatics, 2010, in press. doi:10.1093/bioinformatics/btq135 (Impact factor: 4.328)

- 2. <u>A. Wirawan</u>, B. Schmidt, H. Zhang, C.K. Kwoh: *High Performance Protein Sequence Database Scanning on the Cell B.E. Processor*, Scientific Programming, Vol. 17, No. 1-2, pp. 97-111, 2009

- 3. A. Wirawan, C.K. Kwoh, T.H. Nim, B. Schmidt: *CBESW: Sequence Alignment on the Playstation 3*, BMC Bioinformatics, Vol. 9:377, 2008 (Impact factor: 3.78).

- 4. Y. Liu, B. Schmidt, <u>A. Wirawan</u>, C.K. Kwoh, D.L. Maskell: *Comparison of Accelerator Architectures for Large-Scale Biological Sequence Alignment*, IEEE Transactions on Parallel and Distributed Systems, under review.

#### **Conference Papers**

- A. Wirawan, B. Schmidt, C.K. Kwoh: Pairwise Distance Matrix Computation for Multiple Sequence Alignment on the Cell Broadband Engine, The International Conference on Computational Science 2009 (ICCS 2009), Baton Rouge, Louisiana, Springer, LNCS, Vol. 5544, pp. 954-963, 2009.

- 2. <u>A. Wirawan</u>, B. Schmidt, C.K. Kwoh: *Parallel DNA Sequence Alignment on the Cell Broadband Engine*,7th International Conference on Parallel Processing and

- Applied Mathematics (PPAM 2007), Gdansk, Poland, Springer, LNCS Vol. 4967, pp. 1249-1256, 2008.

- 3. <u>A. Wirawan</u>, B. Schmidt: *Parallel Discovery of Transcription Factor Binding Sites*, IEEE Asia Pacific Conference on Circuits and Systems (APCCAS 2006), Singapore, IEEE Press, 2006.

- 4. N.T. Hieu, C.K. Kwoh. A. Wirawan, B. Schmidt: Applications of Heterogeneous Structure of Cell Broadband Engine Architecture for Biological Database Similarity Search, 2nd International Conference on Bioinformatics and Biomedical Engineering (iCBBE2008), IEEE Press, pp. 5-8, 2008.

### **TABLE OF CONTENTS**

| ABSTRACT                                 | i   |

|------------------------------------------|-----|

| ACKNOWLEDGEMENT                          | iv  |

| AUTHOR'S PUBLICATION                     | v   |

| TABLE OF CONTENTS                        | vii |

| LIST OF TABLES                           | xii |

| LIST OF EQUATIONS                        | xii |

| LIST OF FIGURES                          | xiv |

| 1. INTRODUCTION                          | 1   |

| 1.1. Overview                            | 1   |

| 1.2. Motivation                          | 4   |

| 1.3. Objectives                          | 9   |

| 1.4. Contributions                       | 10  |

| 1.5. Synopsis of Thesis                  | 12  |

| 2. STATE OF THE ART                      | 14  |

| 2.1. Algorithm implementation techniques | 14  |

| 2.1.1. Exhaustive Search Algorithms      | 14  |

| 2.1.2. Branch-and-Bound Algorithms       | 14  |

| 2.1.3. Dynamic Programming Algorithms    | 15  |

| 2.1.4. Greedy Algorithms                 | 16  |

| 2.1.5. Divide and Conquer Algorithms     | 16  |

| 2.1.6. Machine Learning Algorithms       | 17  |

| 2.1.7. Heuristic Algorithms              | 17  |

| 2.2. Sequence Alignment                  | 18  |

| 2.2.1. Types of Alignment                | 18  |

| 2.2.1.1. Pairwise sequence alignment     | 18  |

| 2.2.1.2. Multiple sequence alignment     | 20  |

| 2.2.2. Scoring Scheme                    | 22  |

| 2.2.2.1. Substitution Matrix             | 22  |

| 2.2.2.1.1. Unitary Scoring Matrix        | 22  |

| UNIVERSITY                                                  | Preface |

|-------------------------------------------------------------|---------|

| 2.2.2.1.2. Log-odds ratio                                   | 23      |

| 2.2.2.1.3. Point Accepted Mutation (PAM)                    | 23      |

| 2.2.2.1.4. Block Substitution Matrix (BLOSUM)               | 24      |

| 2.2.2.2. Gap Penalties                                      | 25      |

| 2.2.3. Alignment Algorithms                                 | 26      |

| 2.2.3.1. Global alignment: Needleman-Wunsch algorithm       | 26      |

| 2.2.3.2. Local alignment: Smith-Waterman algorithm          | 28      |

| 2.2.3.3. Algorithms with affine gap penalty                 | 29      |

| 2.2.3.4. Heuristic alignment algorithms                     | 29      |

| 2.2.3.4.1. BLAST                                            | 30      |

| 2.2.3.4.2. FASTA                                            | 31      |

| 2.3. Parallel Computation Model and Parallel Architectures  | 32      |

| 2.3.1. Terminology                                          | 34      |

| 2.3.1.1. Speed-up                                           | 34      |

| 2.3.1.2. Parallel Overhead                                  | 34      |

| 2.3.1.3. Synchronization                                    | 34      |

| 2.3.1.4. Efficiency                                         | 35      |

| 2.3.1.5. Scalability                                        | 35      |

| 2.3.1.6. Task                                               | 35      |

| 2.3.2. von Neumann Architecture                             | 36      |

| 2.3.3. Flynn's Classical Taxonomy                           | 37      |

| 2.3.3.1. Single Instruction, Single Data (SISD)             | 37      |

| 2.3.3.2. Single Instruction, Multiple Data (SIMD)           | 38      |

| 2.3.3.3. Multiple Instruction, Single Data (MISD)           | 39      |

| 2.3.3.4. Multiple Instruction, Multiple Data (MIMD)         | 40      |

| 2.4. Accelerator Technologies in High Performance Computing | 41      |

| 2.4.1. VLSI                                                 | 41      |

| 2.4.2. FPGA                                                 | 42      |

| 2.4.3. GPU                                                  | 43      |

| 2.4.4. Multi-Core                                           | 47      |

| 2.4.4.1. Homogeneous Multi-core                             | 48      |

|    | Pre                                                        | етасе |

|----|------------------------------------------------------------|-------|

|    | 2.4.4.2. Heterogeneous Multi-core                          | . 48  |

|    | 2.4.4.3. Cluster of Multi-core                             | . 49  |

| 3. | CELL BROADBAND ENGINE                                      | . 50  |

|    | 3.1. Introduction                                          | . 50  |

|    | 3.2. Cell/BE Architecture                                  | . 50  |

|    | 3.3. Overcoming the Three Wall Limitations                 | . 53  |

|    | 3.3.1. Overcoming the Power Wall                           | . 53  |

|    | 3.3.2. Overcoming the Memory Wall                          | . 54  |

|    | 3.3.3. Overcoming the Frequency Wall                       | . 54  |

|    | 3.4. Interprocessor communication                          | . 55  |

|    | 3.4.1. DMA transfer                                        | . 55  |

|    | 3.4.2. Mailboxes                                           | . 57  |

|    | 3.4.3. Signal notification channels (Signals)              | . 58  |

|    | 3.5. Developing Applications for the Cell Broadband Engine | . 60  |

|    | 3.5.1. Vectorization                                       | . 61  |

|    | 3.5.2. Data Alignment                                      | . 61  |

|    | 3.5.3. Double-Buffering                                    | . 61  |

|    | 3.5.4. Data Reuse                                          | . 62  |

|    | 3.5.5. Branch Minimization                                 | . 62  |

|    | 3.6. Programming techniques for the Cell/BE                | . 62  |

|    | 3.6.1. Function-Offload Model                              | . 64  |

|    | 3.6.2. Computation-Acceleration Model                      | . 66  |

|    | 3.6.3. Streaming Model                                     | . 72  |

| 4. | ALIGNING LONG DNA SEQUENCE ON THE CELL BROADBAND ENGINE    | . 74  |

|    | 4.1. Introduction                                          | . 74  |

|    | 4.2. Smith-Waterman Algorithm                              | . 75  |

|    | 4.3. Wavefront Parallelization                             | . 77  |

|    | 4.4. SIMD Parallelization                                  | . 79  |

|    | 4.5. Performance Evaluation                                | . 82  |

|    | 4.6. Summary                                               | . 87  |

| 5. CBESW: IMPLEMENTATION OF THE SMITH-WATERMAN ALG       | ORITHM ON |

|----------------------------------------------------------|-----------|

| THE PLAYSTATION®3                                        | 88        |

| 5.1. Introduction                                        | 88        |

| 5.2. Smith-Waterman Algorithm                            | 89        |

| 5.3. IMPLEMENTATION                                      | 90        |

| 5.3.1. Mapping to the Cell Broadband Engine              | 90        |

| 5.3.2. Query Profile                                     | 93        |

| 5.3.3. Saturation Arithmethic                            | 95        |

| 5.4. Performance Evaluation                              | 95        |

| 5.5. Summary                                             | 102       |

| 6. IMPLEMENTATION OF A HEURISTIC PROTEIN SEQUENCE DA     | TABASE    |

| SCANNING ALGORITHM ON THE CELL/BE                        | 104       |

| 6.1. Introduction                                        | 104       |

| 6.2. BLAST-P Algorithm                                   | 105       |

| 6.3. IMPLEMENTATION                                      | 107       |

| 6.3.1. Parallelization Approach                          | 107       |

| 6.3.2. Mapping to the Cell Broadband Engine              | 108       |

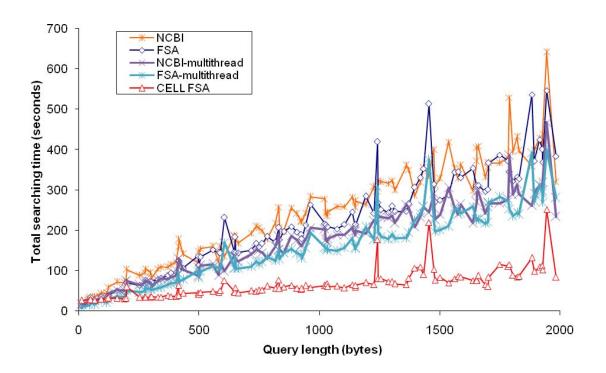

| 6.4. Performance Evaluation                              | 113       |

| 6.5. Summary                                             | 117       |

| 7. PAIRWISE DISTANCE MATRIX COMPUTATION                  | 119       |

| 7.1. Introduction                                        | 119       |

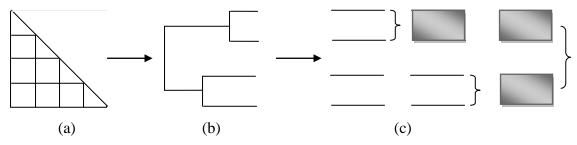

| 7.2. Multiple Sequence Alignment Algorithm               | 120       |

| 7.3. Mapping to the Cell/BE                              | 123       |

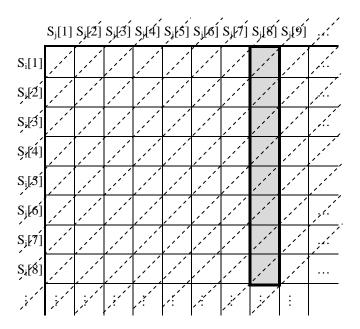

| 7.3.1. Query Profile                                     | 123       |

| 7.3.2. SIMD-specific Implementations                     | 124       |

| 7.3.3. Multithreading-specific Implementations           | 127       |

| 7.4. Mapping to the x86/SSE2 Architecture                | 129       |

| 7.5. Performance Evaluation                              | 130       |

| 7.5.1. Performance Analysis                              | 130       |

| 7.5.2. Comparison against X86/SSE2 Architecture          |           |

| 7.5.3. Comparison against Other Accelerator Technologies |           |

| ~                                                                       | Preface     |

|-------------------------------------------------------------------------|-------------|

| 7.6. Summary                                                            | 142         |

| 8. CONCLUSION AND FUTURE WORK                                           | 144         |

| 8.1. Conclusion                                                         | 144         |

| 8.2. Future Work                                                        | 148         |

| 8.2.1. Protein-Protein Interaction Prediction using Parallel GA with Is | sland Model |

| on the Cell/BE Architecture                                             | 148         |

| 8.2.2. Implementation of A Short Read Assembly Algorithm for de n       | ovo Genomic |

| Sequencing on the Cell/BE Architecture                                  | 150         |

| 8.2.3. Open Programming Language (OpenCL) on the Cell/BE                | 151         |

| 8.2.4. The future of the cell broadband engine architecture             | 153         |

| REFERENCES                                                              | 157         |

### LIST OF TABLES

| Table 1. Traditional BLAST Programs                                                        | 30  |

|--------------------------------------------------------------------------------------------|-----|

| Table 2. Flynn's Taxonomy                                                                  | 37  |

| Table 3. Comparison of mailboxes and signals                                               | 60  |

| Table 4. Classification of Cell/BE applications into programming techniques                | 63  |

| Table 5. Performance evaluation results of the SIMD parallelization                        | 87  |

| Table 6. List of SPU Low-Level Specific and Generic Intrinsics used                        | 90  |

| Table 7. CBESW Performance Evaluation                                                      | 97  |

| Table 8. List of query sequences used in different performance comparisons                 | 98  |

| Table 9. Breakdown of execution time of BLASTP                                             | 107 |

| Table 10. Performance comparison between Cell/BE BLASTP and FSA-BLASTP                     | 115 |

| Table 11. Average number of sequences processed by each stage of FSA-BLASTP on             | a   |

| P4 and by the PPE in Cell/BE BLASTP                                                        | 116 |

| Table 12. Runtime statistics of three exceptional sequences                                | 117 |

| Table 13. Performance analysis of the parallel algorithm. The term $T$ and $S$ describes t | he  |

| runtime and speed up, respectively                                                         | 131 |

| Table 14. Categories of input protein dataset                                              | 132 |

| Table 15. Performance evaluation results                                                   | 133 |

| Table 16. Runtime speedups of the three accelerators compared with the sequential          |     |

| implementation                                                                             | 137 |

| Table 17. SLOC and performance per LOC of the three accelerators                           | 140 |

| Table 18. Performance per dollar of the three accelerators                                 | 141 |

| Table 19. Compute capability utilizations of the three accelerators                        | 142 |

# LIST OF EQUATIONS

| Equation 1. Unitary scoring matrix equation                                 | 22  |

|-----------------------------------------------------------------------------|-----|

| Equation 2. Log-odds ratio scoring matrix equation                          | 23  |

| Equation 3. Linear gap penalty equation                                     | 25  |

| Equation 4. Affine gap penalty equation                                     | 26  |

| Equation 5. Needleman-Wunsch equation                                       | 27  |

| Equation 6. Smith-Waterman equation                                         |     |

| Equation 7. Speed-up equation                                               | 34  |

| Equation 8. Efficiency equation                                             | 35  |

| Equation 9. Simplified efficiency equation                                  | 35  |

| Equation 10. Smith-Waterman equation for affine gap penalties               | 75  |

| Equation 11. Smith-Waterman equation for linear gap penalties               | 75  |

| Equation 12. Modified Smith-Waterman equation for the Cell/BE mapping       | 78  |

| Equation 13. Query profile equation for sequential layout                   | 93  |

| Equation 14. Query profile equation for striped layout                      | 93  |

| Equation 15. Segment length equation used for the query profile calculation | 94  |

| Equation 16. MCUPS calculation equation                                     | 96  |

| Equation 17. Distance value equation                                        | 121 |

| Equation 18. Recurrence relation equation by Liu et. al                     | 122 |

| Equation 19. Modified nid score equation                                    | 122 |

| Equation 20. Modified pairwise distance value equation                      | 123 |

| Equation 21. MCUPS calculation equation for pairwise distance matrix        | 137 |

### LIST OF FIGURES

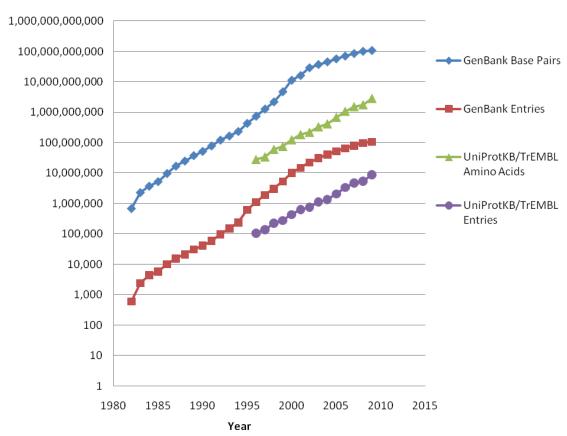

| $Figure\ 1.\ Growth\ rate\ of\ the\ GenBank\ and\ UniProtKB/TrEMBL\ databases\ on\ a\ se$ | mi-log |

|-------------------------------------------------------------------------------------------|--------|

| graph                                                                                     | 2      |

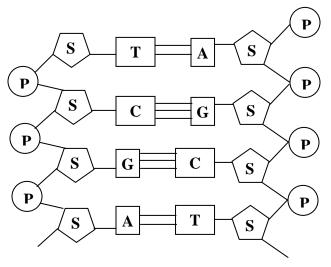

| Figure 2. DNA structure                                                                   | 5      |

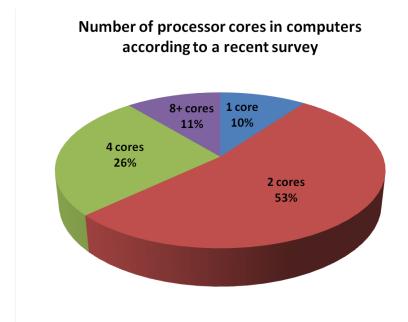

| Figure 3. Number of processor cores in computers according to a recent survey             | 8      |

| Figure 4. PAM250 matrix                                                                   | 24     |

| Figure 5. BLOSUM62 matrix                                                                 | 25     |

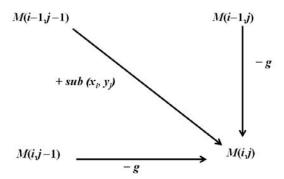

| Figure 6. Data dependency in Needleman-Wunsch algorithm                                   | 27     |

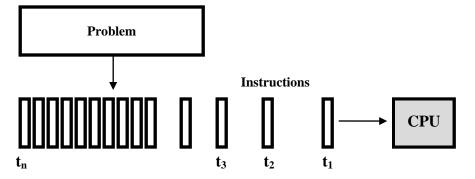

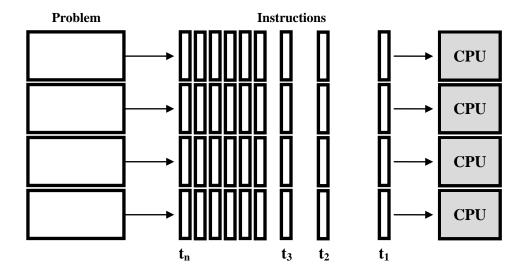

| Figure 7. Sequential programming execution                                                | 32     |

| Figure 8. Parallel programming execution                                                  | 33     |

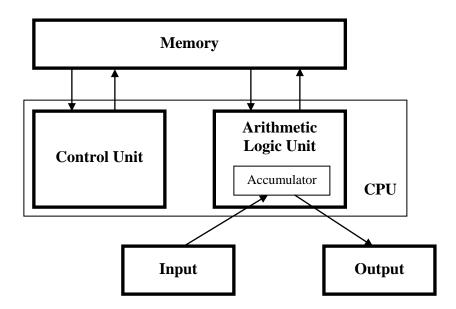

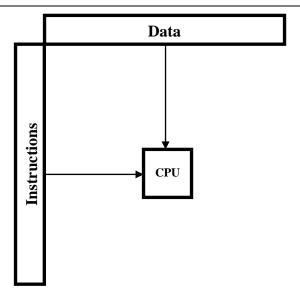

| Figure 9. Block diagram of the von Neumann architecture                                   | 36     |

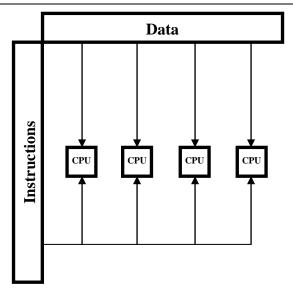

| Figure 10. Single Instruction, Single Data (SISD)                                         | 38     |

| Figure 11. Single Instruction, Multiple Data (SIMD)                                       | 39     |

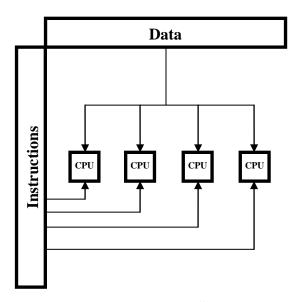

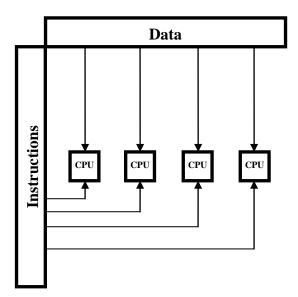

| Figure 12. Multiple Instructions, Single Data (MISD)                                      | 39     |

| Figure 13. Multiple Instruction, Multiple Data (MIMD)                                     | 40     |

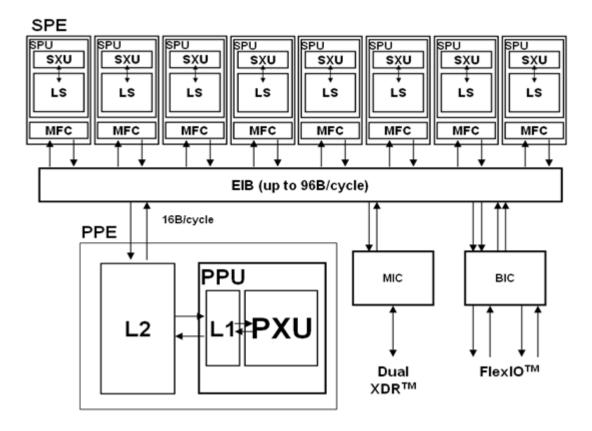

| Figure 14. Block diagram of the Cell Broadband Engine Architecture                        | 51     |

| Figure 15. Pseudocode of the Function Offload Model                                       | 64     |

| Figure 16. Pseudocode of the Computation-Acceleration Model                               | 67     |

| Figure 17. Pseudocode of the Streaming Model                                              | 72     |

| Figure 18. Data dependency in the SW algorithm alignment matrix                           | 76     |

| Figure 19. Sequence alignment of CAGTTTCG and ACAGTCGAACG                                 | 77     |

| Figure 20. Block diagram of the wavefront algorithm                                       | 78     |

| Figure 21. Pseudocode of the SIMD parallelization scheduling                              | 81     |

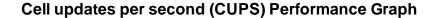

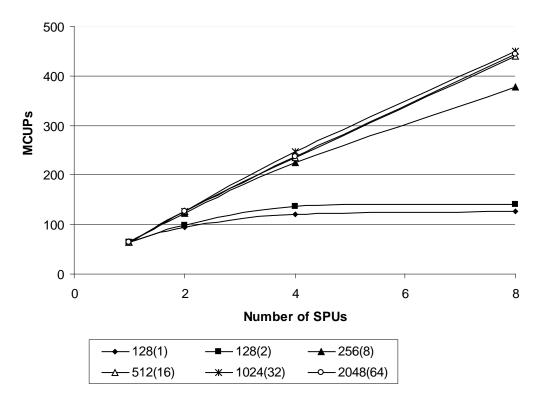

| Figure 22. Computational graph of the performance evaluation results                      | 83     |

| Figure 23. Speed-up graph of the performance evaluation results                           | 84     |

| Figure 24. CUPS graph of the performance evaluation results                               | 85     |

| Figure 25. Efficiency graph of the performance evaluation results                         | 86     |

| Figure 26. Mapping of the different stages of the CBESW implementation                    | 91     |

| Figure 27. Pseudocode of the SPE code for the Cell/BE mapping                             | 92     |

| Figure 28. Query profile layout                                                           | 94     |

| Figure 29. Performance comparison with the SSEARCH implementation                       |

|-----------------------------------------------------------------------------------------|

| Figure 30. Performance comparison with the Striped Smith-Waterman implementation        |

|                                                                                         |

| Figure 31. Performance comparison with the CUDA implementation on a single Nvidia       |

| GeForce 8800GTX101                                                                      |

| Figure 32. Performance comparison with the CUDASW++ implementation on a single          |

| NVIDIA Tesla C1060 102                                                                  |

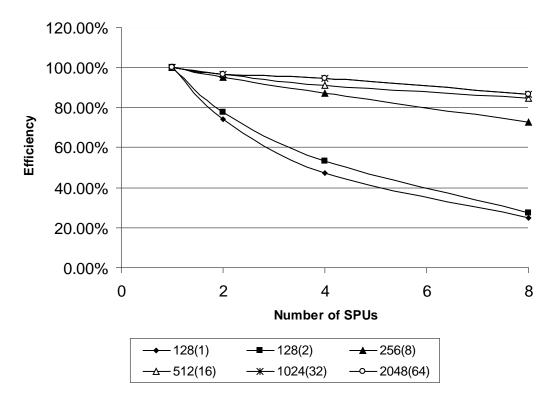

| Figure 33. The BLASTP processing pipeline                                               |

| Figure 34. Mapping of the different stages of the BLASTP algorithm onto the Cell/BE     |

|                                                                                         |

| Figure 35. Illustration of the compressed FSA data structure for <i>w</i> =3            |

| Figure 36. Buffering scheme                                                             |

| Figure 37. Pseudocode of the PPE code                                                   |

| Figure 38. Pseudocode of the SPE code                                                   |

| Figure 39. Performance comparison between our Cell/BE BLASTP implementation with        |

| the FSA-BLASTP and the NCBI-BLASTP114                                                   |

| Figure 40. The three stages of the ClustalW algorithm. (a) Distance matrix computation. |

| (b) Guide tree construction. (c) Progressive alignment                                  |

| Figure 41. Example of a query profile for Lysine-specific histone demethylase 1 protein |

| (Swiss-Prot accession numbers O60341) with BLOSUM50 scoring matrix 124                  |

| Figure 42. Pseudocode of the SPE code                                                   |

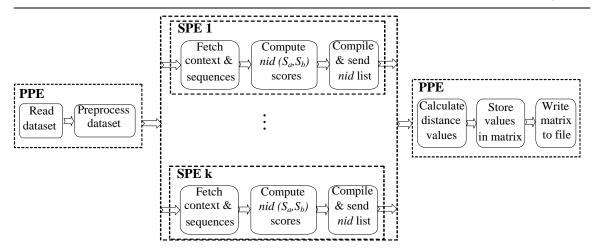

| Figure 43. Block diagram of our pairwise distance matrix implementation                 |

| Figure 44. Pseudocode of the <i>nid</i> score calculation                               |

| Figure 45. Mapping of pairwise distance matrix computation algorithm onto the Cell/BE   |

|                                                                                         |

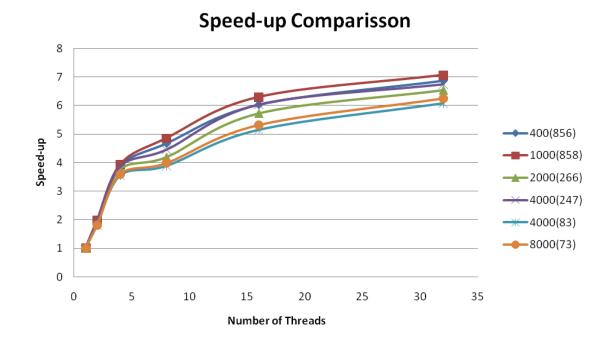

| Figure 46. Speed-up of our x86/SSE2 implementation with up to 32 threads                |

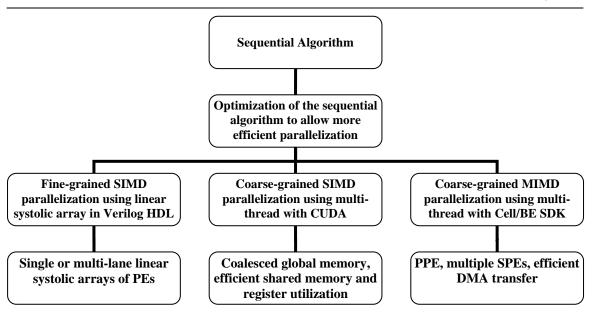

| Figure 47. Utilized parallelization and optimization approach for each                  |

| Figure 48. Parallel genetic algorithm with island model on the Playstation®3            |

#### 1. INTRODUCTION

#### 1.1. OVERVIEW

Due to the rapid progress of genome sequencing projects in the past decade, there has been an exponential increase in the amount of available genomic sequence data. The three principal comprehensive databases of nucleotide sequences currently are:

#### 1. GenBank[1]

GenBank is the National Institute of Health (NIH) genetic sequence database, which is composed of an annotated collection of all publicly available DNA sequences. It is maintained at the National Center for Biotechnology Information (NCBI) in Maryland, USA.

# 2. <u>European Molecular Biology Laboratory (EMBL) Nucleotide Sequence</u> Database[2]

The EMBL Nucleotide Sequence Database constitutes Europe's primary nucleotide sequence resource. Main sources for DNA and RNA sequences are direct submissions from individual researchers, genome sequencing projects and patent applications. It is maintained at the European Bioinformatics Institute (EBI) in Cambridge, UK.

#### 3. <u>DNA Data Bank of Japan (DDBJ)[3]</u>

DDBJ is based in Japan's National Institute of Genetics. DDBJ is the sole DNA data bank in Japan, which is officially certified to collect DNA sequences from researchers and to issue the internationally recognized accession number to data submitters. It is maintained at the National Institute of Genetics in Mishima, Japan.

These three databases form the International Nucleotide Sequence Database Collaboration[4], which has led to many beneficial projects, e.g. the taxonomy project[5] and the feature table[6]. Since all three databases exchange the collected data on a daily basis, the three data banks share virtually the same data at any given time. Their objective is to ensure that nucleotide sequence information's are stored publicly and freely, such that it is easily accessible for researchers and scientists worldwide. This policy has proved to be tremendously successful for the progress of science and has led to an enormous increase in size and usage of genome databases.

#### Growth Rate of GenBank and UniProtKB/TrEMBL

Figure 1. Growth rate of the GenBank and UniProtKB/TrEMBL databases on a semi-log graph

Genome and protein databases are growing exponentially and this growth rate will continue for a foreseeable future. The GenBank release notes for release 172.0 in June 2009 state that "from 1982 to the present, the number of bases in GenBank has doubled approximately every 18 months." This trend is also reflected in protein databases. The UniProtKB/TrEMBL Database[7, 8] release notes for release 40.5 in July 2009 states that compared to a previous release 3 months ago, the current dataset" represents an increase of 16%". Figure 1 illustrates the number of base pairs and entries in the GenBank from 1982 to June 2009 as well as the number of amino acids and entries in the UniProtKB/TrEMBL Database from 1996 to July 2009 on a semi-log graph.

Furthermore, the advent of high-throughput next generation sequencing technologies also brought a need for high throughput in bioinformatics. Two new sequencing technologies were introduced in 2005, i.e. the 454 system using pyrosequencing technology [9], and the Solexa system, which detects fluorescence signals [10]. Both sequencing technologies execute millions of sequencing reactions in parallel, producing data at ultrahigh rates [11]. These next generation technologies offer drastically faster and cost-effective sequence throughput and are vastly superior to shotgun sequencing due to the high volume of data and the drastically short time to sequence a whole genome or disease genome, although genome assembly is much more computational expansive. Therefore, the next generation sequencing technologies will foster enormous potential applications of high performance computing technologies in bioinformatics.

Bioinformatics is a growing research field which involves the use of compute-intensive techniques to solve and analyze biological data. Major research efforts in the field such as sequence alignment, prediction of gene expression, and protein-protein interactions relies

on fast and reliable computational approaches. Furthermore, most bioinformatics applications with optimal solutions are often associated with long runtimes and expensive resources. These are due to various factors:

- Biological data are obtained by experiments. Hence, they are prone to errors. The

need to deal with errors and uncertainties results in high complexity algorithms.

- Some problems that can be solved using polynomial time algorithms have massive computational requirements due to large data sets that have to be analyzed.

- Many problems are computationally intensive due to their inherent algorithmic complexities, e.g. protein folding[12]. Some problems are even NP-hard problems, which means an exact solution cannot be solved in polynomial time.

The work presented in this thesis is mainly concerned with constructing efficient multicore algorithms and techniques that address bioinformatics problems, especially in the area of sequence alignment.

#### 1.2. MOTIVATION

In the last few decades, scientists have tried to understand how life evolved by studying the flow of genetic information in a cell. DNA (deoxyribonucleic acid) is the genetic material, which are read and translated into proteins with specific functions. A common theme throughout biological systems at all levels is that structure and function are intimately related. Therefore, the first step would be to know and understand the DNA and protein structure thoroughly, as well as the organization of the whole molecule as the genomes of an organism. Bioinformatics is a field that would provide approaches for research on DNA and protein sequences as it relies on extensive computational

approaches to decode the information hidden behind billions of nucleotides and amino acids, respectively.

Figure 2. DNA structure

DNA was discovered in 1869. The two strands of a DNA molecule are tied together in a helical structure, known as the double helix structure[13]. Four different bases are used to form the DNA molecules: *adenine*, *cytosine*, *guanine*, *thymine* (**A**, **C**, **G**, **T**). Pairs are always formed between the bases **A** and **T**, and between **G** and **C**. Each base is attached to a phosphate group and a deoxyribose sugar to form a nucleotide, as shown in Figure 2. DNA contains the genetic instructions used in the development and functioning of all known living organisms and some viruses. The main role of DNA molecules is the long-term storage of information. DNA is often compared to a set of blueprints or a recipe, or a code, since it contains the instructions needed to construct other components of cells, such as proteins and RNA molecules. The DNA segments that carry this genetic information are called genes. Other DNA segments have structural purposes, or are involved in regulating the use of this genetic information.

Proteins (also known as polypeptides) are organic compounds made of amino acids arranged in a linear chain polymer and joined together by peptide bonds between the carboxyl and amino groups of adjacent amino acid residues. The sequence of amino acids in a protein is defined by the sequence of a gene, which is encoded in the genetic code. In general, the genetic code specifies 20 standard amino acids, however in certain organisms the genetic code can include selenocysteine and pyrrolysine. Shortly after or even during synthesis, the residues in a protein are often chemically modified by post-translational modification, which alter the physical and chemical properties, folding, stability, activity, and ultimately, the function of the proteins. Proteins can also work together to achieve a particular function, and they often associate to form stable complexes.

Like other biological macromolecules such as polysaccharides and nucleic acids, proteins are essential parts of organisms and participate in virtually every process within cells. Many proteins are enzymes that catalyze biochemical reactions and are vital to metabolism. Proteins also have structural or mechanical functions, such as actin and myosin in muscle and the proteins in the cytoskeleton, which form a system of scaffolding that maintains cell shape. Other proteins are important in cell signaling, immune responses, cell adhesion, and the cell cycle. Proteins are also necessary in animals' diets, since animals cannot synthesize all the amino acids they need and must obtain essential amino acids from food. Through the process of digestion, animals break down ingested protein into free amino acids that are then used in metabolism.

Any alignment between two or more nucleotide or amino acid sequences represents an hypothesis regarding the evolutionary history of these sequences[14]. By aligning nucleotide or amino acid sequences, scientists have been able to determine and identify

important matched and mismatched regions. Matched regions may turn out to be functional homolog pairs, conserved regulatory regions or long repeats. Mismatched regions, on the other hand, may either be Single Nucleotide Polymorphisms (SNPs) or foreign fragments inserted due to transposition, sequence reversal or lateral transfer from another organism. Hence, comparisons of related nucleotide and protein sequences have assisted many recent developments in understanding the content, relationship and function of genetic sequences. As a direct result, sequence alignment and comparison techniques as well as database sequence searching techniques have been the cornerstone of bioinformatics.

Given the continuing improvements in high throughput genomic sequencing and the exponential growth in the size of sequence databases, new advances for bioinformatics area are needed by the research and scientific community. High Performance Computing (HPC) is one of the most popular technique to improve the performance without sacrificing the correctness of the solution[15]. The recent emergence of accelerator technologies such as FPGAs, GPUs and multi-core processors have made it possible to achieve an excellent improvement in execution time for many bioinformatics applications, compared to current general-purpose platforms. Examples of bioinformatics application that takes advantage of HPC are MPIBlast[16], MPI-HMMER[17], ClustalW-MPI[18, 19], PAxML[20], Folding@home[21], Phusion[22], GPU-ClustalW[23] and ClustalW using FPGA[24].

Multi-core technology was first discussed in 1989[25]. Conceptually, multi-core architecture refers to a single processor package containing two or more processor execution cores or computational engines that deliver fully parallel execution of multiple

software threads. The operating system treats each of its execution cores as a discrete processor, with all associated execution resources.

One of the ideas behind the movement to multi-core architectures is parallelism. It is one of the best ways to address the issue of power while maintaining performance where higher data throughput may be achieved with lower voltage and frequency. The result is a larger transistor count, but overall lower power dissipation and power density. Instead of classifying based upon speed, one could classify products based upon the number of working cores or overall data throughput. The integration of multiple cores on a chip also allows lower interconnect latency and therefore higher bandwidth between cores than their discrete counterparts. Hence, microprocessor designers and manufacturers have turned to building chip multi-processors[26-29]. A survey conducted in 2009[30] shows that 90% of common computers today uses multi-core processors and this trend is expected to continue. Figure 3 illustrates the survey according to [30].

Figure 3. Number of processor cores in computers according to a recent survey

Multi-core architectures may take on a number of forms. One form is the heterogeneous multi-core architecture, which can address a variety of applications. Another form is a large number of remedial homogeneous cores which divide and conquer computationally intensive applications and yet individually address less computationally intensive applications. Yet another form consists of a few complex homogeneous cores in which a single core could multitask between several remedial applications or individually handle computationally intensive applications. For any form of multi-core architecture, the application or algorithm development process must be significantly changed in order to fully explore the potential of multi-core processors.

The development of new homogeneous and heterogeneous multi-core architectures brings a shift of paradigm in applications development. In order to implement efficient and scalable code for this type of architecture, novel programming techniques are required. This continues to remain a largely unexplored territory and is the principal motivation behind our work.

#### 1.3. OBJECTIVES

The exponential growth of available biological data has caused bioinformatics to be rapidly moving towards a data-intensive, computational science. As a result, the computational power needed by bioinformatics applications is growing exponentially as well. Traditional approaches to sequence analysis techniques are expensive in terms of time and memory. HPC is a widely used method to improve performance. The emergence of accelerator technologies such as multi-core architecture has made it possible to achieve an excellent improvement in execution time for many bioinformatics applications,

compared to current general-purpose platforms. Therefore, using multi-cores to solve sequence analysis problems is a promising and challenging research field since large-scale computational bioinformatics problems can benefit much from this kind of processing power. Our objectives are as follows.

- Various parallel algorithms for solving sequence analysis problems have been presented for different parallel architectures, e.g. Field Programmable Gate Array (FPGA) and Graphical Processing Unit (GPU). However, multi-cores have their own characteristics. Therefore, new sequence analysis algorithms have to be presented in order to execute efficiently on multi-core architectures.

- The development of sequence analysis algorithms for multi-core architecture is made challenging by the heterogeneous nature of the resources involved. Therefore, new parallel communication patterns and partitioning scheme in parallel models are required.

- The emergence of commonly available accelerator technologies, such as FPGA, GPU, and the Cell/BE processor provide an opportunity to achieve orders-of magnitude performance. Hence, performance evaluation and comparison between these accelerator technologies is required to give a comprehensive understanding of the advantages and disadvantages of these accelerators as well as to provide a reference for mapping algorithms or applications onto them.

#### 1.4. CONTRIBUTIONS

The contributions of our work can be briefly summarized as follows.

- We have developed a novel, efficient and scalable parallel algorithm for very long DNA sequence alignment on a heterogeneous multi-core system, the Cell Broadband Engine. Our implementation utilizes two types of parallelization techniques: (i) SIMD vectorization within a processor and (ii) wavefront parallelization between processors. We also introduced a partitioning scheme to overcome the local storage limitation of the Synergistic Processor Elements (SPEs) as well as a direct SPE to SPE DMA transfer communication technique. Performance evaluation shows that our implementation shows almost linear speedup and leads to significant computational time savings.

- We have demonstrated how the PlayStation® 3, powered by the Cell Broadband Engine, can be used as a computational platform to accelerate the Smith-Waterman algorithm, an optimal pairwise sequence alignment. For large protein datasets, our implementation on the PlayStation® 3 provides a significant improvement in running time compared to other implementations such as SSEARCH, Striped Smith-Waterman and CUDA-SW.

- We have developed a novel implementation to accelerate a heuristic protein sequence database scanning algorithm, the BLASTP heuristic, on to a heterogeneous multi-core system, the Cell Broadband Engine. To our knowledge, this is the first ever reported parallelization of BLASTP on a heterogeneous multi-core system. We also introduced a new parallel communication pattern, in which the Power Processor Element (PPE) coordinates the data transfer. Furthermore, we utilized a data structure similar to compressed deterministic finite-state automaton (DFA) to fit the codeword lookup data

in the SPEs. The BLASTP implementation on a Playstation®3 leads to significant runtime savings compared to corresponding sequential implementations.

• We have developed an efficient parallel implementation that accelerates the distance matrix computation used in multiple sequence alignments on the x86 and Cell Broadband Engine architecture, a homogeneous and heterogeneous multi-core system, respectively. By taking advantage of multiple processors as well as SIMD vectorization, we are able to achieve speedups of two orders of magnitude compared to the publicly available implementation utilized in multiple sequence alignment algorithms. We have also compared the performance of our implementation on the Playstation®3 with other accelerator technologies, i.e. FPGA and GPU.

#### 1.5. SYNOPSIS OF THESIS

The rest of the thesis is structured as follows:

- Chapter 2 reviews algorithm design techniques for sequence alignment problems as well as parallel computation models and parallel architectures. Furthermore, we present a general survey of the state-of-the-art accelerator technologies in High Performance Computing (HPC).

- Chapter 3 introduces the Cell Broadband Engine, a recently introduced heterogeneous multi-core architecture system. Moreover, we discuss its characteristics, how it overcomes the *three wall limitations* as well as strategies and techniques on how to map applications onto such architecture in order to gain good performance.

- Chapter 4 elaborates our parallel algorithm to align very long DNA sequences as well as the implementation and performance evaluation on the Cell Broadband Engine.

- Chapter 5 demonstrates how the PlayStation® 3, powered by the Cell Broadband Engine, can be used as a computational platform to accelerate the Smith-Waterman algorithm for large protein datasets.

- Chapter 6 discusses our mapping of the popular heuristic protein sequence database scanning algorithm, the BLASTP on a heterogeneous multi-core system. The Playstation®3 implementation and performance evaluation are presented at the end of the chapter.

- Chapter 7 elaborates our efficient parallel implementation that accelerates the distance matrix computation used in multiple sequence alignments on a homogeneous and heterogeneous multi-core system. We also present a performance evaluation of our implementation on the Playstation®3 with other accelerator technologies.

- Chapter 8 concludes the achievement of our research work and suggests possible area of future work.

#### 2. STATE OF THE ART

This chapter reviews algorithm design techniques, sequence alignment as a popular and important genome analysis task as well as parallel computation and parallel architectures. Furthermore, we present a general survey of the state-of-the-art accelerator technologies in High Performance Computing (HPC).

#### 2.1. ALGORITHM IMPLEMENTATION TECHNIQUES

This section provides an overview of common algorithm design techniques used for sequence analysis.

#### 2.1.1. EXHAUSTIVE SEARCH ALGORITHMS

Exhaustive search, or brute-force search, is a trivial but very general problem-solving technique that consists of systematically enumerating all possible candidates for the solution and checking whether each candidate satisfies the problem's statement.

Exhaustive search algorithms are simple to implement, and guaranteed to find an optimal solution if it exists. However, their costs are proportional to the number of candidate solutions, which, in many practical problems, tend to grow exponentially as the size of the problem increases. Therefore, exhaustive search algorithm is typically only used for very small problem sizes or when the simplicity of implementation is more important than speed.

#### 2.1.2. BRANCH-AND-BOUND ALGORITHMS

Branch-and-Bound is a general design technique to find optimal solutions of optimization problems, especially in discrete and combinatorial optimization. It consists of a

systematic enumeration of all candidate solutions, where large subsets of fruitless candidates can be discarded, by using upper and lower estimated bounds of the quantity being optimized.

A branch-and-bound algorithm starts by considering the root problem (or the original problem with the complete feasible region) and applying the lower and upper bounding procedures. If the bounds match, then an optimal solution has been found and the procedure terminates. Otherwise, the feasible region is divided into two or more subproblem partitions. The algorithm is applied recursively to the sub-problems. If an optimal solution is found to a subproblem, it is a feasible solution to the full problem, but not necessarily be a global optimal solution. If the lower bound for a node exceeds the best known feasible solution, no globally optimal solution can exist in the sub-space of the feasible region represented by that particular node. Therefore, the node can pruned (removed from consideration). The search proceeds until all nodes have been solved or pruned, or until some specific threshold is met.

Examples of branch-and-bound algorithms used in bioinformatics include computational assignment of protein backbone NMR peaks[31] and matching protein structures[32].

#### 2.1.3. DYNAMIC PROGRAMMING ALGORITHMS

Dynamic programming algorithms solve complex problems by breaking them down into simpler steps. It is suitable to solve problems that exhibit the properties of overlapping subproblems and optimal substructure. A problem that can be broken down into subproblems, which are reused repeatedly, indicates that the problem has overlapping subproblems. Whereas, a problem with optimal substructure mean that an optimal solution can be constructed efficiently from optimal solutions to its subproblem.

Examples of dynamic programming algorithms used in bioinformatics include Smith-Waterman[33] and Needleman-Wunsch[34] for sequence alignment and Nussinov[35] and Zuker-Stiegler[36] for RNA folding.

#### 2.1.4. GREEDY ALGORITHMS

Greedy algorithms make the locally optimal choice at each iteration with the hope of finding the global optimum. They make whatever choice seems best at the moment, without regard for future consequences. It iteratively makes one greedy choice after another, reducing each given problem into a smaller one. When the algorithm terminates, the local optimum is hopefully equal to the global minimum. If this is the case, then the algorithm is correct. Otherwise, the algorithm has produced a sub-optimal solution.

Examples of greedy algorithms used in bioinformatics include G-PRIMER[37] and GreedyEM[38].

#### 2.1.5. DIVIDE AND CONQUER ALGORITHMS

As the name implies, a divide and conquer algorithm has two distinct phases, i.e. a divide phase and a conquer phase. In the divide phase, the algorithm splits the problem into smaller problem instances and solves them independently. The solutions of these smaller problems instances are combined into a solution of the original problem in the conquer phase.

The divide and conquer approach is similar to dynamic programming in that the solution of a large problem depends on a previously obtained solutions of sub-problems. The significant difference, however, is that sub-problems of the divide and conquer approach must be completely separate and can be solved independently.

Example of divide and conquer algorithms used in bioinformatics include a multiple alignment algorithm in [39] and [40].

#### 2.1.6. MACHINE LEARNING ALGORITHMS

Machine learning approaches are best suited for areas where there is a large amount of data but little theory[41]. Machine learning algorithms try to build a model from training data by deriving important insights about the parameter, which is often hidden. As the amount of training data increases, the accuracy of the machine learning algorithm typically increases as well. The parameters learned during training represents knowledge, while application of the algorithm to new data represents the algorithm's use of that knowledge.

Examples of machine learning algorithms used in bioinformatics include identification of structurally conserved residues[42], Support Vector Machine (SVM)-based MiRTif[43] and GIST[44].

#### 2.1.7. HEURISTIC ALGORITHMS

Heuristic algorithms do not guarantee that the optimal best solution will be found. Heuristic algorithms are typically used to solve problems with the following properties:

- Problems with large search spaces such that they cannot realistically be enumerated or searched exhaustively.

- There are no known methods for finding the best solution to the problems that do not employ a strategy that is fundamentally similar to exhaustive search.

Examples of heuristic algorithms used in bioinformatics include BLAST[45], FASTA[46], T-Coffee[47] and M-Coffee[48].

#### 2.2. SEQUENCE ALIGNMENT

Sequence alignment is one of the most popular sequence analysis tasks, in which two or more sequences are compared by searching for a series of substrings that are in the same order in the sequences. It is utilized to infer a relationship between the sequences and also gives an impression on how close they are in terms of sequence similarity. Hence, it is essential for discovering functional, structural and evolutionary information in biological sequences.

A list of key issues that are related to sequence alignment are identified in [49]. These key issues are summarized as follows:

- What type of alignment should be considered?

- What scoring system is used?

- What algorithm is used to obtain the optimal (or good) scoring alignments?

- What statistical methods used to evaluate the significance of an alignment score?

#### 2.2.1. TYPES OF ALIGNMENT

In general, sequence alignment can be categorized into two groups, i.e. pairwise sequence alignment and multiple sequence alignment.

#### 2.2.1.1. Pairwise sequence alignment

Consider the following pair of DNA sequences: **ATAGAC** and **ATTAGGC**. At a glance they look very much alike and this becomes more obvious when they are aligned together, as shown below.

A-TAGAC ATTAGGC

The differences lie in the extra T in the second sequence and a change from A to G in the second to last position. Note that a gap, marked with a "sign, is introduced in the first sequence in order to allow the bases before and after the gap to align perfectly. This is an example of a pairwise sequence alignment.

A pairwise sequence alignment is defined as an alignment of two sequences to determine how similar they are. In most sequence similarity calculations, a similarity score is inferred from the alignment. Gap insertions are allowed until the resulting sequences are of the same size and the alignment must obey the restriction that gaps cannot appear in the same position in both sequences. The example above satisfies the definition of an alignment.

Ideally, the alignment of two sequences should be in agreement with their evolution, i.e. the patterns of descent as well as molecular structural and functional evolution[50]. Unfortunately, the evolutionary traces are often very difficult to detect, e.g. amino acid mutations, insertions and deletions of residues, transposed gene segments and the like can blur the ancestral relationship beyond recognition. In the absence of observed evolutionary traces, pairwise sequence alignment is regarded as mimicking evolution best when the minimum number of mutations is used to arrive at one sequence to the other. An approximation of this is to find the highest similarity value determined from summing substitution scores along matched residue pairs minus any insertion/deletion penalties. Such alignment is generally called the optimal alignment.

Unfortunately, testing all possible alignments, including the insertion of a gap at each position of each sequence is unfeasible. For example, 10<sup>88</sup> possible alignments exists of a pairwise sequence alignment of 300 amino acid[33]. The number of calculations

managed to be reduced greatly by introducing gaps as assigned scoring values such that they can be treated in the same manner as the mutation of one residue to another. The technique to calculate the highest scoring or optimal alignment, generally known as the dynamic programming (DP) technique, has been introduced by Needleman and Wunsch[34] in 1970.

There are two basic types of sequence alignment: global alignment and local alignment. Global alignment implies the matching of sequences over their complete lengths, whereas with local alignment the sequences are aligned only over the most similar parts of the sequences, carrying the clearest trace of evolutionary relationship. It is no always clear which of the two alignments (global or local) is biologically the most meaningful. In general, where there is a large difference in the lengths of two sequences to be compared, local alignment should be included in the analysis.

The first pairwise algorithm for local alignment was developed by Smith and Waterman[33] in 1981 as an adaptation of the algorithm of Needleman and Wunsch. The Smith-Waterman technique selects the most similar region in each of the two sequences, which are then aligned. In 1987, Waterman and Eggert[51] generalized the local alignment routine by devising an algorithm that allows the calculation of user-defined number of top-scoring local alignments instead of only the optimal local alignment.

#### 2.2.1.2. Multiple sequence alignment

Multiple sequence alignment is an extension of pairwise alignment to incorporate more than two sequences at a time. Multiple alignment methods try to align all of the sequences in a given query set. Multiple alignments are often used in identifying conserved sequence regions across a group of sequences hypothesized to be

evolutionarily related. Ideally, in order to generate an accurate multiple alignments, indepth knowledge of the evolutionary and structural relationships within the family would have to be utilized. However, these information are often lacking or difficult to use. General empirical models of protein evolution[52] are widely used instead, but these can be difficult to use when sequences are less than 30% identical[53]. Furthermore, mathematically sound methods for carrying out alignments using the models can be extremely demanding in computer resources for more than a handful sequences[54]. Therefore, heuristic methods have been developed to be able to cope with practical datasets.

Progressive alignment method[55, 56] is the most commonly used heuristic method. It adds sequences one by one to the existing alignment to build a new alignment. Many implementations determine the order of the sequences to be added to the new alignment by using an approximation of a phylogenetic tree, which is often called a guide tree. The guide tree is constructed using the similarity of all possible pairs of sequences stored in the distance matrix. The disadvantage of the progressive alignment method is that it suffers from greediness. Errors made in the first alignments during the progressive procedure cannot be corrected later. Global sequence weighting schemes[57, 58] are introduced to minimize such alignment errors. However, such schemes carry the risk of propagating rather than reducing error when used in progressive multiple alignment strategies[59]. ClustalW[58, 60] is the most widely used progressive alignment implementation. Up to 2009, ClustalW has over 26,000 citations in the ISI Web of Science. ClustalX[61] is the graphical version of ClustalW. Other multiple sequence alignment methods include MUSCLE[62], T-Coffee[47], and PRALINE[63].

## 2.2.2. SCORING SCHEME

Aligning two or more sequences can produce multiple possible results. In order to determine which of those possible alignments are optimal alignments, a scoring scheme is required. In general, scoring schemes used in sequence alignment consists of substitution matrix and gap penalties.

#### 2.2.2.1. Substitution Matrix

Substitution matrix consists of substitution score terms for each aligned residue pair. The substitution score s(x,y) indicates the scores of aligning residue x with residue y. In the case of DNA,  $x,y \in \{A, G, C, T\}$  and in the case of proteins,  $x,y \in \{A, R, N, D, C, Q, E, G, H, I, L, K, M, F, P, S, T, W, Y, V\}.$

Various popular substitution matrices utilized in sequence alignments include:

## 2.2.2.1.1. Unitary Scoring Matrix

Early sequence alignment programs used unitary scoring matrix. A unitary matrix scores all residue matches as well as penalizes all mismatches with the same value, as shown in equation 1, where c and d are constants.

$$s(x, y) = \begin{cases} c, & \text{if } (x = y) \\ d, & \text{if } (x \neq y) \end{cases}$$

# **Equation 1. Unitary scoring matrix equation**

Although this scoring is sometimes appropriate for DNA and RNA comparisons, for protein alignments using a unitary matrix amounts to proclaiming ignorance about protein evolution and structure.

## **2.2.2.1.2. Log-odds ratio**

Log-odds ratio substitution matrix consists of individual scores s(x,y) for each aligned pair of residues. The value of s(x,y) is defined as the *odds ratio* between two probabilities that describe the probability that some residue x will change to residue y over time, as shown in equation 2.

$$s(x, y) = \log \frac{M_{xy}}{P_{y}}$$

**Equation 2. Log-odds ratio scoring matrix equation**

where  $M_{xy}$  is the probability that we expect to observe residues x and y aligned in homologous sequence alignments and  $P_y$  is the probability we expect to observe residue y on average in a random sequence.

#### 2.2.2.1.3. Point Accepted Mutation (PAM)

The PAM[64] matrix was developed by Margaret Dayhoff in the 1978. It is calculated by observing the differences in closely related proteins. The PAM1 matrix estimates what rate of substitution would be expected if 1% of the amino acids had changed. The PAM1 matrix is used as the basis for calculating other matrices by assuming that repeated mutations would follow the same pattern as those in the PAM1 matrix, and multiple substitutions can occur at the same site. Using this logic, Dayhoff derived matrices as high as PAM250. Example of the PAM250 matrix is shown in Figure 4.

R Ν D С 0 Ε G Η Ι L Κ M F Ρ S W Y В Ζ Х -20 0 -2 0 1 -2 -30 0 - 8Α 0 -1 -1-1-1 -31 1 1 -6 0 0 -2 2 -2 -33 0 0 R 6 Π -1-41 -1-3-40 2 -4-2 -10 -1-8 0 Ν 1 1 0 -2 -3 1 -2 -31 -2 -2 1 -8 0 -1-5 3 1 -4-3 -6 -13 -1 D 4 2 1 -2 0 0 -23 -8 -2 -5 12 -5 -5 -3-2 -6 -5-5 -4-3С -4-4-30 -2 -8 -2 -4-5 -3 -81 1 -5 2 - 13 - 2 - 21 -1 -50 - 10 -5 -3Ε 0 -11 3 2 4 0 1 2 0 -2 -5 -10 0 -7-2 3 3 -1 -1G -30 1 -3 -10 5 -2 -3 -4 -2 -3 -5 0 -7-5 1 1 0 0 0 - 1 - 80 - 2 - 2H - 12 2 1 -33 1 - 26 -2 -20 -1-1-30 -21 -2 -2 -2 -2 -2-35 2 -2 2 1 - 2 - 1-5 -1-2-2 0 -1-2 -2 -3 -3 -4 -6 -2 -3 -4 -2 -2 -2L -2 2 -32 - 3 - 36 4 -12 - 3 - 3 - 10 - 50 - 2 - 35 K -1 3 1 1 0 - 20 - 5 - 10 0 - 3 - 4 - 21 0 - 1 - 8-2 -3 -5 -1 -2 -3 -2 2 4 0 -2 -2-1 -4 -26 0 2 -2 -2 -1 -6 -4 -5 -5-5 -2 2 -5 F -3 -4-3 1 0 9 -5 -3-3 0 7 - 1 - 40 - 10 - 2 - 3-1 -2 -50 - 6Ρ 0 0 -1 -30 6 1 -11 -5 -10 - 1-8 0 S 0 0 0 - 10 1 -1 -1-3-2-31 -2-3-1Т -2 0  $^{-1}$ 0 1 -5 0 -2 0 0 -10 -33 -30 -1W -6 2 -4-7 -8 -5 -7-7 -3 -5 -2 -3 -4 0 - 6-2 -5 17 0 -6 -5 -6 -4 -5 -2 -40 - 4 - 4 - 50 -1 -1 -4 -2 7 -3 -30 10 -2 -3 -4 -2 2 0 - 2 - 2-2 -2 -2-1-2-2 2 -1 -1 -1 0 -6 -2 4 -2 -2 -1 2 3 - 41 - 2 - 30 0 - 5 - 3 - 2В 0 - 11 3 0 1 - 2 - 4-13 2 - 1 - 8Ζ 0 3 -5 2 -2 -30 - 2 - 50 1 3 0 0 -1-6 -4-2 2 3 3 -1 -8-1 -3 -1 -1 -1 -1 -1 -1 -1 -2 -1 0 0 -4-2 -1 -1 -1 -1

Figure 4. PAM250 matrix

## 2.2.2.1.4. Block Substitution Matrix (BLOSUM)

Dayhoff's methodology of comparing closely related species turned out not to work very well for aligning evolutionarily divergent sequences. Sequence changes over long evolutionary time scales are not well approximated by compounding small changes that occur over short time scales. The BLOSUM[52] series of matrices rectifies this problem. Henikoff and Henikoff constructed these matrices using multiple alignments of evolutionarily divergent proteins. The probabilities used in the matrix calculation are computed by looking at "blocks" of conserved sequences found in multiple protein alignments. These conserved sequences are assumed to be of functional importance within related proteins. To reduce bias from closely related sequences, segments in a block with a sequence identity above a certain threshold were clustered giving weight 1

to each such cluster. For the BLOSUM62 matrix, this threshold was set at 62%. Pair frequencies were then counted between clusters, hence pairs were only counted between segments less than 62% identical. One would use a higher numbered BLOSUM matrix for aligning two closely related sequences and a lower number for more divergent sequences. Example of the BLOSUM62 matrix is shown in Figure 5.

```

С

Q

Ε

G

Η

L

Κ

М

F

Ρ

S

γ

٧

В

Ι

0 - 2 - 2

-2

-1 -1 -3

-1

2

0

-4

-3

0 -2 -1

-5

0

-3

3

-2 -4 -3

-4 -2

-2

1

0 -3

-1

-2

-3

0 - 3 - 4 - 3

0 -1

1 -5 -5

9 -5

0

2 -2 -2 -5 -5 -1 -5 -5 -2

0 - 2

-6

-5 -5

C -1 -5 -4 -5 13 -4 -5 -4 -4 -2 -2 -5 -2 -4 -4 -1 -1

-3 -4 -1 -5 -5 -3 -6

0

8

3 -3

1 -4 -3

2

-1 -5 -2

0

-3 -2

-4

-1

-3

0

-5

7 -3

0 -5 -4

1 -3 -5 -2

-4 -3 -4

E -1

0

0

2

3

0 -1

1

0 - 3 - 1 - 2

-4 -3 -3

8 -3 -6 -5 -2 -4 -5 -3

0

-2

-4 -5 -5 -1 -3 -2

1 -2

-4

1

0 -3 11 -5 -4 -1 -2 -2 -3 -1

-3

-4

3 -5 -1

2

-4

2

I -2 -4 -5

-5

-2 -4 -5 -6 -5

6

0

-4

-4

-4

-2

4 -5 -5 -2

-4

-2 -3

-5

-5

-2 -3 -4 -5 -4

2

6

3

1

-4

-4

-2

-2

-2

1 - 5 - 4 - 2

1 -2 -1 -4 -4

0 -1 -4 -3 -3 -1

0 - 1 - 5

2

7 -2 -5 -2

M -1 -2 -3 -5 -2 -1 -3 -4 -2

3 -2

8

0 - 4 - 2

9 -5 -4 -3

F -3 -4 -4 -5 -4 -5 -5 -5 -2

0

1 -5

0

4 -1 -5 -5 -2 -6

1

-1 -3 -3 -2 -4 -2 -2 -3 -3 -4 -4 -2 -4 -5 11 -1 -2 -5

-4 -4 -3 -2 -2

0 -2 -4 -1

2 -1

0 -1

0

0

0 -1 -4 -4

6

2

-4 -3 -2

0

0 -1

0 -2 -1 -1 -1 -2 -3 -1 -2 -1 -1 -3 -2

2

7

-4 -2

W -4 -4 -6 -6 -3 -3 -4 -4 -4

-4 -2

-4 -2

1 - 5 - 4

-4 16

3 -4 -6 -4 -3

Y -3 -3 -3 -5 -4 -2 -3 -5

3 -2 -2 -3 -1

4 -4 -3 -2

3 10 -2 -4 -3 -2

-4 -4 -5

-1 -3 -4 -5 -5

4

1

-3

1 -1

-4

-2

-4

-5

Ο

1 - 1 - 1 - 5

-5

-1 -4 -5 -3

Ο

-4 -5

1 -5

0 - 5 - 4

1 -2 -5 -2

5

6 -3

0 -1 -4 -3 -4

X -1 -2 -2 -2 -3 -1 -1 -2 -2 -2 -1 -1 -2 -2 -1 -1 -3 -2 -1 -2 -1 -2 -6

```

Figure 5. BLOSUM62 matrix

#### 2.2.2. Gap Penalties

Gaps are expected to be penalized in an alignment. The standard gap penalty w(k) associated with a gap of length k can either be given by a linear penalty or an affine penalty. Equation 3 shows the linear gap penalty equation.

$$w(k) = g \cdot k$$

**Equation 3. Linear gap penalty equation**

Affine gap penalty introduces the concept of gap open and gap extension penalty. Equation 4 shows the affine gap penalty equation, where h is the gap open penalty and g is the gap-extension penalty.

$$w(k) = h + g \cdot k$$

# **Equation 4. Affine gap penalty equation**

## 2.2.3. ALIGNMENT ALGORITHMS

Below we introduce several basic types of alignment algorithms.

# 2.2.3.1. Global alignment: Needleman-Wunsch algorithm

The Needleman-Wunsch algorithm[34] is a dynamic programming algorithm, that obtains the optimal global alignment between two sequences, allowing gaps. Gotoh[65] modified the algorithm to run at O(mn) complexity by considering affine gap penalties.

The main idea of this algorithm is to build up an optimal alignment using previous solutions for optimal alignments of smaller subsequences. Given a matrix M and two sequences  $\mathbf{X} = \{x_1, x_2, ..., x_m\}$  and  $\mathbf{Y} = \{y_1, y_2, ..., y_n\}$ , M(i,j) is the score of the best alignment between the segments  $x_1...i$  up to  $x_i$  and  $y_1...j$  up to  $y_j$ . Hence, M(0,0) is initialized to be 0 and M(i,j) is then build recursively.

The value of M(i,j) could only be calculated if the values of M(i-1,j-1), M(i-1,j) and M(i,j-1) are known. There are three possible ways that the best score M(i,j) of an alignment up to  $x_i$ ,  $y_i$  could be obtained:

- $x_i$  is aligned to a gap, in which case M(i,j) = M(i-1,j) g

- $y_i$  is aligned to a gap, in which case M(i,j) = M(i,j-1) g

•  $x_i$  is aligned to  $y_i$ , in which case  $M(i,j) = M(i-1,j-1) + sub(x_i,y_i)$

where g is the gap penalty and sub  $(x_i, y_j)$  is the substitution score of aligning residues  $x_i$  and  $y_j$ . The best score up to (i,j) will be the largest of these three options. Therefore, we have following equation:

$$M(i,j) = \max \begin{cases} M(i-1,j-1) + sub(x_i, y_j), \\ M(i-1,j) - g, \\ M(i,j-1) - g \end{cases}$$

**Equation 5. Needleman-Wunsch equation**

Initialization values are given as the following: for  $0 \le i \le m$ ,  $M(i, 0) = -i \cdot g$  and for  $0 \le j$   $\le n$ ,  $M(0, j) = -j \cdot g$ . Equation 5 is repeatedly applied to fill in the matrix of M(i,j) values, calculating the value in the bottom right-hand corner of each square of four cells from one of the other three values (above-left, above, or left), as shown in Figure 6.

Figure 6. Data dependency in Needleman-Wunsch algorithm

The most bottom right cell of the matrix M(m,n) is the score of the best global alignment for an alignment of **X** and **Y**. A *traceback* procedure is needed to determine the actual alignment(s) from the corresponding score. The traceback for the Needleman-Wunsch algorithm starts from the cell with the best score M(m, n) to M(0, 0).

## 2.2.3.2. Local alignment: Smith-Waterman algorithm

A lot of biological problems, e.g. search for a common domain between two protein sequences, comparison of extended sections of genomic DNA sequences and similarity detection between two very divergent sequences, require us to look for the best alignment between subsequences. Such alignment is called local alignment. The Smith-Waterman algorithm[33] is a dynamic programming algorithm, that obtains the optimal local alignment between two sequences.

The algorithm is closely related to the global alignment algorithm. There are, however, two main differences. The first is that the value of M(i,j) will be 0 if its value is 0 or less. Taking the option 0 basically corresponds to starting a new alignment. If the best alignment up to a certain point reaches a negative score, a new alignment is preferred, rather than continue and extend the old one. This is reflected in Equation 6.

$$M(i,j) = \max \begin{cases} 0, \\ M(i-1,j-1) + sub(x_i, y_j), \\ M(i-1,j) - g, \\ M(i,j-1) - g \end{cases}$$

# **Equation 6. Smith-Waterman equation**

The second difference is that the best score of the alignment is no longer M(m,n), but it is the cell with the highest value of M(i,j) over the whole matrix. That particular cell indicates where the alignment ends.

Further details of the Smith-Waterman algorithm will be elaborated in Chapter 4.

# 2.2.3.3. Algorithms with affine gap penalty

The simplest gap model implemented in most algorithms is a simple multiplication of the length with the gap penalty. This type of model, however, is not ideal for biological sequences. In the real world, when gaps do occur, they are more likely to have a large gap, rather than many small gaps. For example, a biological sequence is much more likely to have one big gap of length k, due to a single insertion or deletion event, than it is to have k small gaps of length 1.

To account for this tendency, affine gap penalty is introduced. Affine gap penalty consists of a gap opening penalty,  $\alpha$ , and a gap extension penalty,  $\beta$ . A gap of length k would then have an affine gap penalty  $w(k) = \alpha + (k-1)\beta$ . The value of  $\alpha$  and  $\beta$  are usually always negative because gap extension are encouraged, rather than gap introduction.

## 2.2.3.4. Heuristic alignment algorithms

All the alignment algorithms described so far produce optimal result. However, they are not the fastest methods and in some cases, speed is an issue. Heuristic alignment algorithms offer fast solutions with a trade off of accuracy and sensitivity. The goal of these methods is to search as small a fraction as possible of the cells in the dynamic programming matrix, while still looking at all the high scoring alignments. Two of the best-known algorithms are the Basic Local Alignment Search Tool (BLAST)[45] and FAST-All (FASTA)[46].

# 2.2.3.4.1. BLAST

The BLAST package[45] provides programs for finding high scoring local alignments between a query sequence and a database. The sequences can either be DNA or protein sequences. The main idea of the BLAST algorithm is that true match alignments are very likely to contain within them a short stretch of identities or very high scoring matches. Such short stretches are called seeds, from which they are extended out in search of a good longer alignment.

**Table 1. Traditional BLAST Programs**

| Program | Query                              | Database                           | Typical Usage                                                                                                                        |

|---------|------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| BLASTN  | Nucleotide                         | Nucleotide                         | Mapping oligonucleotides, cDNAs and PCR products to a genome; screening repetitive elements; annotating genomic DNA; vector clipping |

| BLASTP  | Protein                            | Protein                            | Identifying common regions between proteins; collecting related proteins for phylogenetic analysis                                   |

| BLASTX  | Nucleotide translated into protein | Protein                            | Finding protein-coding genes in genomic DNA; determining if a cDNA corresponds to a known protein                                    |

| TBLASTN | Protein                            | Nucleotide translated into protein | Identifying transcripts from multiple organisms; mapping a protein to genomic DNA                                                    |

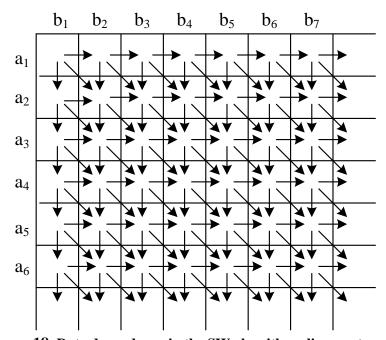

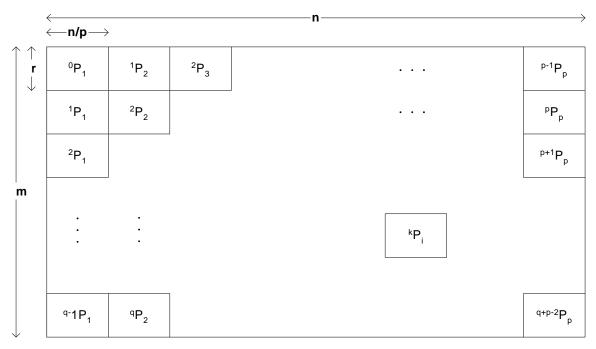

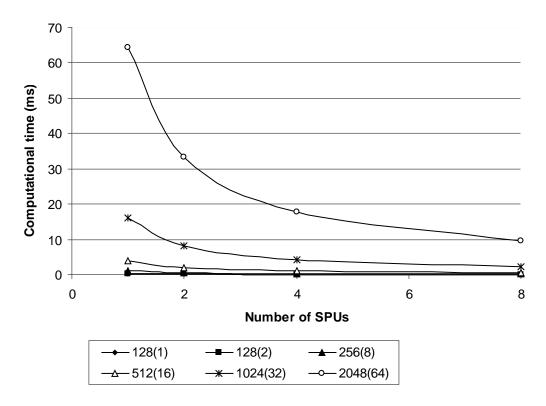

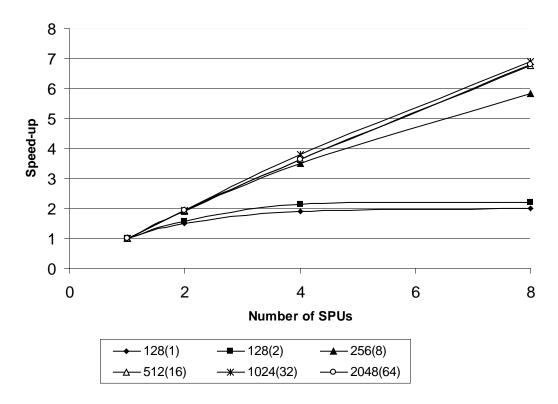

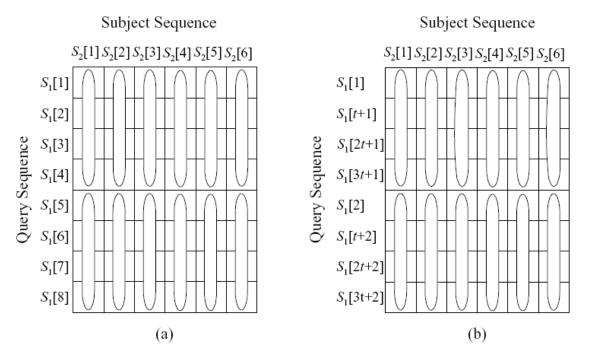

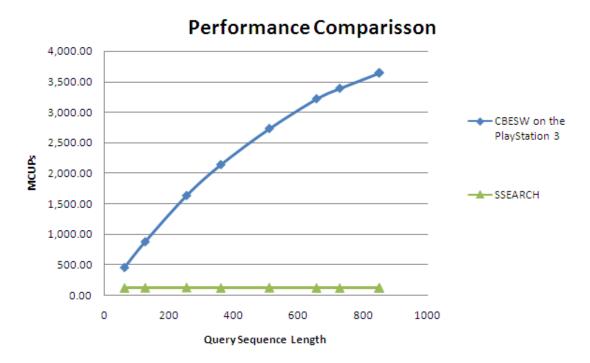

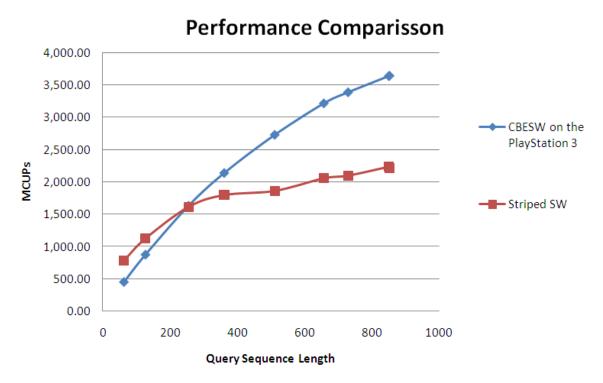

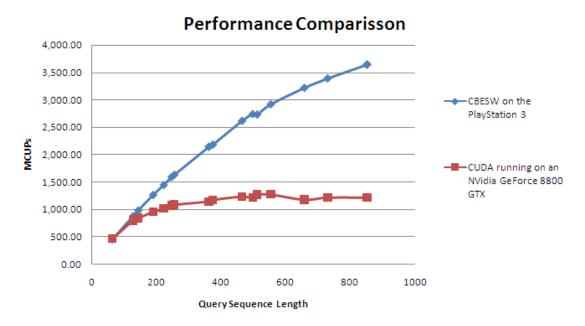

| TBLASTX | Nucleotide translated into protein | Nucleotide translated into protein | Cross-species gene prediction at the genome or transcript level                                                                      |