## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# A novel sampling process with low harmonic distortion for a digital class D amplifier

Fang, Yu

2005

Fang, Y. (2005). Novel sampling process with low harmonic distortion for a digital class D amplifier. Master's thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/4243

https://doi.org/10.32657/10356/4243

Nanyang Technological University

Downloaded on 09 Apr 2024 11:03:38 SGT

## A Novel Sampling Process with Low Harmonic Distortion for a Digital Class D Amplifier

## Fang Yu

## School of Electrical & Electronic Engineering

A thesis submitted to the Nanyang Technological University

in fulfillment of the requirement for the degree of

Master of Engineering

2005

TK 7871.2 F211 2005

## **Statement of Originality**

I hereby certify that the work embodied in this thesis is the result of my original research and has not been submitted for a higher degree to any other University or Institution.

19/12/2005 Date Fang Yu

## Acknowledgments

I owe a great gratitude to my supervisor A/P Joseph Chang and to Ast/P Gwee Bah Hwee for their invaluable guidance, helpful suggestions and persistent encouragement throughout the study. Their broad knowledge and enthusiasm have a lasting effect on me. Their kindness and patience are also deeply appreciated.

I would like to express my gratitude to Ast/Prof Tan Meng Tong for his inspiration and guidance. I would also thank Dr. Gu Jiangmin for his useful suggestion and encouragement.

I also wish to express my appreciation for the help provided by other graduate students and research staffs. In particularly, I would like to thank Mr. Chong Kwen Siong, Mr. Adrian Victor, Mr. Yang Jingbo and other postgraduate candidates in our research group for their constant help in my project. They are nice enough to share their invaluable knowledge and experience with me. The assistance provided by all the technicians in Integrated System and Research Lab 1 is highly appreciated.

Finally, from the bottom of my heart, I want to thank my parents for their love and support.

#### Abstract

Digital Class D amplifiers offer the advantages of higher power efficiency and reduced hardware (when connected to a digital input source) compared to conventional classical linear amplifiers such as Class A and Class AB amplifiers. These attributes are particularly advantageous in applications whose critical parameters include micropower low-voltage operation and small integrated circuit (IC) area.

In this dissertation, we investigate the sampling processes and pulse generators for a Pulse Width Modulator (PWM) for a digital Class D amplifier. The emphases of the Class D amplifier design are micropower operation, small IC area and low We propose a novel sampling process, termed 'Second-Order harmonic distortion. This sampling process requires three sampled Polynomial' sampling process. points and aims to emulate the Natural Sampling process. We derive the double Fourier series expression for the proposed sampling process to analytically determine the non-linearity of the sampling process. We show that the derivation is correct by comparing it against the time-domain expression. The double Fourier series expression is also useful as it provides insight to a designer on how different parameters for a given design may be compromised to meet its specifications.

We compare our Second-Order Polynomial sampling process against the prevalent Delta-Compensation ( $\delta$ C) and Linear Interpolation (LI) sampling processes. We show that the Second-Order Polynomial sampling features lower harmonic distortion. Although the drawback of the Second-Order Polynomial sampling process is the slight increase in computation, its reduced non-linearity is worthwhile.

We synthesize the hardware for the PWM, including the Second-Order Polynomial process and pulse generator, and investigate various design variations.

## List of Symbols

signal harmonic index n carrier harmonic index m signal frequency  $\omega_{\nu}$ carrier frequency  $\omega_c$ modulation index  $(0 \le M \le 1)$ M Bessel function of first kind, with order n $J_n$ DC bias of modulating signal k sampling ratio  $(\omega_c/\omega_v)$ p pulse duration  $t_p$ Tsampling period current sampling point  $S_1$ previous sampling point before  $S_I$  $S_0$  $S_2$ next sampling point after  $S_I$ SNS Natural sampling point Linear Interpolation sampling point  $S_{LI}$ Uniform sampling point  $S_{UN}$ Delta-compensation sampling point  $S_{\infty}$ variable sampling factor of Enhanced Sampling Process  $\varepsilon$ Second-Order Polynomial sampling point  $S_{sop}$ mean square value of quantization noise eRMS Е spectrum density of noise = input signal bandwidth

$f_0$

$f_s$  = sampling frequency

a, b, c (A, B, C) = coefficient of the second order polynomial function

$t_{sop}$  = pulse duration of the second order polynomial sampling point

$K_{mn}$  = double Fourier series coefficient

$A_{mn}$  = cosine component of double Fourier series coefficient

$B_{mn}$  = sine component of double Fourier series coefficient

$\Delta$  = amplitude difference between  $S_1$  and  $S_2$

## **List of Figures**

| Figure 2.1  | A digital Class D amplifier8                                            |

|-------------|-------------------------------------------------------------------------|

| Figure 2.2  | Classification of Pulse Width Modulations: (a) Leading edge modulation, |

|             | (b) Trailing edge modulation, and (c) Double edge modulation14          |

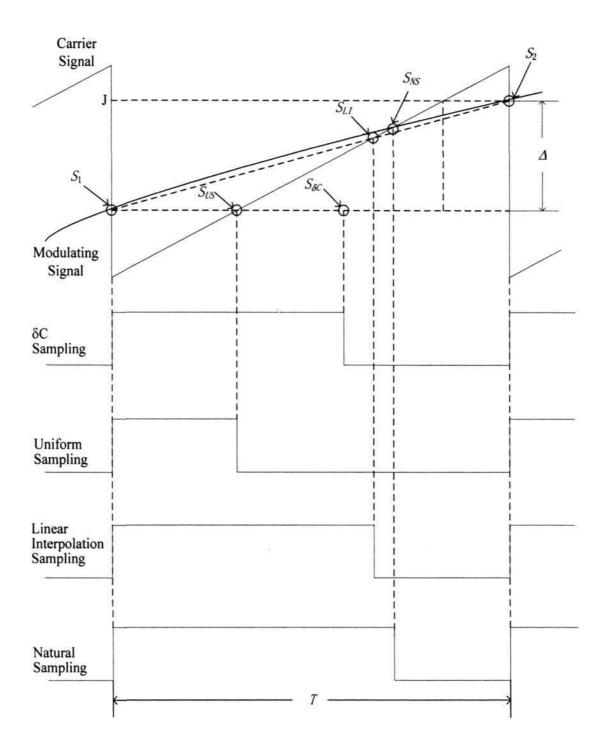

| Figure 2.3  | The Natural, Uniform, Delta-Compensation and Linear Interpolation       |

|             | sampling processes                                                      |

| Figure 2.4  | Enhanced sampling based on LI [Mellor et. al., 1991]22                  |

| Figure 2.5  | Third order interpolation polynomial approximation24                    |

| Figure 2.6  | Illustration of pulse edge placement error in                           |

| WPWM        | 25                                                                      |

| Figure 2.7  | PCM to single-edge NPWM conversion algorithms27                         |

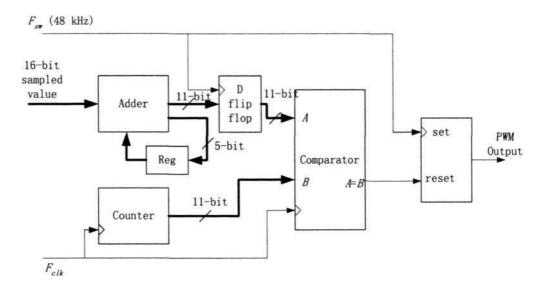

| Figure 2.8  | Fast-clock-counter based PWM pulse generator31                          |

| Figure 2.9  | Tapped-delay-line base PWM pulse generator31                            |

| Figure 2.10 | Hybrid counter-delay-line pulse generator33                             |

| Figure 2.11 | Relationship between power dissipation and counter bits of PWM pulse    |

|             | Generator34                                                             |

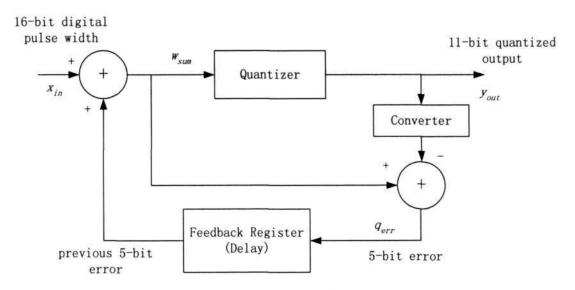

| Figure 2.12 | 16-bit to 11-bit 1 <sup>st</sup> order noise shaper35                   |

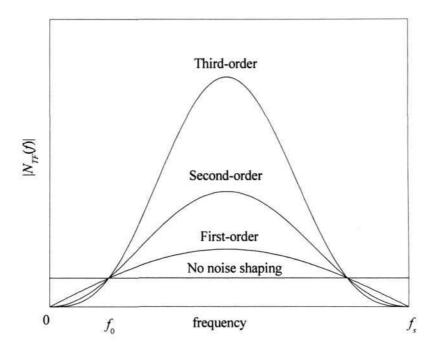

| Figure 2.13 | Some different noise-shaping transfer function38                        |

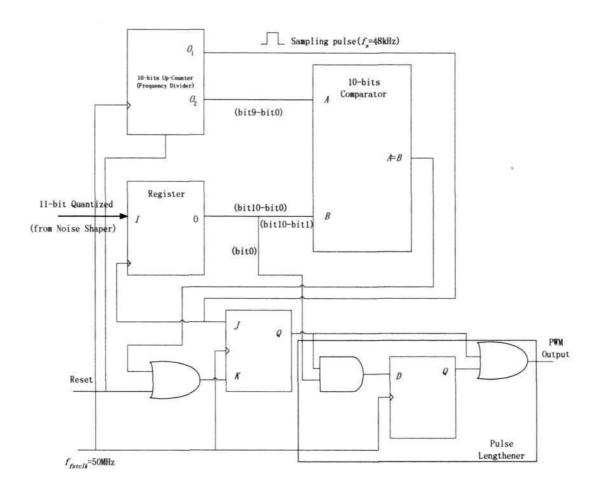

| Figure 2.14 | Block diagram of the 10-bit counter, comparator, and the 1-bit          |

|             | frequency doubler39                                                     |

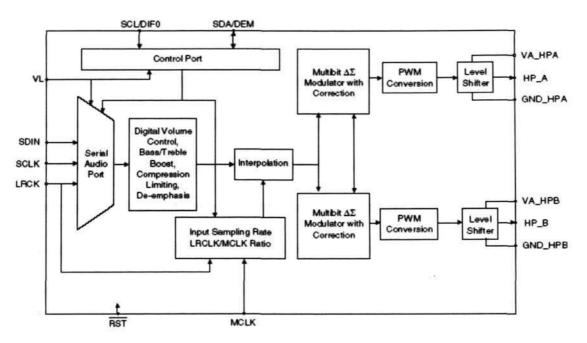

| Figure 2.15 | The CS44L10 digital-to-PWM Class D audio amplifier system               |

|             | Controller4                                                             |

| 2           |                                                                         |

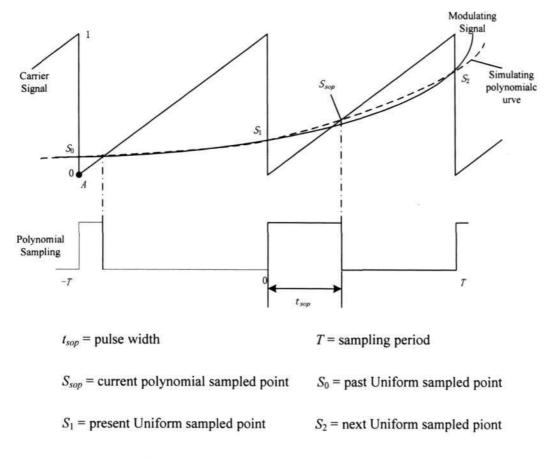

| Figure 3.1  | Polynomial Sampling process                                             |

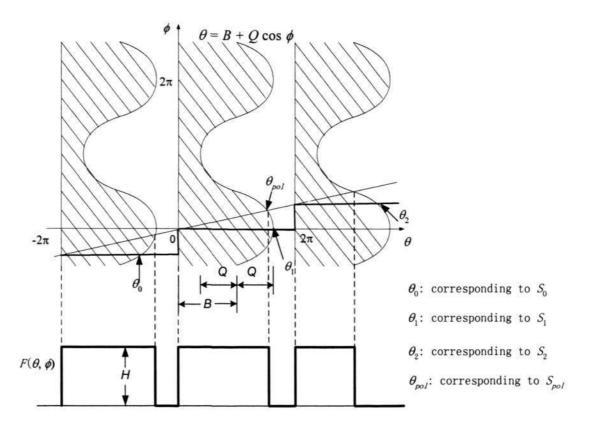

| Figure 3.2  | Spectrum analysis by double Fourier series                              |

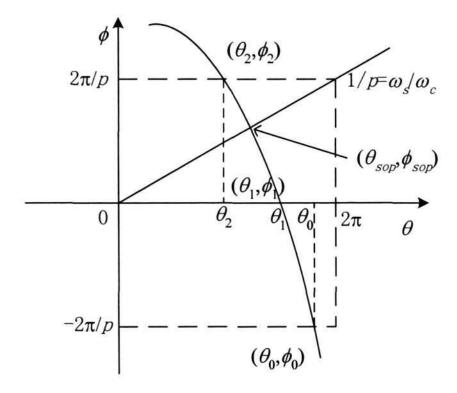

| Figure 3.3  | Detailed illustration of the Second-Order Polynomial single-sided       |

|             | trailing edge PWM sampling53                                            |

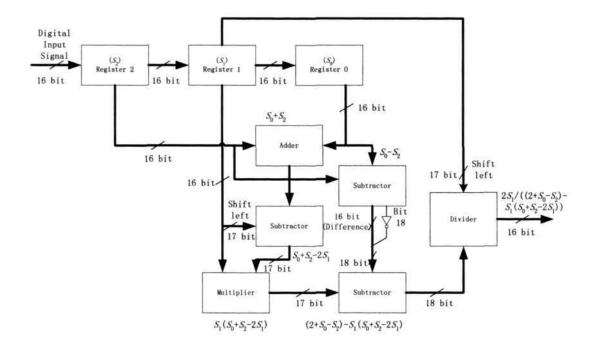

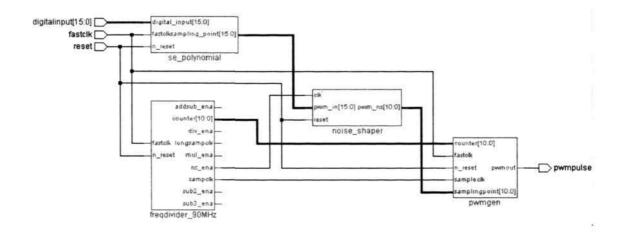

| Figure 4.1  | Block diagram of the Second-Order Polynomial sampling process63         |

| Figure 4.2 | WM pulse generator structure65                                     |

|------------|--------------------------------------------------------------------|

| Figure 4.3 | Circuitry of Polynomial PWM67                                      |

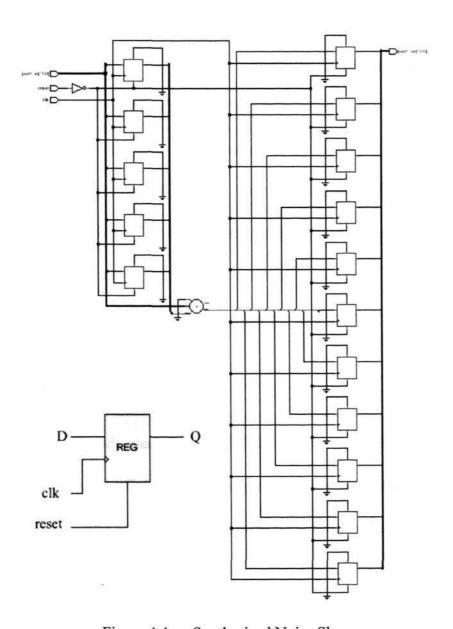

| Figure 4.4 | Synthesized Noise Shaper67                                         |

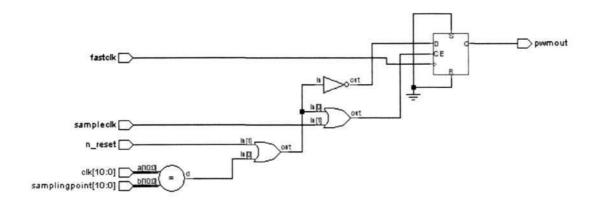

| Figure 4.5 | Synthesized pulse generator based on Fast-Clock Counter approach68 |

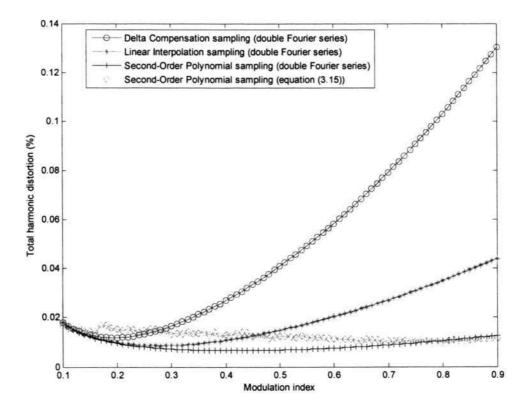

| Figure 4.6 | THD of different sampling processes based on double Fourier series |

|            | Expressions69                                                      |

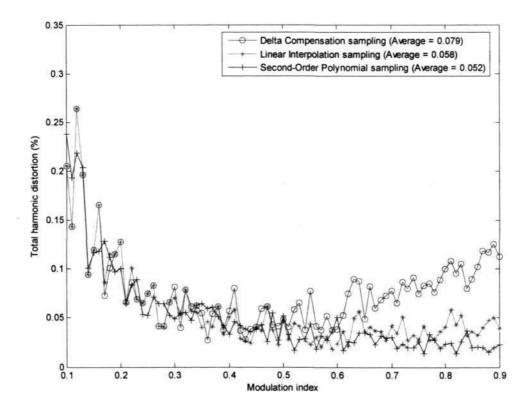

| Figure 4.7 | The THD comparison between different sampling processes using time |

|            | domain expressions and with 11-bit pulse generator                 |

| res        | olution72                                                          |

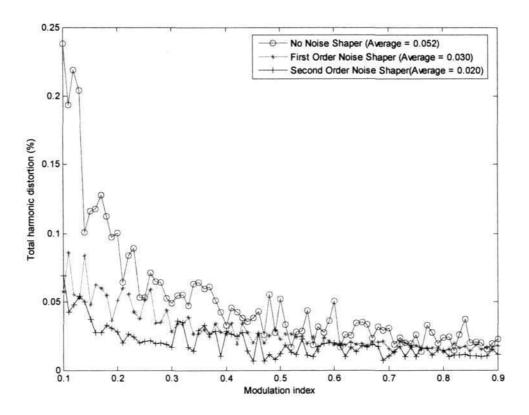

| Figure 4.8 | THD comparison of noise shaper effect (11-bit resolution)73        |

## **List of Tables**

| Table 1.1 | Specifications of the design parameters                      | 5  |

|-----------|--------------------------------------------------------------|----|

| Table 4.1 | Comparison of calculation complexity for different processes | 71 |

## **Table of Contents**

| Acknow    | ledgem  | nents                                         | i    |

|-----------|---------|-----------------------------------------------|------|

| Abstrac   | t       |                                               | ii   |

| List of S | Symbols | ls                                            | iii  |

| List of I | Figure  |                                               | v    |

| List of T | Гable   |                                               | vii  |

| Table of  | f Conte | ents                                          | viii |

| Chapter   | r1 In   | troduction                                    | 1    |

|           | 1.1     | Application of Power Amplifiers               | 1    |

|           | 1.2     | Motivations                                   | 2    |

|           | 1.3     | Objectives                                    | 4    |

|           | 1.4     | Major Contributions                           | of   |

|           | T       | hesis5                                        |      |

|           | 1.5     | Thesis Organizations                          | 6    |

| Chapte    | r 2 Li  | iterature Review                              | 7    |

|           | 2.1     | Introduction                                  | 7    |

|           | 2.2     | Review of Different PWM Sampling Processes    | 13   |

|           | 2.2     | 2.1 PWM signals                               | 13   |

|           | 2.2     | 2.2 Total Harmonics Distortion (THD)          | 15   |

|           | 2.2     | 2.3 Overviews of Different Sampling Processes | 15   |

|           |         | 2.2.3.1 Natural Sampling Process              | 18   |

|          | 2.                                   | 2.3.2 Uniform Sampling Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 2.                                   | 2.3.3 Algorithm-based Sampling Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3      | R                                    | eview on other reported sampling processes22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 99<br>98 | 2.3.1                                | Enhanced Sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 52<br>22 | 2.3.2                                | Pseudonatural PWM (PNPWM)23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          | 2.3.3                                | Weighted Pulse Width Modulation (WPWM)24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | 2.3.4                                | PCM to Single-Edge NS Conversion27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.4      | R                                    | eview on PWM pulse generators29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          | 2.4.1                                | Fast-Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cou      | ınter                                | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 2.4.2                                | Counter-Delay-Line31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 2.4.3                                | Hybrid Counter-Delay-Line32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          | 2.4.4                                | Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Sha      | ping                                 | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 2.4.5                                | Frequency Doubler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.5      | D                                    | Oelta-Sigma ( $\Delta\Sigma$ ) Modulator40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | 2.5.1                                | Introduction40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          | 2.5.2                                | Applications41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.6      | C                                    | Conclusions42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3        | Prop                                 | osed Second-Order Polynomial Sampling Algorithm43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1      | Iı                                   | ntroduction43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2      | P                                    | roposed Polynomial Sampling Algorithm43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | 2.4<br>Cou<br>Sha<br>2.5<br>2.6<br>3 | 2.3.1 2.3.2 2.3.3 2.3.4 2.4.1 Counter 2.4.2 2.4.3 2.4.4 Shaping 2.4.5 2.5.1 2.5.2 2.6 C 3 Proposition of the proposition |

| 3.3       | Spectrum Analysis for the Second-Order Polynomial Sampling49 |

|-----------|--------------------------------------------------------------|

| 3.4       | Conclusions61                                                |

| Chapter 4 | Hardware Description and Simulation Results62                |

| 4.1       | Introduction62                                               |

| 4.2       | Hardware Description of the Second Order Polynomial          |

|           | Sampling Process62                                           |

| 4.3       | Simulation Results Based on Double Fourier Series and        |

|           | Time-domain Expression68                                     |

| 4.4       | Simulations Results Based on Synthesized Hardware71          |

| 4.5       | Conclusions74                                                |

| Chapter 5 | Conclusions and Recommendation for Future                    |

|           | Work75                                                       |

| 5.1       | Conclusions75                                                |

| 5.2       | Recommendation for Future Work                               |

| Reference | 79                                                           |

## Chapter 1 Introduction

## 1.1 Applications of Power Amplifiers

Traditionally audio amplifiers are linear analogue amplifiers whose transistors operate in the linear region, and are typically Class A or Class AB; Class B is generally avoided due to its gross crossover distortion. These linear amplifiers have low power efficiency – Class A amplifiers (bridge output) have a maximum power efficiency of 50% [Gray and Hurst, 2000] while Class AB have a maximum efficiency between 50% and 78.5%, depending on the biasing. The maximum efficiency of these linear analogue amplifiers is when the signal swing is largest and this is not the usual operating condition of the amplifiers. Consequently, in practice, these linear amplifiers have substantially lower efficiencies, typically 10%-30% because the nominal signal swing is usually substantially lower than the maximum swing, that is where the crest factor is high. As the power efficiency is low, much of the wasted power is dissipated as heat. These amplifiers, if they are high power, are hence usually large (and heavy) due to the added heat sinks required to safely dissipate the heat.

With the advent of digital technology and in particular digital audio sources, it is highly desirable to perform audio power amplification directly in the digital domain, as opposed to usual approach of digital-to-analogue conversion followed by a linear analogue power amplifier. Audio amplifiers, both digital and analogue, using Class

D output stages tend to have higher power conversion efficiency, largely due to the fact that the output transistors therein operate digital-like, that is either in the ohmic or cut-off regions [Tan et. al., 2003].

Digital audio devices are now prevalent and are found in living rooms, broadcast studios, cars, etc. These include compact discs (CD), mini-discs (MD), MP3, DVDs, etc, and many of these devices are portable. In an audio system, the power amplifier is often used to offer the necessary gain and drive to the output load. these audio systems, particularly portable devices, it is desirable to obtain the power efficiency to be as high as possible to enable the device with a sufficiently long The digital Class D amplifier is particularly advantageous in these battery life. applications because when properly designed, it features high power efficiency (of the order of 90%) over a large modulation index range (signal swing), and at the same time, can feature low non-linearities (for example the Total Harmonic Distortion The digital Class D amplifier is also advantageous when (THD) < 0.5%). interfaced to a digital processor (for example, in a digital hearing instrument (hearing aid) and the like) because the need for a digital-to-analogue (D/A) converter is eliminated, hence the immediate power savings and reduced hardware.

#### 1.2 Motivation

An increasing number of portable audio devices, including devices with critical power considerations such as hearing instruments, employ Class D amplifiers, primarily

because when appropriately designed [Chang et. al., 2000], Class D amplifiers can feature high power efficiency, greater than 90% over a wide range of signal swing (modulation index, M).

Class D amplifiers may be generally classified into two groups: Analogue and Digital amplifiers. Analogue Class D amplifiers are perhaps more conventional and are semi-analogue circuits, in the sense that the modulation process, usually the Pulse Width Modulation (PWM) process, employs an analogue comparator and the input is an analogue (modulating) signal. It is probably of interest to note that other methods of modulation (for an analogue Class D amplifier) include Sigma Delta Modulation [Candy and Themes, 1992], and more recently Bang-Bang Control Modulation [Takagishi, 2002]. However, the PWM approach is most prevalent. This is largely due to the simplicity of the required hardware for the PWM, in particular where power is a critical parameter, for example in hearing instrument When these analogue Class D amplifiers are interfaced to a digital applications. signal processor (DSP), a D/A conversion is required to obtain the modulating analogue signal.

The current-art method would be to directly employ a digital Class D amplifier, thereby eliminating the need for the D/A converter, hence a more hardware efficient design. Furthermore, a digital Class D amplifier offers greater programmability and repeatability (more tolerant to fabrication process variations), easier (direct)

interface to digital processors and a higher immunity to noise [Gwee et. al., 2002]. As in the analogue Class D amplifier, there are also a number of modulation techniques and they include Sigma Delta [Melanson, 1998] and the Click Modulation [Logan, 1984], in addition to PWM. However, both the Sigma Delta and the Click Modulation methods are substantially more complex than the PWM and consequently dissipate higher power [Gwee et. al., 2003]. In view of the objectives of this research work that pertains to the power critical applications, in particular the hearing instrument, we will restrict our work to a Class D amplifier based on the PWM approach.

In Chapter 2, we will review the different modulation methods, including the different sampling processes for the PWM approach. In view of these sampling processes, there is a need for a simple sampling process (for low power dissipation considerations) that also features low non-linearity, particularly low THD (< 0.1%).

In summary, the motivation of this research is to design a micropower low-distortion digital PWM process for digital Class D amplifiers.

## 1.3 Objectives

The objective of this project is to investigate the design of a micropower low-voltage and low THD digital Class D power amplifier and its implementation for low-voltage power-critical applications, including digital hearing instruments. Specifically, the

#### design parameters are:

Table 1.1 Specifications of the design parameters

| Voltage                  | 1.1 V         |

|--------------------------|---------------|

| Carrier Signal Frequency | 44.1 kHz      |

| Data Bandwidth           | 20 Hz - 4 kHz |

| Internal Frequency       | <100 MHz      |

| Power dissipation        | <100 μW       |

| Signal Noise Ratio (SNR) | >80 dB        |

| THD                      | <0.1%         |

To be specific, the objective of this project is to propose a novel sampling process and its subsequent implementation to achieve micropower operation and with low non-linearities, for a low voltage Class D amplifier. The further objective is to analytically derive the double Fourier series expression for the proposed sampling process, and its subsequent verification.

## 1.4 Major Contribution of Thesis

This dissertation presents the analysis, design and implementation of a micropower, low-voltage and low distortion digital pulse width modulator for a digital Class D amplifier. The major contributions of this thesis are:

A novel digital sampling process, specifically the Second-Order Polynomial sampling process is proposed, and thereafter simplified and implemented; The double Fourier series mathematical expression of the proposed

Polynomial sampling process to depict the frequency components of the sampling process is derived and verified.

## 1.5 Thesis Organization

In this chapter, we have described the motivation, objectives and major contributions of this research programme. The remaining chapters of this dissertation are organised as follows. Chapter 2 provides an overview of reported PWM generating approaches, PWM sampling processes and PWM pulse generators of Class D amplifiers. Chapter 3 describes the proposed Polynomial Sampling and its spectrum analysis. Chapter 4 describes hardware description of the proposed sampling process, and provides the simulation results. Chapter 5 concludes this dissertation and lists several directions for future work.

## **Chapter 2** Literature Review

#### 2.1 Introduction

The methods for generating the PWM signal for a digital Class D amplifier may be classified into three general approaches: (i) algorithmic PWM, (ii) oversampled Delta-Sigma ( $\Delta\Sigma$ ) PCM (Pulse-Code Modulation)-PWM, and (iii) Click Modulation [Logan, 1984]. The first two methods are popular while the last remains largely academic due to its complexity. In view of this, we will only review in detail digital Class D amplifiers based on the first two approaches.

We will now briefly describe an overview of the three approaches and thereafter provide a somewhat comprehensive review of the formal two approaches. This review provides a good perspective of our proposed sampling process and its simplification (and subsequent implementation).

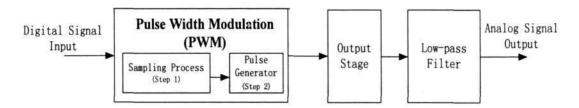

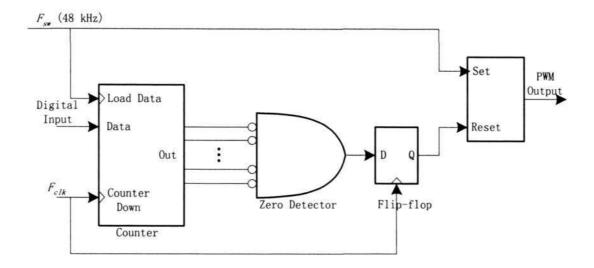

Figure 2.1 depicts a block diagram of a generic digital Class D amplifier based on algorithmic PWM. The input is the output of a digital source whose data is read from a digital medium such as a CD, digital audio tape (DAT), digital versatile disc (DVD), a digital communications receiver, etc. The first step in digital amplification is a sampling process to determine the digital value of the pulse width that is equivalent to the amplitude of the modulating signal sampled by the carrier. The second step is to generate the corresponding modulated pulses based on the

digital value provided by the sampling process. The output stage is a cascade of inverters whose transistors have increasing aspect ratios where the final output transistors have a low output impedance, typically  $<30\Omega$ . This stage provides sufficient drive ability to drive a low impedance load (subminiature hearing instrument receiver), typically  $<600\Omega$ . The low-pass filter removes the carrier components (pulses from the pulse generator) and delivers the amplified input equivalent in analogue form to the output device. In audio application systems, the output device is usually a loudspeaker.

Figure 2.1 A digital Class D amplifier

The Pulse Width Modulation is the fundamental component of a Class D amplifier, which produces a train of pulses having widths corresponding to the level of input modulating signal. It is composed of two stages: sampling process and pulse generation.

The algorithmic PWMs essentially involve a signal sampling process to digitally emulate the Natural Sampling (NS) process, followed by a pulse generator. This signal sampling process is sometimes termed the cross-point deriver and as its name

implies, the process simply involves estimating the cross-point or intersection of the modulating signal and the carrier signal - the NS process, see later in this chapter.

One of impetuses for the wealth of reported algorithmic PWM sampling processes in literature is the desire for a low distortion PWM output (THD < 0.5%) with a low sampling rate (for example,  $f_s = 48 \text{ kHz}$ ) and with modest computation complexity (for example, 2 additions/subtractions and 1 division operation per sample). These attributes are highly desirable in view of micropower operation for power critical portable applications and devices such as hearing instruments. This is because a high sampling frequency, increased computation rate arising from more samples per unit time and the corresponding higher clock rate in the pulse generator, all translate to undesirable higher power dissipation. Further, a low computation complexity translates to simpler hardware, hence lower cost and usually higher reliability.

The reported sampling processes for the algorithmic PWM methods include the Linear Interpolation (LI) [Mellor et. al., 1991; Goldberg and Sandler, 1994], Pseudo-Natural PWM [Goldberg and Sandler, 1994], Static-Filter PWM [Risbo and Morch, 1998], Weighted PWM and its variants [Johansen and Nielsen, 1999], Derivative PWM [Song, 2001], Parabolic Correction PWM [Pascual and Roeckner, 2000], Prediction Correction PWM [Roeckner et. al., 2003; Midya et. al., 2000] and more recently, the Delta Compensation (8C) PWM [Gwee et. al., 2002] sampling processes from our research group. At the outset, we remark that the LI process offers low

non-linearities with very modest computation complexity and with low sampling rate.

The other processes may offer lower non-linearities but at the high cost of substantially more complex computation and in some cases, requiring a higher sampling rate. We will qualify and quantify these parameters and briefly describe these different algorithmic sampling processes in our review in this chapter.

For completeness, we remark that the mechanisms of the non-linearities of low-voltage analogue Class D amplifiers, based on NS but with a quasi-linear carrier, for power-critical analogue hearing instruments are now well understood from a recent publication [Tan et. al., 2003] from our research group.

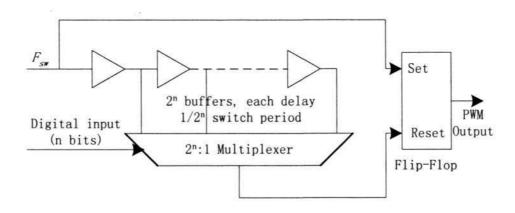

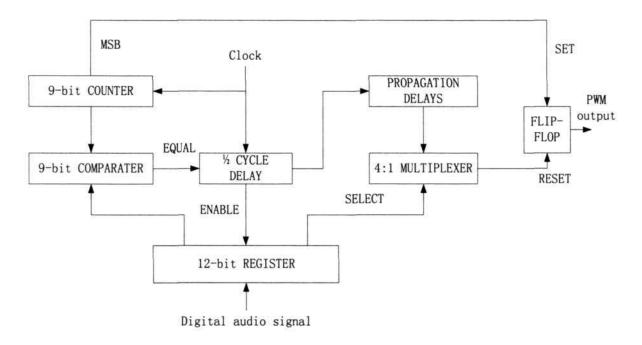

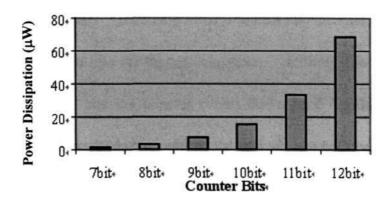

Pulse generators for the algorithmic PWM include the clock-counter [Wei and Horowitz, 1996], tapped-delay-line [Dancy and Chandrakasan, 1997], a hybrid combination of clock-counter cum tapped-delay-line [Dancy and Chandrakasan, 1998], and the clock-counter cum noise-shaper approach [Hiorns et. al., 1990; Tewksbury and Hallock, 1978] abbreviated the CNS pulse generator. Of these designs, the CNS pulse generator is the preferred design because of its robustness (in the sense that its parameters are virtually independent of fabrication process variations) in design and all its building blocks are compatible with standard digital CMOS fabrication processes. As in the case of the sampling processes, it is highly desirable that the sampling rate of the counter embodied in CNS pulse generator be low for low power dissipation. This

is because the pulse generator dominates the power dissipation in the Class D amplifier, and its clock counter is the functional block that dissipates the largest power.

In the later sections (Sections 2.2 - 2.4) in this chapter, we will provide a somewhat comprehensive review of reported PWM sampling processes and pulse generators.

The oversampled  $\Delta\Sigma$  PCM-PWM method [Melanson, 1998] is essentially a PCM-to-PWM converter where the PCM signal is the original sampled signal, the Uniform Sampled (US, see section 2.2 later) data. This conversion process is usually complex, including the following chronological processes: oversampling by interpolation, ΔΣ modulation and a Pulse-Density-Modulation (PDM)-to-PWM converter. The oversampling effectively reduces the wordlength of the input samples in the interpolation process but at the cost of a higher clock frequency (typically 27-28 times, thereby reducing the wordlength of the input samples by 3-4 LSBs) and increased computation, including the need for digital filtering. The subsequent  $\Delta\Sigma$ modulation is also usually relatively complex and involves a delta sigma modulator a table look-up may be used instead of direct computation to reduce the intensity of the To reduce the high frequency of the PDM output, bit-flipping computation. techniques [Magrath and Sandler, 1997; Esslinger et. al., 2002] are sometimes used. However, these techniques result in some errors and as a result, may compromise the low linearities attribute of the oversampled  $\Delta\Sigma$  PCM-PWM method and may possibly lead to instability. Finally, a PWM output is obtained via a PDM-to-PWM converter and the PWM output is usually low resolution (~5-bit) but timed to a medium speed clock (~10s MHz). The analogue output can be obtained by low pass filtering the high frequency PDM signal directly or the lower frequency PWM signal.

In short, it is instructive to appreciate that the computation of the oversampled  $\Delta\Sigma$  PCM-PWM method is substantially more intensive than the algorithmic PWM method. However, the primary advantage [Melanson, 1998] of the oversampled  $\Delta\Sigma$  PCM-PWM method hitherto is its low THD, typically 0.08% (compared to ~0.2% in typical algorithmic PWMs), negligible intermodulation distortion is over the entire audio bandwidth and high Signal-to-Noise Ratio (SNR). The reduced THD, however, is obtained at considerable hardware (including a larger IC area) and power dissipation costs, and these costs may be prohibitive for power critical applications.

Click Modulation PWM [Streitenberger et. al., 2001; Logan, 1984] involves the application of Hilbert transform to convert the audio signal into a complex signal. It further involves an analytic exponential modulation to generate a binary signal having a separated baseband and finally the PWM signal is generated. Despite of the computation complexity of Click Modulation PWM, it does not appear, in practice, to offer any advantage in terms of non-linearities. This is because both the algorithmic PWM and  $\Delta\Sigma$  PCM-PWM methods can offer comparable low non-linearities but with lesser computation demands.

## 2.2 Review of Different PWM Sampling Processes

In this section, we will review different reported PWM sampling processes. We will first describe the PWM signals in general and qualify the most common figure-of-merit that qualifies the PWM signals and/or a Class D amplifier. Thereafter we will provide an overview of the most common PWM sampling process and review other reported sampling processes.

### 2.2.1 PWM signals

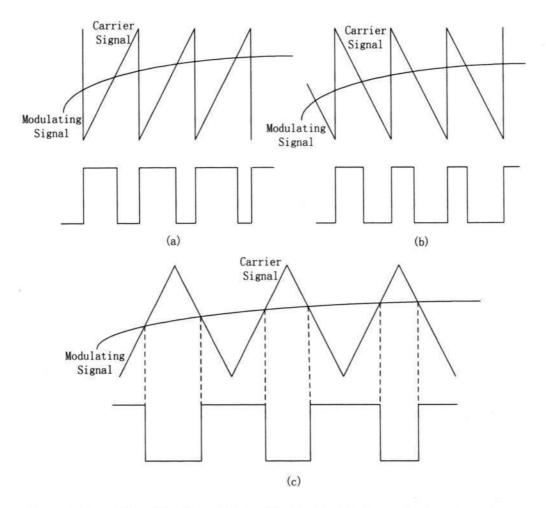

PWM schemes can be generally categorised [Black, 1953] into single-edge PWM and double-edge PWM, and this is illustrated in Figure 2.2. In the single-edge PWM (Figure 2.2(a) and (b)), either the leading or the trailing edge of the rectangular PWM output pulse is presented to a given carrier frequency, while the position of the other edge is determined by the value of the input modulating signal. The single-edge PWM consequently produces a sequence of rectangular pulses whose widths are proportional to the signal values.

Figure 2.2 Classification of Pulse Width Modulations: (a) Leading edge modulation, (b) Trailing edge modulation, and (c) Double edge modulation

In double-edge PWM (Figure 2.2 (c)), both the leading and the trailing edges of the pulses are modulated by the input signal, either in a symmetric fashion (a single sample value determines both edges) or an asymmetric fashion (the leading and trailing edges correspond to two successive sample values). Since the double-edge PWM is usually more difficult and more expensive to implement than the single-edge PWM, the single-edge PWM is the more common accepted form of modulation, and this is the only form of interest in this dissertation. For completeness, note that in principle, the approaches adopted to analyze single-edge PWM signals can be applied

to the double-edge PWM signals as well.

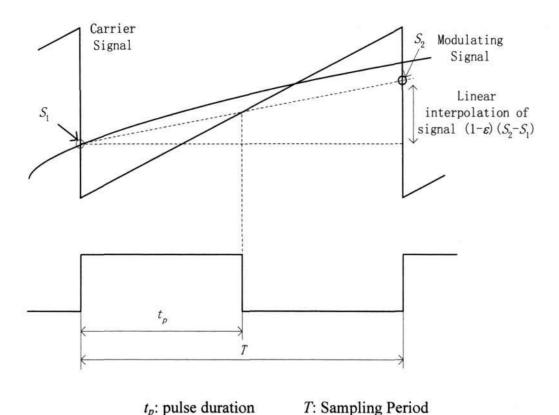

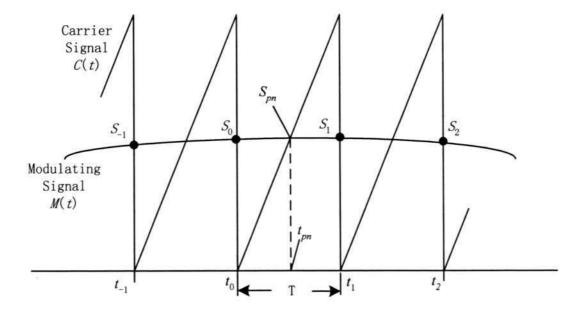

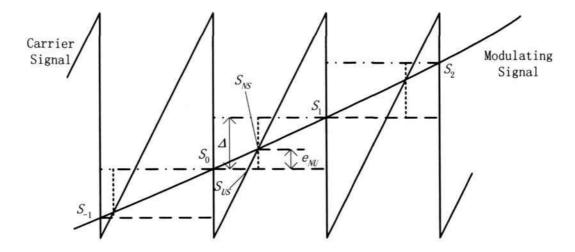

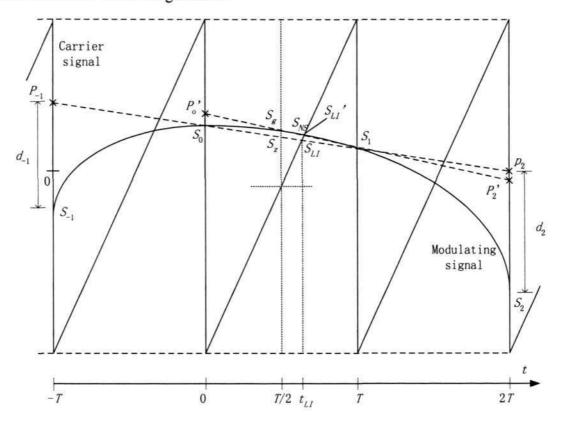

#### 2.2.2 Total Harmonic Distortion (THD)