## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# High level thermal-aware scheduling for multiprocessors

Jin, Cui

2012

JIn, C. (2012). High level thermal-aware scheduling for multiprocessors. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/54996

https://doi.org/10.32657/10356/54996

Downloaded on 13 Mar 2024 14:54:56 SGT

#### NANYANG TECHNOLOGICAL UNIVERSITY

# High Level Thermal-Aware Scheduling for Multiprocessors

## Cui Jin

## **School of Computer Engineering**

A Thesis Submitted to the Nanyang Technological University in fulfilment of the requirement for the degree of Doctor of Philosophy

## Acknowledgements

First, I would like to express my deeply heartfelt thanks to my supervisor, Associate Professor Douglas L. Maskell, for his intellectual guidance, constructive and patient direction as well as his unceasing attention, support and encouragement. It is he who led me into a new wonderful palace of science, which made me enjoy the pursuit of the Ph. D. all the time. I wish to thank him for the open, interactive and relaxed academic environment he provided for me. In particular, I would like to thank him for all his kind consideration and care for me in my daily life and all the special time and effort he has spent to support me to fulfil the Ph. D. What I benefited from him has contributed much to my current career and I believe it will assist me more in my way ahead.

I would like to thank the staff and the students in the Centre for High Performance Embedded Systems for their kind help for my research work and all the happy days I have had with them.

I would like to acknowledge the School of Computer Engineering, Nanyang Technological University for providing the research facility and the research scholarship.

I wish to express my thanks in my deep heart ocean to my fiancée, Zheng Yuanyuan for her consistent care and support. Her words are always companying with me to shrink the tough time and double the happiness in my life.

Last but not least, I want to thank my family in China, for their constant love and encouragement. Particularly, my parents and grandma are always caring and loving me. They unceasingly input encouragement, comfort and support to me. I can do nothing to express my deep gratitude to them but dedicate the thesis to them.

## **Table of Contents**

| Acl | knowle   | dge  | ements                                                    | i   |

|-----|----------|------|-----------------------------------------------------------|-----|

| Tal | ole of ( | Con  | itents                                                    | ii  |

| Lis | t of Fig | gur  | es                                                        | v   |

| Lis | t of Ta  | ble  | s                                                         | vii |

| Abs | stract   |      |                                                           | 1   |

| Cha | apter 1  | In   | troduction                                                | 3   |

|     | 1.1      | Po   | ower and Thermal Optimization                             | 5   |

|     | 1.2      | M    | otivation of the Research                                 | 6   |

|     | 1.3      | Tł   | nesis Organization                                        | 8   |

| Cha | apter 2  | 2 Pc | ower/Thermal-Aware Management and Scheduling              | 11  |

|     | 2.1      | Po   | ower Profiling                                            | 13  |

|     | 2.1      | .1   | Offline Power Profiling (Simulator-Based)                 | 15  |

|     | 2.1      | .2   | Online Power Profiling (Counter-based)                    | 18  |

|     | 2.1      | .3   | Leakage Power Estimation and Profiling                    | 19  |

|     | 2.2      | Т    | emperature Estimation and Profiling                       | 22  |

|     | 2.2      | .1   | Power/Thermal Model                                       | 22  |

|     | 2.2      | .2   | Direct Readings from Digital Thermal Sensors (DTS)        | 29  |

|     | 2.3      | D;   | ynamic Thermal Management at the Micro-Architecture Level | 31  |

|     | 2.4      | Tł   | nermal-Aware Scheduling                                   | 36  |

|     | 2.4      | .1   | Power/Energy-aware Scheduling                             | 37  |

|     | 2.4      | .2   | Static TAS                                                | 38  |

|     | 2.4      | .3   | Dynamic TAS                                               | 43  |

|     | 2.5      | Di   | iscussion                                                 | 50  |

| Cha | apter 3  | 3 A  | Fast Event-Driven Thermal Model                           | 53  |

|     | 3.1      | M    | ethodology and Metrics                                    | 54  |

|     | 3.2      | Po   | ower Events and their Profiling                           | 55  |

|     | 3.3      | Tł   | nermally Different Location                               | 59  |

|     | 3.4      | Tł   | nermal Model                                              | 61  |

|     | 3.5      | Pr   | ebuilding the LUT                                         | 63  |

|     | 3.6      | M    | apping Power Input to the Correct Core                    | 65  |

|     | 3.7      | Su   | perposition Principle of the Thermal Response (LUT)       | 68  |

|    | 3.8       | Validation of the Generated LUT                                   | 70   |

|----|-----------|-------------------------------------------------------------------|------|

|    | 3.9       | Summary                                                           | 74   |

| Ch | apter 4   | Schedulability with Thermal Constraints in a Static Thermal-Aware |      |

| Sc | heduling  | Scenario                                                          | 77   |

|    | 4.1       | Preliminary                                                       | 78   |

|    | 4.1.      | 1 The Task Model                                                  | 79   |

|    | 4.1.      | 2 Power Event and LUT                                             | 80   |

|    | 4.2       | LUT-Based Operations                                              | 81   |

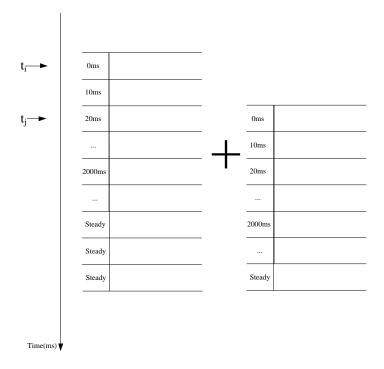

|    | 4.2.      | 1 Addition of Two LUTs                                            | 81   |

|    | 4.2.      | 2 Simplified LUT Addition for a Single Task                       | 82   |

|    | 4.2.      | 3 Addition of Task Tables                                         | 85   |

|    | 4.3       | Static Thermal Aware Scheduling Algorithm                         | 86   |

|    | 4.3.      | 1 Schedulability and Performance Maximization                     | 87   |

|    | 4.3.      | 2 Heuristic Peak Temperature Minimization                         | 90   |

|    | 4.4       | Problem Extension                                                 | 93   |

|    | 4.4.      | 1 Using Slack to Cool Down the Chip                               | 94   |

|    | 4.5       | Experiment                                                        | 95   |

|    | 4.5.      | 1 Validation of the Framework                                     | 96   |

|    | 4.5.      | 2 Effectiveness of the Schedulability Test                        | 98   |

|    | 4.5.      | 3 Heuristic Thermal Optimization based on Static TAS              | 101  |

|    | 4.6       | Summary                                                           | 106  |

| Ch | apter 5   | Predictive Dynamic Thermal-Aware Scheduling with Leakage Power    | er   |

| Mo | odelling. |                                                                   | 107  |

|    | 5.1       | Preliminary                                                       | 109  |

|    | 5.1.      | 1 Leakage Power Modelling in High Level Optimization              | 109  |

|    | 5.1.      | 2 Power Events and their Data Structure                           | 111  |

|    | 5.2       | Online Thermal Estimation in a Non-Temperature-Dependent Leaks    | age  |

|    | Power     | Scenario                                                          | 112  |

|    | 5.3       | Online Thermal Estimation on a Temperature-Dependent Leakage F    | ower |

|    | Scenar    | io                                                                |      |

|    | 5.4       | Algorithms for Thermal Map Monitoring and Prediction              |      |

|    | 5.5       | Algorithm Extension                                               |      |

|    | 5.5.      |                                                                   |      |

|    | 5.5.      |                                                                   |      |

|    | 5.6       | Heuristic Predictive Task Allocation                              |      |

| 5.6.1 Future Coolest First                                    | 123 |  |  |  |

|---------------------------------------------------------------|-----|--|--|--|

| 5.6.2 Future Neighbour Aware                                  | 124 |  |  |  |

| 5.6.3 Future Task Aware                                       | 124 |  |  |  |

| 5.6.4 Future Temperature Trend                                | 125 |  |  |  |

| 5.7 Experiments                                               | 125 |  |  |  |

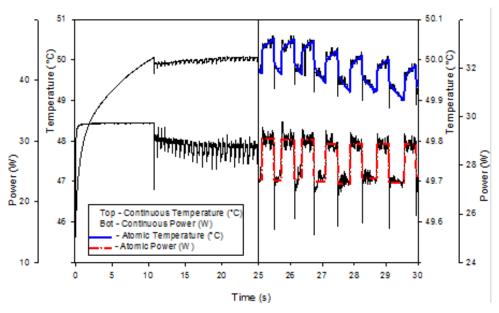

| 5.7.1 Validating the Event-Driven Estimator                   | 126 |  |  |  |

| 5.7.2 Event Driven Thermal Estimation for CMP systems         | 130 |  |  |  |

| 5.7.3 Heuristic Predictive Task Allocation for DTAS           | 134 |  |  |  |

| 5.8 Summary                                                   | 138 |  |  |  |

| Chapter 6 Conclusions and Future Work                         |     |  |  |  |

| 6.1 Contributions                                             | 139 |  |  |  |

| 6.2 Future Work                                               | 141 |  |  |  |

| Reference                                                     |     |  |  |  |

| Appendix A Multi-ARM Simulator for Power Profiling            |     |  |  |  |

| A.1 Multi-core ARM Simulator                                  | 158 |  |  |  |

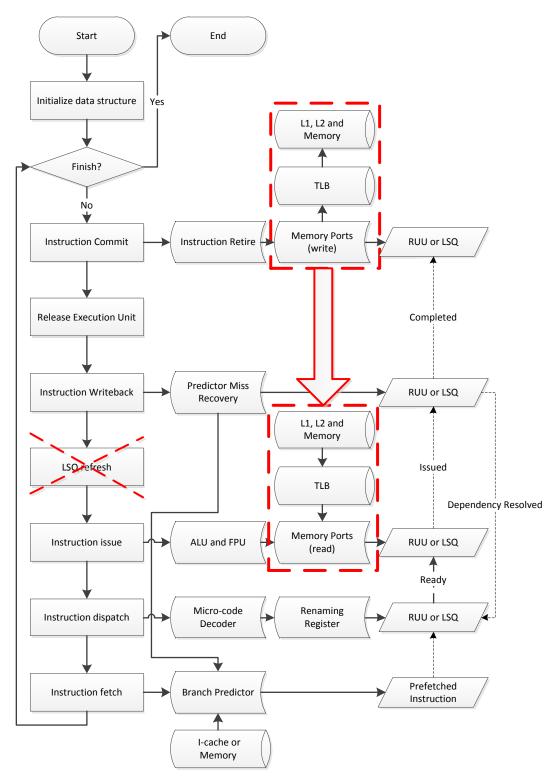

| A.1.1 Basic Simulation Procedure in SimpleScalar-ARM          |     |  |  |  |

| A.1.2 Transactional Load/Store Instructions                   | 166 |  |  |  |

| A.1.3 Inter-Core Communication                                | 168 |  |  |  |

| A.1.4 System Calls and Instructions Needed By Multi-Threading | 174 |  |  |  |

| A.2 Summary                                                   | 183 |  |  |  |

| Appendix B An Example of Online Thermal Estimation            |     |  |  |  |

| Annendix C. Author's Publications List                        | 187 |  |  |  |

## **List of Figures**

| Figure 1.1: Consumer stationary design complexity trends                                 |

|------------------------------------------------------------------------------------------|

| Figure 1.2: Evolving Roles of Different Design Levels in Overall System Power            |

| Minimization6                                                                            |

| Figure 2.1: The high level management and optimization process                           |

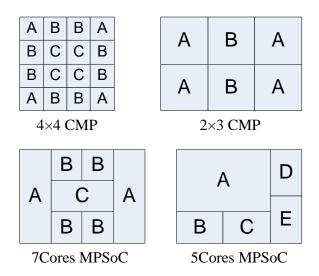

| Figure 2.2: Thermal model for 4×4 CMP                                                    |

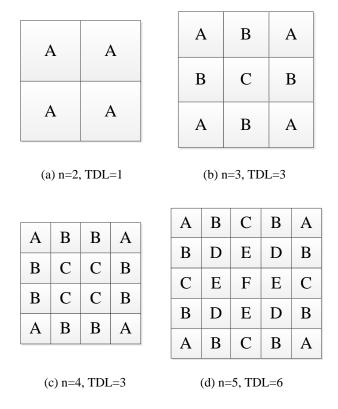

| Figure 2.3: A CMP and its corresponding TDL                                              |

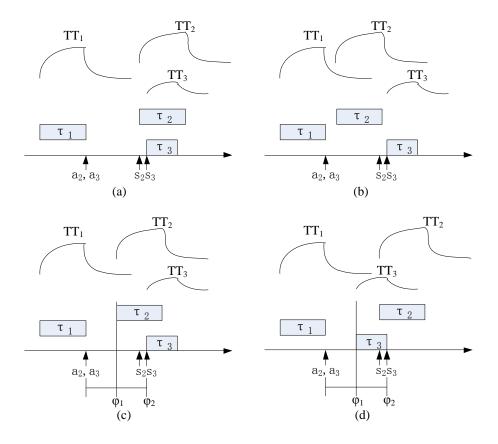

| Figure 2.4: Example of TAS polices                                                       |

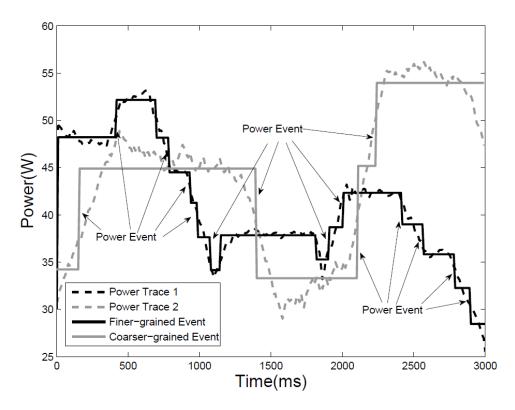

| Figure 3.1: Power event profiling                                                        |

| Figure 3.2: Temperature Trace Comparison for Synthetic Power Input59                     |

| Figure 3.3: Temperature Trace Comparison for MPEG2 decoder power profile59               |

| Figure 3.4: Core/module level abstraction                                                |

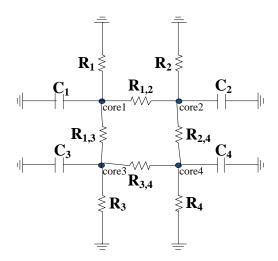

| Figure 3.5: Thermal RC network for a 2×2 CMP                                             |

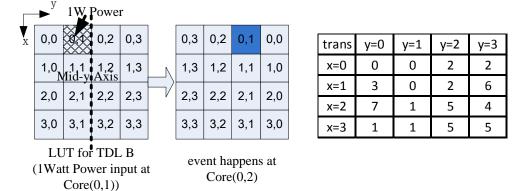

| Figure 3.6: Transformation for Power Input Mapping                                       |

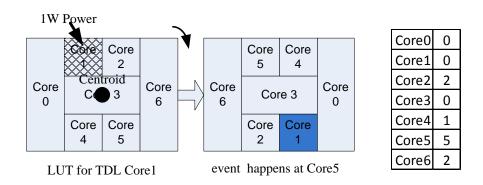

| Figure 3.7: Thermal response for any single power event                                  |

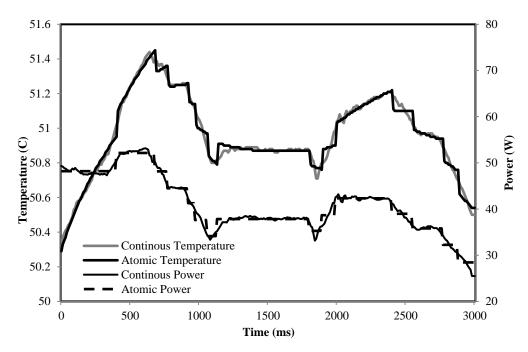

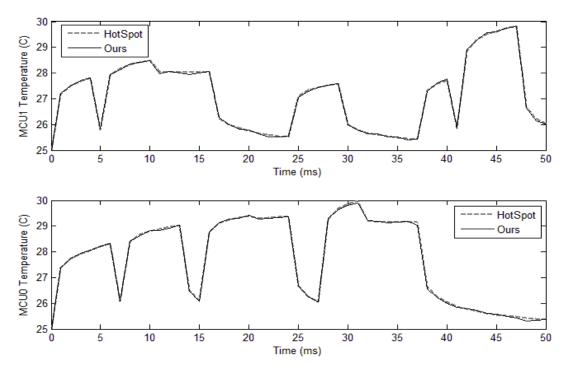

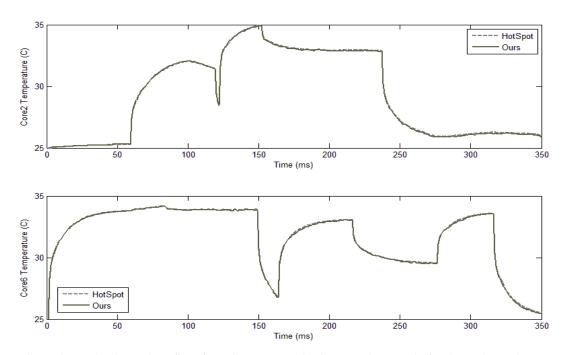

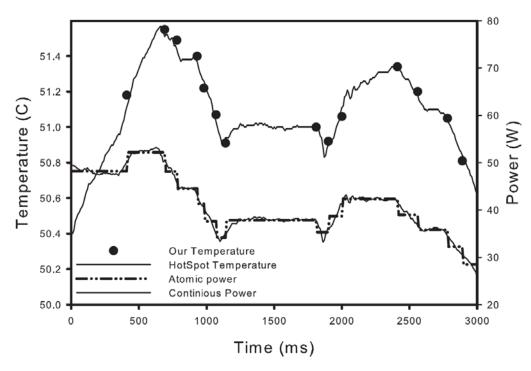

| Figure 3.8: Event-driven temperature estimation comparing with HotSpot71                 |

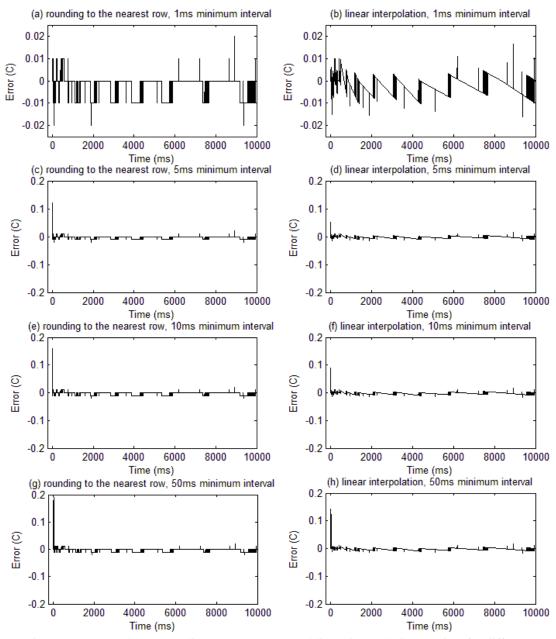

| Figure 3.9: Errors due to rounding to nearest row, and linear interpolation vs. time for |

| different resolutions                                                                    |

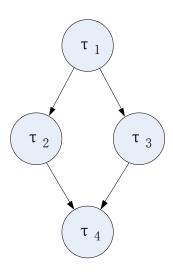

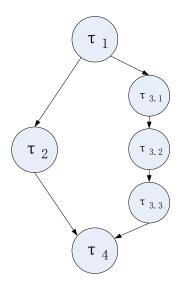

| Figure 4.1: A task graph80                                                               |

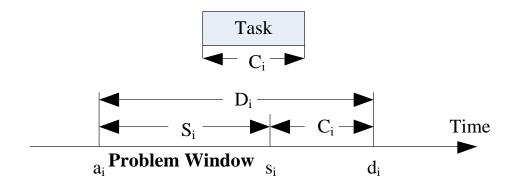

| Figure 4.2: The problem window80                                                         |

| Figure 4.3: The addition of two LUTs                                                     |

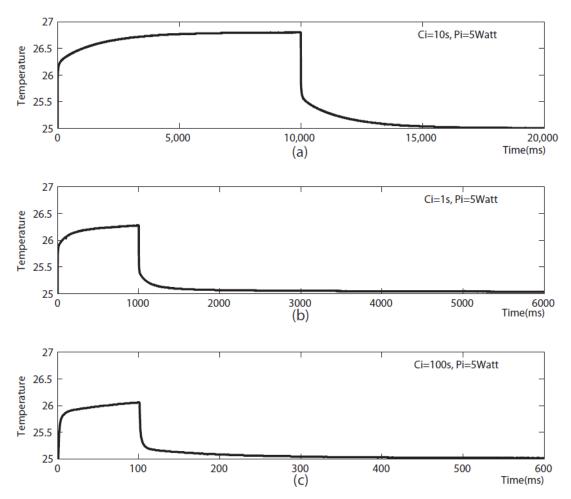

| Figure 4.4: The core thermal profile for different trancated table length84              |

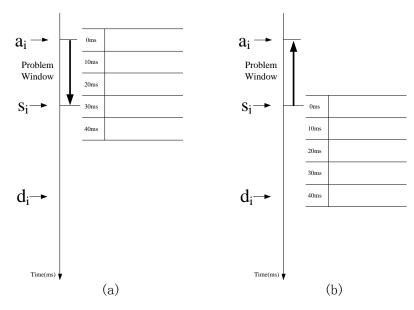

| Figure 4.5: Searching (a) Forward in time, and (b) Backward in time                      |

| Figure 4.6: A heuristic for minimizing the temperature during a backward search93        |

| Figure 4.7: Task splitting for Figure 4.1                                                |

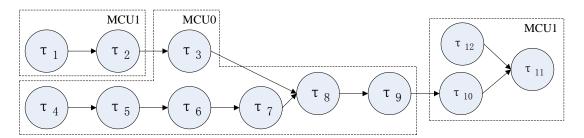

| Figure 4.8: The task graph for PapaBench                                                 |

| Figure 4.9: A successful thermal schedule for PapaBenchError! Bookmark not               |

| defined.                                                                                 |

| Figure 4.10: Thermal Profile Comparison of Figure 4.9                                    |

| Figure 4.11: The thermal profile of two hottest cores in the 15-task example for the     |

| 2×4 core layout101                                                                       |

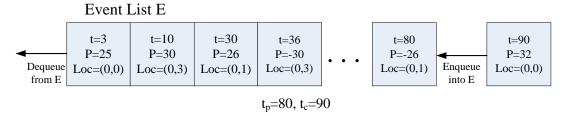

| Figure 5.1: Data structure related to power events                                  |  |  |  |  |

|-------------------------------------------------------------------------------------|--|--|--|--|

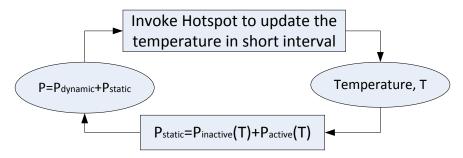

| Figure 5.2: Iterative procedure to use HotSpot in temperature-dependent scenario114 |  |  |  |  |

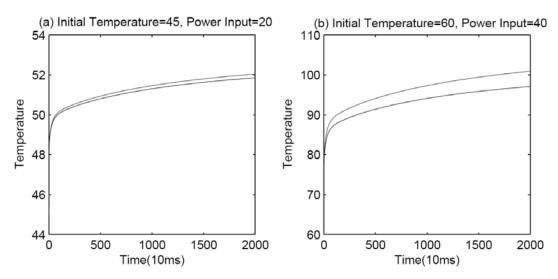

| Figure 5.3: The temperature profile for the temperature-dependent (upper) vs. non-  |  |  |  |  |

| temperature-dependent (lower) simulations for different initial temperature and     |  |  |  |  |

| power                                                                               |  |  |  |  |

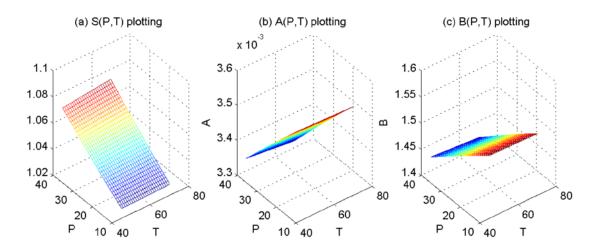

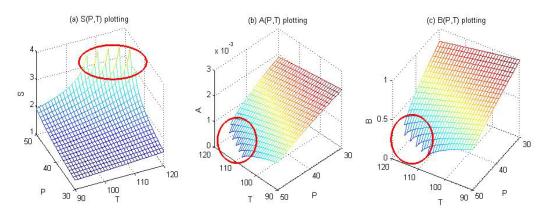

| Figure 5.4: Plots of S, A, B versus power and temperature for a 4×4 CMP117          |  |  |  |  |

| Figure 5.5: Thermal runaway described by S, A, B plots                              |  |  |  |  |

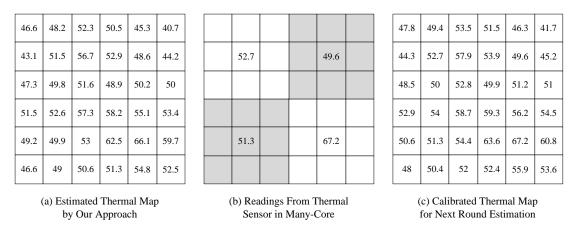

| Figure 5.6: Example of calibration using real temperature readings122               |  |  |  |  |

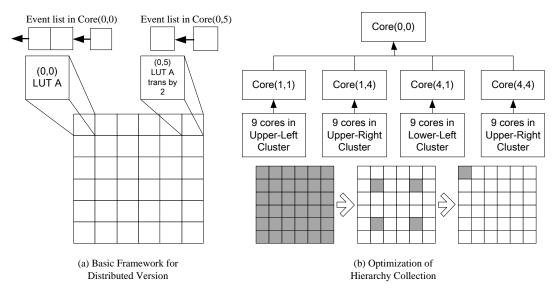

| Figure 5.7: A distributed version of our online algorithm                           |  |  |  |  |

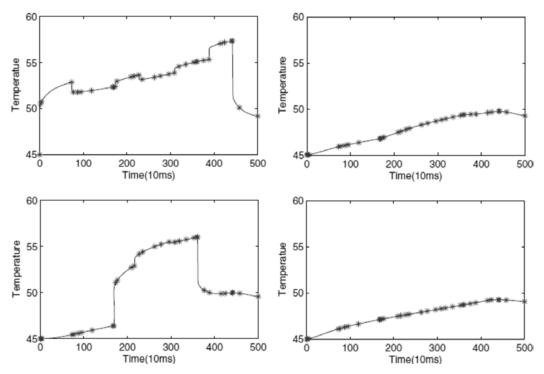

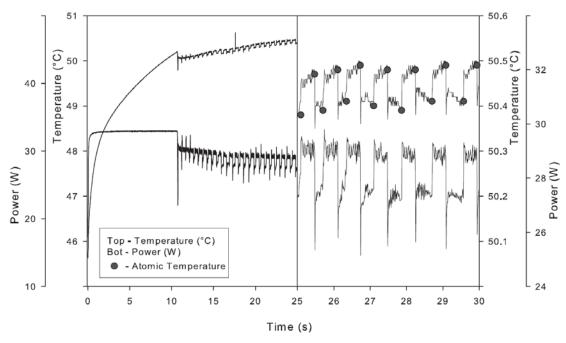

| Figure 5.8: The variant-P thermal simulation of a single core processor using a     |  |  |  |  |

| synthetic power input127                                                            |  |  |  |  |

| Figure 5.9: The variant-P thermal simulation for an MPEG2 decoder at the core level |  |  |  |  |

|                                                                                     |  |  |  |  |

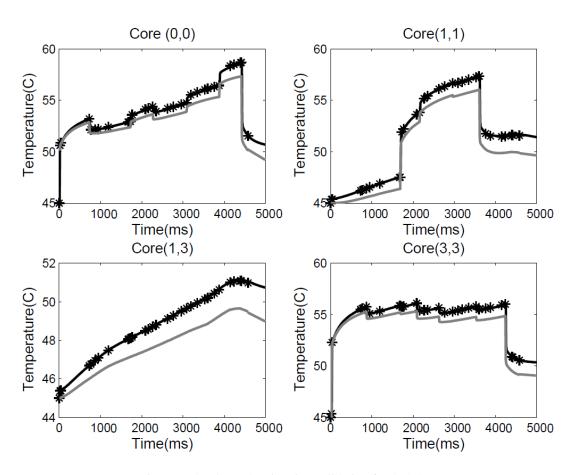

| Figure 5.10: Thermal estimation validation for 4×4 CMP                              |  |  |  |  |

| Figure A.1: The flow chart of SimpleScalar                                          |  |  |  |  |

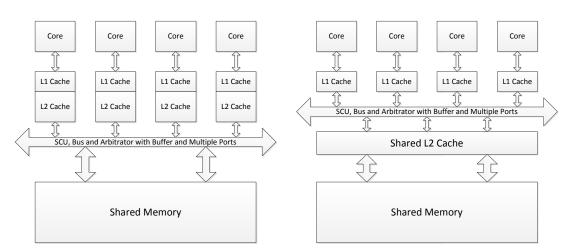

| Figure A.2: SCU and Cache Hierarchy                                                 |  |  |  |  |

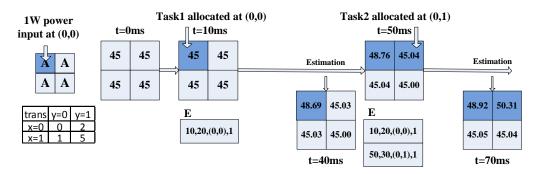

| Figure B.1: Example of online event driven estimation                               |  |  |  |  |

## **List of Tables**

| Table 3.1: Look-Up Table for a 2×2 CMP                                           | 64    |

|----------------------------------------------------------------------------------|-------|

| Table 3.2: Event-driven calculation overhead and runtime comparing with HotSpo   | ot 72 |

| Table 3.3: Non-uniform interval applied for different resolutions of LUTs        | 72    |

| Table 3.4: Errors in the LUT due to different LUT row resolutions                | 73    |

| Table 4.1: The task properties                                                   | 79    |

| Table 4.2: The error (in °C) caused by different table truncation lengths        | 84    |

| Table 4.3: Accumulated error and runtime for different length of truncated table | 85    |

| Table 4.4: Tasks characteristics from PapaBench after simulation and profiling   | 97    |

| Table 4.5: The HP algorithm runtime comparison for the 2×4 core layout           | .100  |

| Table 4.6: The HP algorithm runtime comparison for the 4×4 core layout           | .101  |

| Table 4.7: Maximum core temperature (in °C) using non-TAS scheduling             | .102  |

| Table 4.8: Temperature optimization for the schedulable task sets                | .103  |

| Table 4.9: High utilization scenario and low utilization scenario                | .104  |

| Table 4.10: High power consumption scenario and low power consumption scenar     | oi    |

|                                                                                  | .105  |

| Table 5.1: Core Level error and overhead in temperature-dependent leakage power  | r     |

| scenario                                                                         | .128  |

| Table 5.2: MA Level error and overhead in temperature-dependent leakage Power    |       |

| scenario                                                                         | .129  |

| Table 5.3: MA Level error and overhead in non-temperature-dependent leakage      |       |

| power scenario                                                                   | .129  |

| Table 5.4: Performance, average error, overhead comparison                       | .132  |

| Table 5.5: Algorithm performance for varying runtime                             | .133  |

| Table 5.6: Algorithm performance for varying input power granularity             | .134  |

| Table 5.7: Temperature Optimization and Comparison amongst Different DTAS        |       |

| Policies                                                                         | .135  |

| Table 5.8: DTM Times and Overall Task Completion Time amongst Different DT       | AS    |

| Policies                                                                         | .137  |

| Table 5.9: Soft Real-Time Performance amongst Different DTAS Policies            | .137  |

| Table A.1: Comparison between MPI and pthread                                    | .157  |

| Table A.2: System calls needed by multi-threading                 | 176 |

|-------------------------------------------------------------------|-----|

| Table A.3: The slight modifications to some existing system calls | 181 |

| Table A.4: Tested pthread functions                               | 182 |

| Table B.1: Look-Up Table for a 2×2 CMP                            | 185 |

#### **Abstract**

Power and thermal issues are primary design constraints in both stationary and portable computing devices. Adverse thermal issues can impact microprocessor performance, including computational speed degradation, aging, and unreliable system behaviour. These situations are exaggerated in current state-of-the-art multiprocessors due to their high power density and the thermal coupling between cores. High level thermal-aware scheduling (TAS) is seen as one possible solution to optimize and control on-chip temperature. However, after performing an extensive review of the literature, a number of shortcomings in current high level TAS implementations have been identified. These include, the inaccuracy of thermal sensor readings, low computational efficiency of existing time-triggered thermal simulators, oversimplified thermal and leakage power models currently used at the system level, lack of appropriate thermal constraints used in scheduling analysis in hard real-time embedded systems and a lack of appropriate fine-grained dynamic TAS (DTAS). These shortcomings have provided suitable motivation for the work described in this thesis, which includes the following contributions:

- A fast event-driven look-up table (LUT) based thermal estimation approach is developed. We introduce the concept of power events which capture the significant power changes on-chip. These power events induce a temperature change which can be easily obtained using the pre-calculated LUTs (representing the thermal response of a unit power input). We show that these thermal responses, induced by individual power events, satisfy the superposition principle and can be accumulated to evaluate the thermal map when any event occurs. We also define the necessary optimizations and operations for the LUTs. Experimental results show our LUT method is accurate, producing thermal estimations of similar quality to an existing open-source thermal simulator (HotSpot), while providing 2 to 3 orders of magnitude reduction in computational complexity.

- We use our fast LUT approach to analyze the offline schedulability for a realtime task set on a simulated multiprocessor system under a strict (hard)

thermal constraint. This is very useful for reducing the risk of overheating in safety-critical embedded systems. Our schedulability test can also be used as a framework to optimize other goals (e.g. maximizing the performance and minimizing the peak temperature). We show that we are able to schedule large task sets (up to 50 tasks) in reasonable time (less than 12 minutes), which is 2 to 3 orders of magnitude faster than using scheduling with existing thermal simulation tools.

• For high power multiprocessor (or many-core) systems, it is not possible to ignore the temperature-leakage power dependence. Therefore, we modify the LUT-based approach to include a temperature-dependent leakage power model. The leakage power calibration enables us to accurately predict the near future thermal map without needing to resort to a computationally expensive iterative approach. Based on this prediction, we develop several heuristic policies for dynamic TAS on a simulated many-core system. We show that our proposed predictive policies are significantly better, in terms of minimizing average/peak temperature, reducing the dynamic thermal management overhead and improving other real-time features, than existing TAS schedulers, making them highly suitable for heuristically guiding thermal aware task allocation and scheduling.

### **Chapter 1**

#### Introduction

Microprocessor performance has been one of the primary design goals, with performance scaling to follow Moore's law over the last few decades. To facilitate these performance advances, the transistor gate length and the dioxide thickness have been reduced year on year, thus allowing more and more complex functional units to be integrated into a much smaller area. This dimension shrinking in the modern integrated circuit (IC) manufacturing process brings a number of advantages such as smaller signal delay on shorter wires, lower core voltage, shorter signal edge, smaller chip area and more I/O pins on package. However, the function complexity and the number of transistors are becoming incredibly high, resulting in a number of disadvantages, including extremely high power density, increased design time and increased validation complexity. The high power density results in increased energy consumption and chip temperature.

Power/thermal issues in uniprocessor system have been intensively studied by both academia and industry [15][45][48][50][55][56][57][58]. The thermal effects introduced by the high power density on chip are unavoidable, with heat fluxes (or power densities) in state-of-the-art microprocessors currently being in the range of 200-300W/cm<sup>2</sup> [1], and are expected to continue to increase. Power/thermal effects can impact the following critical metrics:

- Computational Speed Degradation: A higher temperature may degrade the computational speed due to the current leakage induced by carrier migration at the physical level [5][53].

- Reliability: Operating the processor at above the thermal designed power (TDP) could induce a timing sequence error and even physical damage. A timing error is recoverable without destroying the processor, but physical damage, such as a transistor fusing, is permanent. Current commercial processors usually embed thermal sensors into the core to monitor the temperature and control the temperature to within a safe threshold [102][103].

- Accelerated Aging: High temperatures can accelerate aging and shorten the life span of the processor. The metal components and wires on die can ablate in a long-term hot environment. As such, both the reliability and lifespan are reduced [102].

- Cost: Better packaging techniques and external cooling devices for heat

dissipation increase the system cost dramatically. The processors used in

embedded systems generally depend on natural convection, using the heat

spreader and package to passively remove excess heat, while desktop and

server processors depend on active cooling devices [27][35].

- Power: Higher temperatures increase the leakage currents which contribute to higher static power consumption. The increased static power results in an increased temperature, resulting in a positive feedback relationship between static power and temperature, which can result in processor failure due to "thermal runaway" [77].

- User Perception: Higher temperatures can result in an uncomfortable feeling while using the devices. This is particularly the case with portable devices.

About a decade ago, processor designers realized that reducing the transistor size was not going to produce significant frequency gains, as occurred previously, due to adverse power/thermal effects. This launched the multi-core era, as the best way to efficiently utilize the available silicon was to duplicate multiple processors on a single die. However, this does not solve the thermal problems. In fact, the ITRS [1] have identified power and thermal issues as a major design constraint and bottleneck for current and future computing devices.

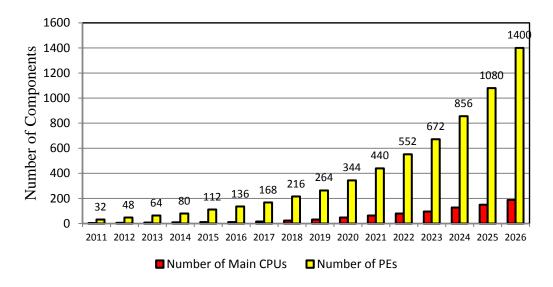

In the last decade, processor manufactures have introduced a number of multi-core processors for mainstream server and desktop market. For example, the modern Intel Xeon processor, targeting the server market, has up to 10 processing cores [113]. ITRS [1], reproduced here as Figure 1.1, predicts that the number of CPUs will hit 50 by the 2020s, if not sooner.

Figure 1.1: Consumer stationary design complexity trends [1]

#### 1.1 Power and Thermal Optimization

Power and thermal optimization in microprocessors has been extensively studied [2][3][4][5][6][7][8][9][10][11][12][13][14][15][16][17][18][19] and is applied at different levels in the design flow. Different approaches and techniques are applicable at each level. At the lower levels (e.g. the physical [2][3][4][7][8][9][10], logic and register transfer levels [15][17][18][19]), the techniques used are relatively mature [1] and include: new materials (e.g. High-K dielectric [5] or GeA compounds [1]) and new processes (such as, tri-gate [6], FinFET [53] and 3D-ICs [11]). The EDA tools used for design at these levels also provide support for power/thermal-aware synthesis, mapping [12][13][14], placement and routing [7][8][9].

Techniques for power/thermal management applicable at the micro-architecture and architecture level include: dynamic voltage and frequency scaling (DVFS) [21], clock gating [21], pipeline gating [21], stop & go policy [21], I-cache toggling [20][21]. There techniques are usually adopted on a global or per-module basis.

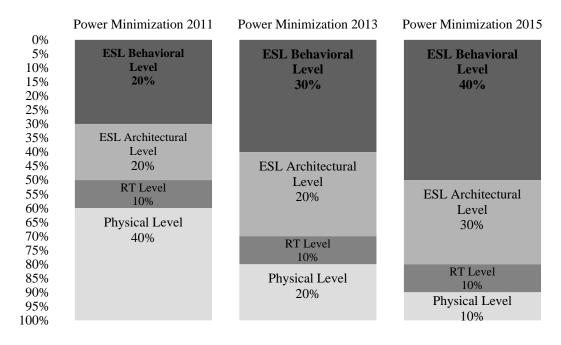

At the higher levels (e.g. the algorithmic and system level), compiler optimization techniques [22] and scheduling [21][69][72][81][82][88][89] can help to alleviate the power/thermal issues in a high-level (abstracted) way. In fact, according to the ITRS

<sup>&</sup>lt;sup>1</sup> We use the term multiprocessor in our research to refer to multiple processors, integrated onto a single silicon die and tightly coupled to each other.

[1], system-level power/thermal management and optimization will be confronted with tremendous opportunities and challenges in the coming decades. The ITRS predicts that the higher design levels will play an increasingly important role in achieving the required levels of system power minimization, as shown in Figure 1.2.

Figure 1.2: Evolving Roles of Different Design Levels in Overall System Power Minimization [1]

The increasing power densities associated with transistor scaling and the trend towards more and more processors on a single IC are likely to significantly impact on reliability and performance [1], while decreasing supply voltages worsen leakage currents and noise [1]. These trends will require power optimizations that simultaneously exploit techniques at all levels in the design process, as well as at the operating system and application software levels.

#### 1.2 Motivation of the Research

Increasing the power/ thermal optimisation efforts at higher design levels will produce more efficient circuits, which when mapped to the lower level could obtain better results than are possible for optimizations at the lower levels only. Higher level design impacts the performance of the whole system, implying that an improvement at the high-level could lead to significant overall savings.

Thus, examining high-level power/thermal optimisation for multi-core and many-core systems would appear to be an important and timely endeavour. In particular, high-level thermal optimisation and management for delivering power/thermal improvements at the system level would provide an appropriate focus for my research. However there are a number of challenges, or research questions, that need to be addressed. These include:

- Current thermal management techniques (e.g. DVFS, power gating, etc.) are coarse grained (with a relatively long time response from an OS scheduling point of view) and they are reactive (in that the system responds to a system event, such as the thermal threshold being exceeded). Will a fast proactive thermal-aware scheduling technique, such as thermal-aware scheduling (TAS), provide a better option for system-level thermal management?

- Current TAS techniques fall into one of two general categories:

- a. Relatively fast with a very simple, but inaccurate thermal model due to the thermal coupling effect between cores [65][92].

- b. Relatively slow due to a thermal simulator with an accurate but much more complex thermal model.

In a multi-core/many-core TAS scenario, and particularly for dynamic TAS (DTAS), both speed and accuracy are important. The scheduling analysis in static TAS (STAS), which is an NP-hard problem, would also benefit from an accurate but faster thermal estimator, particularly with the expended search space associated with multi-core/many-core systems. Is it possible to propose a technique for thermal estimation which is able to run orders of magnitude faster than a thermal simulator (such as the widely used HotSpot simulator [29][35][72][43]) while providing similar accuracy?

• Leakage power is an important consideration in current IC design, and will become more and more significant with transistor scaling. *Is it possible to extend a fast thermal estimator to include a leakage power model while still maintaining accuracy?*

If these questions can be answered, STAS and DTAS could be used to more effectively provide high-level thermal optimisation and management in multi-core

and many-core systems.

#### 1.3 Thesis Organization

Chapter 2 presents a detailed literature review where we analyse the strengths and weaknesses of the existing research in the area of power/thermal-aware management and scheduling.

In Chapter 3, we develop a fast and accurate technique for thermal estimation, applicable to multi-core/many-core systems. The technique is based upon event driven power changes and uses a fast look-up table (LUT) to perform the thermal estimation. The LUTs are prebuilt and use the same non-leakage model as HotSpot, and as such, have the same steady-state accuracy, but with a significantly reduced computational overhead. A number of primary definitions and LUT operations are introduced.

Chapter 4 applies this LUT-based approach to static thermal-aware real-time task scheduling in low power multi-core/many-core systems. In this scenario, the effect of leakage power is less significant and to some extent can be ignored. A forward search, which gives the minimum-time schedule of the task set for a given thermal constraint, is introduced. A heuristic peak temperature minimization algorithm is also developed. Experiments using both real and synthetic real-time benchmarks show that we are able to schedule large task sets (up to 50 tasks) in reasonable time (less than 11 minutes), which is 2-3 orders of magnitude faster than using scheduling in conjunction with the Hotspot thermal simulator.

Chapter 5 examines DTAS. It firstly extends the simple LUT-based thermal estimator developed in chapter 3 to include a temperature dependant leakage power model. To minimize the overhead, while maintaining the estimation accuracy, prebuilt look-uptables and predefined leakage calibration parameters are used to speed up the thermal solution. Based on this refined fast LUT-based thermal estimator, a number of heuristic DTAS algorithms are developed for high power multi-core/many-core systems. In this scenario, the effect of leakage power is much more significant and cannot be ignored. We show that our proposed DTAS policies are better able to

minimise the average/peak temperature than existing DTAS schedulers, making them highly suitable for heuristically guiding thermal aware task allocation and scheduling. We are able to reduce the dynamic thermal management overhead (by 3 orders of magnitude compared to using HotSpot) while maintaining comparable accuracy.

Lastly, in Chapter 6, we summarize and highlight the contributions of this work and discuss possible extensions and other future work.

### Chapter 2

## **Power/Thermal-Aware Management and Scheduling**

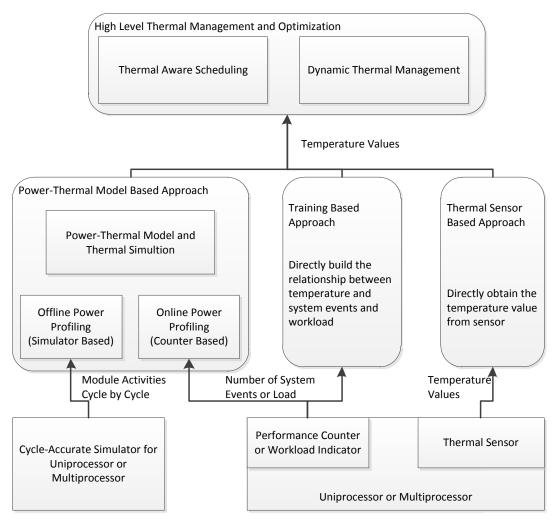

The current research examining power/thermal-aware management and scheduling in microprocessors is introduced and discussed in this chapter. Based on this review of the literature, we are able to summarize the high level thermal management and optimization process, as shown in Figure 2.1.

Figure 2.1: The high level management and optimization process

Thermal aware scheduling (TAS) and dynamic thermal management (DTM) are two common techniques used in high level thermal optimization. In general, TAS actively works with the OS scheduler, i.e. every time the scheduler is invoked (e.g. on the

occurrence of a timer tick interrupt in Round Robin scheduling, at the end of a system call or on the occurrence of an interrupt, etc.), to determine where to allocate (or migrate) a task according to some temperature criteria (e.g. allocate to the core with the lowest temperature or the lowest temperature gradient). Usually, TAS works in a relatively fine-grained time increment<sup>2</sup> while DTM is relatively coarse-grained and is passively triggered when the temperature exceeds a predefined threshold (resulting in the scaling down of the overheated core's frequency or putting the core into a low power sleep state).

Even though these two mechanisms are different, both of them can reduce or inhibit the occurrence of adverse thermal effects on-chip. Moreover, both techniques need to know the temperature distribution on-chip for proper operation. Therefore, capturing, monitoring or estimating the temperature is a vital step for high level thermal management and optimization.

In terms of TAS, there are two main categories in the research domain: static-TAS (STAS) and dynamic-TAS (DTAS). In STAS, thermal-aware scheduling is carried out offline, usually in design stage. STAS uses a pre-implemented power/thermal model and thermal simulator to schedule a set of tasks and simulate their corresponding thermal behaviours, without the need for real thermal sensors. DTAS, on the other hand, needs to track the temperature changes on-the-fly and schedule a task in, or near to, real time. Therefore, DTAS requires a fast thermal simulator, real-time thermal sensor information, or both, as the input. The various TAS techniques will be discussed in more detail in Section 2.4.

We classify the temperature measurement or estimation into three classes, as indicated in the middle part of Figure 2.1. These methods include: on-chip thermal sensor(s), training-based models that combine thermal sensor readings with the occurrence of system events; and temperature estimation based on a power profile measured using either a simulation based approach or a performance counter based approach. All of these methods can provide chip/processor/module temperature information to the higher level. However, each method has its own strengths and weaknesses, and will be discussed in more detail in Section 2.1 and 2.2.

\_

<sup>&</sup>lt;sup>2</sup> The typical TAS interval is usually that of two consecutive time ticks in the OS.

The procedure for high level thermal optimization and management can be summarized as in the following steps:

#### STAS

- a. Perform static power profiling for tasks.

- b. Predetermine a schedule that meets the task constraints (e.g. deadline)

- c. Estimate the temperature induced by the task based on a power-thermal model and the results from the thermal simulator.

- d. Determine if the schedule meets the temperature constraints or if temperature optimal metrics are achieved

- e. Iterate steps b, c and d if the desired thermal threshold is exceeded.

#### DTAS and DTM

- a. Perform static power profiling for tasks or dynamic power profiling using performance counters. This step is not necessary for a trainingbased approach or when using direct temperature sensor readings.

- b. Estimate the temperature based on a power-thermal model, a thermal simulator or a training-based approach, or direct temperature measurement from thermal sensors.

- c. Schedule the task based on the temperature estimation or thermal sensor reading.

- d. Repeat steps b and c at runtime.

In the following sections, we introduce and discuss the literature relating to DTM and TAS (including power profiling and thermal measurement/estimation). The strengths and weaknesses of the various techniques are highlighted and are then used to form the basis for the development of the research focus outlined in subsequent chapters.

#### 2.1 Power Profiling

The power consumption of the processor is composed of two main parts: the dynamic power consumption induced by the charging and discharging of the capacitors during signal switching and the static power consumption due to the inherent gate leakage and sub-threshold leakage effects in the process technology. The proportion of the

static power relative to the total power consumption increases with decreasing transistor feature size. Currently, the static power represents a very significant proportion of the total power and cannot be ignored, and therefore, high level power modelling and analysis must represent both these aspects (Equation 2.1).

$$P = P_{dynamic} + P_{static} (2.1)$$

For the dynamic power, an analytical expression for a single transistor is given by Equation 2.2:

$$P_{dynamic} = CV^2 f (2.2)$$

where C is the equivalent parasitic capacitance, V is the supply voltage and f denotes the frequency of signal switching. At the system/architectural level, a functional unit is composed of a large number of transistors with many different signal inputs. As such, simulating large scale circuit activity using the single transistor model will result in a significant computing overhead. As a result, most high-level power analysis and estimation techniques use a module-based approach that stores the different categories of power related parameters (e.g. the signal switching probability, determined by performing a number of simulations on a functional unit, and the equivalent parasitic capacitance, determined by performing circuit and gate level simulation, such as using HSPICE [37]) for each module at the architectural level. The total dynamic power can then be estimated based on the resource utilization and the power parameters. Since the power parameters are predetermined constants, the only variable is the switching frequency which can be significantly affected by different applications and their processed data. For instance, some computationintensive tasks require more ALU or FPU resources, while some data-access-intensive applications occupy the load/store queue and memory controller more frequently.

On the other hand, the static power consumption is related to the inherent transistor parameters (e.g. gate length, leakage ratio, voltage etc.), and is not affected greatly by the application. Therefore, power profiling firstly examines the resource utilization for a task to estimate its dynamic power consumption, and then adds the static power to determine the total power consumption. Both online and offline power profiling can estimate the resource utilization for the dynamic power component.

#### **2.1.1 Offline Power Profiling (Simulator-Based)**

Offline power profiling, also called simulator-based profiling, uses a simulator to estimate the power. The simulator can model the different activity details of a specific piece of hardware. For example, a circuit simulator emulates the signal switching at gate and wire level; a register-transfer-level (RTL) simulator can track the input/output and register values for every logical component (e.g. adder, multiplexer, flip-flop and so on); and a micro-architecture level simulator can emulate the status (e.g. input/output values, idle or busy) for each functional unit on a cycle-by-cycle basis.

Different simulators can provide different details of the signal activities and capacitance estimation, as such, affecting the accuracy of power profiling. A low level simulator has the best accuracy, but also requires a huge computation overhead, particularly if simulating a complex module. For example, while it may be possible to carry out a circuit level simulation of an entire processor, the computational resources and time required make this infeasible. Even at the higher register-transfer-level, a simulation for a common application may last for several days on a high performance workstation. Such a huge overhead is not acceptable for higher level optimization, especially for the on-line case.

The highest level of simulation is referred to as behavioural or functional simulation. This kind of simulator only analyses the binary instructions one by one in the execution file, and simulates their logical (semantic) outcomes and records the register and memory status in logical (semantic) order. This level of simulation can only reflect the logical correctness of a section of code, and neglects all the activities related to the realistic implementation of the instructions in a processor. Therefore, it is applicable for debugging software or testing logical behaviour of a code section, and is often used in the early developmental stages when a real hardware platform is unavailable. It is not suitable for any complex architecture, such as out-of-order execution (superscalar), branch prediction and speculation. This level of simulation has a relatively low computational overhead, and is able to emulate a full-system with a fully functional OS. A behavioural simulator concentrates on the logic, rather than on the implementation, and is not able to obtain the necessary cycle-by-cycle information relating to module utilization to provide an accurate power profile.

QEMU [38] is a very popular open source full-system emulator that supports a range of platforms (e.g. X86 PC, ARM Cortex-A9 PandaBoard, etc.). Simics [39] is also widely used in academia for multicore functional simulation, but it only supports simple in-order pipeline architectures. These simulators also neglect the implementation of the real processor, and as a result are unsuitable for power estimation.

GEMS [40] is a well-known execution-driven multiprocessor simulator, which can provide full system simulation. GEMS integrates with Simics, an in-order processor behavioural simulator, and Ruby, a customized memory subsystem simulator. However, Simics emulates the instruction behaviours one by one without properly simulating the processor stalls caused by inter-instruction dependency (e.g. data hazards3), and it only captures the stalls caused by the memory requests4 (e.g. the memory instruction latency simulated by Ruby, such as L1 and L2 cache hit and miss). As such, GEMS is unable to provide an accurate power estimation which reflects the realistic power consumption. Subsequently, the GEM5 implementation integrated M5 [114] as the processor simulator. This supports out-of-order superscalar simulation, but doesn't support the shared-memory-based pthread library for multi-threaded applications or provide a power profiler.

A micro-architecture (MA) level simulator simulates the activities and status (e.g. input/output, idle/busy) for the functional units (e.g. load/store queue, instruction fetch and decoding unit, ALU, register renaming units and so on). It reflects how these functional units work together and intercommunicate (e.g. internal bus, data path and instruction path) with each other in each cycle. The most important information obtained from a MA simulator is whether one unit is busy or idle in each cycle. As such, the cycle-by-cycle resource utilization is profiled so as to estimate the power consumption of an entire functional unit as a simulation object, rather than the detailed signals and circuits inside the functional unit. As a result, the MA simulator can obtain the cycle-accurate information for the functional units, while keeping the simulation overhead as low as possible. Thus, it gives a good trade-off between efficiency and accuracy.

\_

<sup>&</sup>lt;sup>3</sup> This refers to data dependency among instructions.

<sup>&</sup>lt;sup>4</sup> Memory requests include all memory access instructions (e.g. load and store, stack pop and push etc.) accessing the data cache and all instruction fetches to the instruction cache.

SimpleScalar [41] is one such MA simulator, used for architecture design and research. It originally supported the simulation of a single-core Alpha processor with out-of-order superscalar, and was subsequently extended to support the single-core PowerPC and ARM processor (referred to as SimpleScalar-ARM). However, SimpleScalar only simulates a uniprocessor without implementing the privileged instructions<sup>5</sup> used by the operating system. Moreover, it only supports simple system calls, with many of the critical system calls (e.g. process creation/switching (e.g. fork) and inter-process communication (IPC)) not being simulated. As such, multi-thread/process applications or operating systems cannot be simulated with SimpleScalar.

Brooks et al. [42] developed a toolset PowerTimer for use in early stage, microarchitecture level power and performance analysis of microprocessors. The main component of the toolset, Wattch [43], is an extension of SimpleScalar. Wattch is a set of parameterized power estimation functions (accumulating the resource utilization to get the power estimation) that can be integrated into SimpleScalar or any other cycleaccurate micro-architectural simulator. However, Wattch, is a uniprocessor power estimator and is not suitable for the multiprocessor case.

Eisley et al. [44] examined the high-level power analysis for CMP and MPSoC, which are both more complicated than the uniprocessor case as they must also consider the power consumption for intercommunication between cores. A power estimator called LUNA (link utilization for network power analysis) is used for estimating the power consumed by the NoC intercommunication network, which is faster than Orion (a bus simulator) and is able to maintain a good relative accuracy. In terms of the NoC power estimation, the utilizations of the key parts of the router (e.g. write/read buffer, crossbar and the (four directional) link) are recorded. However, only the utilization of the link is used (as a proxy for all the other parts), as ignoring the detailed power components improves the performance of the power estimator while still maintaining a good relative accuracy. Another contribution is that the network graph, used for tracking the utilization of the various functional units, allows a segment of code to be walked through for obtaining the functional unit utilizations. However, as the network graph cannot correctly analyse the instruction path for out-of-order-execution or for the speculation architecture, its power profiling is less accurate than that of a micro-

<sup>&</sup>lt;sup>5</sup>Control register instructions (e.g. the switch between supervisor mode and user mode) and co-process instructions (e.g. control page table, MMU, TLB and cache).

architecture level simulator. Moreover, the leakage power in the power analysis is always treated as a constant or even ignored, which can be a source of error, as the leakage power heavily depends on temperature which inversely impacts power consumption.

In summary, even though several simulators are available for academic research, power estimation and profiling for multiprocessor is not mature. These simulators (e.g. Simics and GEMS) simplify the processor implementation and do not provide cycle-accurate information. The inter-core communication in many simulators (e.g. Ruby and LUNA) is based on a message passing interface and is not compatible with the shared memory architecture used by many current multi-threaded applications.

#### **2.1.2** Online Power Profiling (Counter-based)

Online power profiling, also referred to as counter-based power profiling, is carried out directly on a real processor while an application is running. Since current processors do not provide runtime power information and no measuring devices are embedded into the package, direct online power profiling is not feasible. If a processor can dynamically provide the statistics of key functional units, the utilization of these functional units can be used for online power estimation. The performance counter in current state-of-the-art processors is a set of registers recording critical system events for different functional units, such as the number of cache hits/misses, the number of ALU accesses, and so on. For example, the performance counters in the older processors, such as the Compaq Alpha 21164 and the Intel Pentium II were able to count monitor 22 and 77 system events [45], respectively. More recent processors, such as the Intel Core-i7 [46] and the ARM Cortex-A9 [47] are able to count 97 and 58 system events, respectively. Based on the number of system events, the utilization of a functional unit in a certain period can be determined and hence the power can be estimated [48][49].

Russ et al. [45] proposed a heuristic utilization estimation based on the number of system events. As the performance counter can only measure a limited number of system events in the same time slot and cannot capture all system events in one cycle,

heuristic formulas are used to estimate the utilization. This work showed that accurate online power estimation using a counter-based approach was possible. In a similar way, Canturk et al. [48] used counter-based power profiling with heuristic estimation, on an Intel Pentium 4 processor. The results showed good correlation between the proposed counter-based profiling and the direct power measurement, and as such the procedure has been adopted by other researchers [49].

#### 2.1.3 Leakage Power Estimation and Profiling

The online/offline power profiling mentioned in last two sections are only effective for estimating dynamic power consumption on-chip. However, we have emphasized the importance of leakage power consumption, which due to reductions in the transistor feature size can no longer be neglected in current research. The leakage power consumption is usually regarded as a constant in much of the literature [51][54][55]. However, this is not the case in practice as the leakage power consumption is heavily affected by temperature. In this section, we examine the literature relating the relationship between leakage power and temperature.

The leakage power, also called the static power, consists of two parts: the sub-threshold leakage and the gate leakage [52], as:

$$I_{leakage} = I_{subthreshold} + I_{gate} = A_s \frac{W}{L} \left(\frac{kT}{q}\right)^2 e^{\frac{q(V_{GS} - V_{th})}{nkT}} + I_{gate}$$

(2.3)

where k and q are thermal voltage constants, n is the sub-threshold swing coefficient for the transistor, and  $A_s$  is a technology-dependent constant. L and W are the device effective channel length and width.  $V_{GS}$  and  $V_{th}$  are the gate-to-source voltage and threshold voltage respectively. T is the temperature.  $I_{gate}$  is primarily affected by the supply voltage and the dielectric thickness and is relatively insensitive to temperature [52][53]. Hence,  $I_{gate}$  is usually considered a constant or even negligibl<sup>6</sup> (particularly in the high temperature case). This leakage model is accurate at the transistor level for both MOS and FINFET circuits [53], however is not suitable at the module or system

<sup>&</sup>lt;sup>6</sup> If the temperature is greater than 50°C, the gate leakage is a small component of the total leakage, and the sub-threshold leakage is dominant.

level due to the computational overhead, and thus is unable to be applied to high level optimization and management.

Andrei et al. [54] consider the leakage power in their energy-aware scheduling process, but the leakage is assumed to be unaffected by temperature. Bao et al. [55] also use a similar assumption in their static energy-aware scheduling. However, in their later work [50], they improve the leakage calculation for dynamic scheduling scenarios. The following equation is used to evaluate the leakage power:

$$P_{leakage} = I_{sr} \cdot T^2 \cdot e^{\frac{\alpha \cdot V_{dd} + \beta \cdot V_{bs} + \gamma}{T}} \cdot V_{dd} + |V_{bs}| \cdot I_{ju}$$

(2.4)

where  $I_{sr}$  is the reference leakage current at the reference temperature,  $I_{ju}$  is the junction leakage current and  $V_{bs}$  is the body bias voltage.  $\alpha$ ,  $\beta$  and  $\gamma$  are technology dependent coefficients determined by curve fitting. These parameters are usually determined (or measured) prior to run-time, and only the temperature T and the voltage  $V_{dd}$  are changed dynamically.

The leakage power and temperature are interrelated, and hence determining the leakage power in a temperature-dependent scenario requires an iterative calculation to reach convergence between the leakage power and the temperature. This calculation usually requires several iterations, and is generally time consuming for an online algorithm. As a result, a reference table is built offline and is directly used for the online estimation. This leakage power model is used by a number of other researchers [52][53] at the micro-architecture level, however, the exponential component of the model increases the computational overhead, restricting its applicability for online purposes.

To reduce the exponential calculation, Liu et al. [52] use an efficient linear estimation for the leakage power. A piece-wise linear (PWL) function is used to map the relationship between the leakage power of a functional unit and its corresponding temperature. Experimental results, compared to those from HSPICE, showed that this technique was both accurate and reduced the computational overhead. An important theorem is developed [52], which states: "for all IC cooling configurations, as long as the total power input is constant, the sum of the IC area-temperature product in the active layer is also constant, if and only if, each power source has the same impact on

the average temperature of the active layer." Therefore, for CMP (where each core is regarded as a separate functional unit, e.g. a core level model for high level analysis) each core's leakage current  $I_{leakage}$  can be evaluated as:

$$I_{leakage} = F_{tech}S_{tot}(MT_{avg} + N)$$

(2.5)

where  $F_{tech}$  is the leakage current per unit area, and depends on the design style, the supply voltage, the manufacturing technology and the input pattern;  $S_{tot}$  denotes the area of the core and  $T_{avg}$  is the average temperature of the core; M and N are parameters obtained by curve fitting the piece-wise linear model. The accuracy of the estimation improves with an increased number of segments, with the 3-piecewise linear function being very close to the HSPICE results. In this work, this PWL is verified to have the capability that can replace the exponential part in most leakage power modelling and thus, is suitable for online thermal-aware scheduling due to its efficiency and accuracy.

The above research [50][52][53] analyses the leakage power from a pure temperature aspect, which means they are only concerned with the circuit itself and its inherent properties. In other words, if the physical parameters of the IC and the current temperature are known, the leakage power can be estimated. However, other research [56] shows that the leakage power is also affected by the dynamic power, i.e. a higher dynamic power also increases the leakage power, even at a constant temperature. This is because the leakage power changes with the charge/discharge in a circuit.

Sharon et al. [56] gave an empirical equation that shows the ratio r between the dynamic power and the static leakage power induced by the signal activities, as:

$$r = \frac{R_0}{V_0 T_0^2} e^{\frac{B_{tech}}{T_0}} \cdot VT^2 \cdot e^{\frac{-B_{tech}}{T}}$$

(2.6)

where  $T_0$  is the ambient temperature;  $R_0$  is the ratio between the dynamic power and the static leakage at  $T_0$  and nominal voltage  $V_0$ ; and  $B_{tech}$  is a process technology constant that depends on the ratio between the threshold voltage and the sub-threshold slope, and is computed using the leakage current and saturation drive current values from ITRS 2001.

Unfortunately, the above literature does not consider the computational complexity of the calculations, and particularly the online calculation overhead associated with the power and temperature iterations required for convergence. We have identified this as one of our challenges for achieving DTAS, and we will address this problem in more detail in Chapter 5.

#### 2.2 Temperature Estimation and Profiling

As seen earlier in Figure 2.1, there are 3 different techniques to get the temperature value needed for high level optimization purposes. These are: 1) estimating the temperature using a power/thermal model after profiling the power consumption; 2) directly estimating the temperature from the system events recorded in the performance counter; and 3) directly reading the digital thermal sensors (DTS) integrated on chip. These approaches are discussed in this section.

#### 2.2.1 Power/Thermal Model

After the power profiling is obtained, by either a simulator-based or counter-based approach, the temperature can be estimated using a power/thermal model. In this section, several related thermal models are introduced, including the simple uniprocessor model, the thermal RC network, the finite element method (FEM) and other empirical models.

Zhang et al. [57] applied the thermal RC model to a uniprocessor. The thermal characteristics and the electrical characteristics have a duality, where the voltage, current, resistance and capacitance in an electrical circuit are equivalent to temperature, power input, thermal resistance (the reciprocal of thermal conductivity) and thermal capacitance. The processor is abstracted as one node connecting the ambient temperature (abstracted as the ground) via one compact thermal resistance and capacitance <sup>7</sup>. This simple model is widely used in other STAS research

<sup>&</sup>lt;sup>7</sup> The thermal resistance denotes the heat dissipation rate between the core and the ambient temperature, while the thermal capacitance reflects the time interval of heating and cooling.

[58][51][59]. Since there is only one node with power input in entire thermal RC circuit, the core temperature can simply be expressed as:

$$T = T_0 \cdot e^{-RC} + T_s (1 - e^{-RC})$$

$$T_s = T_{amb} + RP$$

(2.7)

where  $T_0$  is the initial temperature,  $T_S$  is the steady-state temperature which is decided by the thermal resistance R and the power input P at the node, and C is the equivalent thermal capacitance. However, this single node model is unable to give the detailed temperature for each functional unit in the uniprocessor, nor is it suitable for the multiprocessor scenario where each core is abstracted as a power input node and the inter-core heat transferring should be considered.

Dhodapkar et al. [60] presented a cycle-accurate, flexible and scalable tool and framework for power and performance analysis using SimpleScalar [41] and Wattch [43]. Both dynamic power and static power are taken into account. Since static power and temperature are tightly coupled (as stated in a previous section), an iterative thermal computation is implemented in the analysis. The two main highlights that are relevant to our work are:

- Both an empirical mode and an analytical mode are proposed, allowing the user to select between efficiency and accuracy.

- A temperature factor is introduced into the power/performance evaluation to study the thermal management and power-temperature interaction, since subthreshold leakage and product reliability are exponentially related to temperature. However, this model regards the whole chip as a single uniform thermal resistance/capacitance, evaluating only the average temperature of the whole chip. Such a coarse-grained model may not be suitable to analyse the temporal and spatial thermal distribution on chip for different functional units at the micro-architecture level. Several useful equations (shown in Equation 2.8) are introduced for calculating the thermal distribution:

Heating:

$$\Delta T^+ = (T_{max} - T_{j-1}) \times [1 - exp(-1/\tau_{heat})]$$

Cooling:  $\Delta T^- = T_{j-1} \times [1 - exp(-1/\tau_{cool})]$  (2.8)

where  $\Delta T^+$  is the temperature increment,  $T_{max}$  is the maximum junction

temperature,  $T_{j-1}$  is the temperature of the previous cycle,  $\tau_{heat}$  is the thermal time constant in heating stage,  $\Delta T^-$  is the temperature decrement, and  $\tau_{cool}$  is the thermal time constant in the cooling stage. If instantaneous temperature generated by  $T_a + R_t \cdot P_j$  is greater than  $T_{j-1}$ , then  $T_j = T_{j-1} + \Delta T^+$ , else  $T_j = T_{j-1} - \Delta T^-$ , where  $T_a$  is the ambient temperature,  $T_j$  is the present cycle temperature,  $T_j$  is the equivalent thermal resistance, and  $T_j$  is the present cycle power dissipation.

Skadron et al. [35] developed a compact thermal model for architecture-level thermal analysis and optimization. The architecture-level is able to take advantage of the runtime knowledge of the application behaviour and the current temperature information of different on-chip functional units to adjust the execution and distribute the workload in order to optimize thermal behaviour. For the same reason, CMP can also benefit from such a model since each core can be regarded as a single coarse-grained functional unit that can execute a single thread for applications. The allocation of the workload at runtime is essential for core-level and high level thermal management and optimization. At the architecture level, a reliable thermal model is needed to reflect the current and future temperature variation in both temporal and spatial scales for the different functional units on chip.

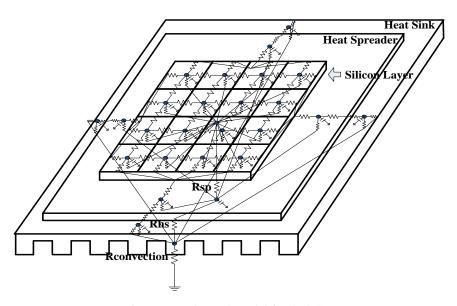

In terms of the architectural model of a chip, each functional unit can be abstracted into a piece of uniform material, with two adjacent units being connected via a thermal resistance R and a thermal mass (thermal capacitance) C, which are decided by the manufacturing process, the transistor density, the design complexity and the shared lateral area between the two adjacent functional units. Another contribution of [35] is the derivation of the equation to determine the lumped values of resistances and capacitances related to the material thickness and the area. The lumped R and C values can be obtained by experimentation or by using a low level simulator, e.g. HSPICE. Therefore, the temperature transient behaviour of the whole chip and its package can be modelled by a single integrated thermal model. This approach is suitable for architecture and higher level thermal estimation and analysis. Figure 2.2 shows the thermal circuit describing a  $4\times4$  core CMP.

Figure 2.2: Thermal model for 4×4 CMP

Usually, such a model includes several important layers: the silicon layer (the silicon layer is the active layer as this is where the heat is generated, represented as a power source injected into the thermal circuit), the heat spreader layer and the heat sink layer. Power from each functional unit is injected into the circuit at the corresponding node, and then the temperature (*T*) transient of each node can be described and constrained by the differential equations of Equation 2.9:

$$\begin{cases} C_{i} \frac{dT_{i}}{dt} = p_{i} + \sum_{j \in Path} \frac{T_{i} - T_{j}}{R_{j}}, \text{ node } i \in \text{silicon layer} \\ C_{i} \frac{dT_{i}}{dt} = \sum_{j \in Path} \frac{T_{i} - T_{j}}{R_{j}}, \text{ node } i \notin \text{silicon layer} \end{cases}$$

(2.9)

where  $C_i$  is the thermal capacitance of node i,  $T_i$  is node temperature as a function of the time t,  $p_i$  denotes the instantaneous power input at node i, Path is the set of all thermal conduction paths that connect with node i,  $R_j$  denotes the resistance of each thermal conduction path in Path, and  $T_j$  is the temperature of the adjacent node in each thermal conduction path. This equation indicates that the number of nodes determines the scale of the differential equation set, since each node represents one equation. Therefore, a large system with many functional units (or cores for core-level simulation) generates a large differential equation set, which requires a significant amount of computation to solve. For example, HotSpot [35] uses a  $4^{th}$ -order Runge-Kutta solver to process this equation set.

HotSpot [35][56] models the heat dissipation at a much finer granularity for different functional units at the micro-architecture level. It also considers the lateral resistances and the packaging, as well as dividing the heat dissipation layer into heat sink, heat spreader and internal layer. This detailed modelling can dramatically increase the accuracy of the temperature transient with time. HotSpot and its corresponding thermal models, along with SimpleScalar and Wattch, provide a standard platform for thermal simulation which is widely used in academia. As such, Hotspot has become an important reference and highly used tool for experiments and comparisons related to thermal-aware design and optimization.

However, while HotSpot is accurate, it has a high computational overhead making it unsuitable for use in dynamic (online) thermal optimization scenarios. Two methods [61][62] have been proposed that use the same thermal model as HotSpot, but improve the computational performance. Liu et al. [62] proposed a method that treats the power trace as a piecewise constant power input, and then uses fast spectrum analysis and a moment matching algorithm in the frequency domain to determine the steady state temperature and the transient temperature respectively. This approach gave a 10x-100x speedup, compared to the traditional HotSpot solver. Chen et al. [61] used a global adaptive method to optimize the step size of the iterations in HotSpot, and achieved a 38x--138x speedup. Paci et al. [27] use two different thermal modelling approaches on a 16-core ARM7-based CMP that includes a NoC infrastructure for inter-core communication. One of the models is similar to the previous thermal RC circuit-based model, and the other exploits the advantages of the finite element method (FEM) and corresponding tools (e.g. ANSYS[63] and COSMOL[64]) to analyse the temperature variation across the chip. FEM can provide a very accurate thermal distribution and a detailed temperature transient analysis, but at the cost of a very long computation time. Due to its accuracy, it is ideal as a reference for other thermal models or thermal estimation methods. The significant contribution is the comparison between FEM and the thermal RC network, which shows that the temperature errors of the thermal RC network are small (in the range  $0.1 \text{ to } 0.6^{\circ}\text{C}$ ).

Stavrou and Trancoso [65] developed a fully parameterizable tool for CMP thermal scheduling simulations, called TSIC, which allows the testing of different

configurations, application characteristics and scheduling policies. As TSIC is designed for CMP systems, the thermal model must reflect the spatial and temporal thermal diversities over the chip, and take into account the inter-core and ambient heat transfer, as well as the lateral heat dissipation. Notably, their approach does not use the thermal RC network of [35] to obtain an accurate thermal distribution in each time interval, but rather an intuitive empirical model, described by Equation 2.10, is adopted for updating the temperature of each core.

$$\Delta T_i = \left[\sum_{m=1, m \neq i}^{n} f_c(T_i - T_m)\right] - \left[f_a(T_i - T_{ambient})\right] - \left[f_p(Process_i, T_i)\right] \quad (2.10)$$

The first term in Equation 2.10, models the inter-core heat exchange, implying that such an exchange exists among any pair of cores on chip. For any pair of cores, A and B,  $f_c(T_A - T_B) = -f_c(T_B - T_A)$  must be satisfied. The function  $f_c$  is dependent on the difference in temperature of a pair of cores and the location of these two cores. The second term in Equation 2.13 indicates the heat dissipation from a core to the external environment  $(T_{ambient})$ . The function  $f_a$  also needs to consider the temperature difference and the core's location. For a core that is not on the chip edge, only the vertical thermal path is considered. The lateral thermal path is only considered for the outer cores. The last term of Equation 2.10 calculates the temperature change induced by executing the application (or process).

The model proposed in [65] improves the computation efficiency for temperature evaluation so as to be applicable for the online scenario. However, the model uses a time-driven approach which is only suitable for small-interval updates, using very fine granularity scheduling. This is because the temperature error becomes significant above 1 millisecond. Contrast this to the analytical model (thermal RC model), where any update interval is applicable.

Zhan et al. [66] proposed a novel approach to rapidly calculate the temperature distribution in VLSI chips by using the discrete cosine transform (DCT) and LUT. This approach improves on the previous temperature distribution algorithm that uses the Green's function [67] and the unrealistic assumption that the chip is infinitely large horizontally. Experimental results show that this approach is accurate, with a relative temperature error of less than 1%. The approach is suitable for a fine-grained

thermal analysis at the micro-architecture level since the computational overhead does not increase with the number of power sources (nodes on the active layer in the thermal RC model) and there is no need to solve a large set of differential equations. Unfortunately, the approach proposed in this paper only solves the steady state temperature distribution, and does not consider the transient profile as only the thermal resistance is taken into account while the thermal capacitance is ignored.

Michaud and Sazeides [68] used analytical methods to develop a temperature model, called ATMI. ATMI is based on an idealized microprocessor chip and its packaging. Partial differential equations are used to describe the physical model of ATMI (formed by two layers: the chip layer and the packaging layer) and its boundary conditions (the temperature and its first order differential on the cross-section of the adjacent layers and the lateral-section adjacent to the ambient). As ATMI is a linear model, and the multi-source power input can be solved by superposition of the individual power sources, the model produced accurate results, verified by the thermal sensors on chip. However, the convolution operation, used to obtain the temperature transient over time, is very time consuming, and thus is not computationally efficient enough for online thermal estimation and prediction in the OS, even when using the fast Fourier transform (FFT) to accelerate the convolution operation.

Computational efficiency and the accuracy of the power/thermal model are both critical in the thermal simulation, estimation and optimization topics mentioned above. The thermal models used in current research have several shortcomings: 1) Some thermal models (e.g. TEMPEST) are only used for uniprocessors, and cannot be applied to a multi-core scenario; 2) Some thermal models (e.g. TSIC) use inaccurate heuristic or empirical thermal modelling that is hard to adapt for different layouts and architectures; 3) Some thermal models [66][93][94] only consider the steady-state temperature and ignore the transient temperature because of the limitations in the solving algorithm (e.g. linear programming and DCT LUT), and thus the temperature error is large; 4) Some thermal models (e.g. HotSpot or the FEM approach) provide an accurate temperature estimation when used for offline thermal simulation, but require a computational overhead which makes them unsuitable for online thermal management; 5) Current thermal models (e.g. TSIC) are time triggered, and update the temperature in a fixed fine-grained time step, which adds to the computational

overhead; 6) Much of the research related to thermal-aware scheduling [90][92][57] assumes that the leakage power is invariant (that is a non-temperature-dependent leakage model is assumed). While these assumptions simplify the problem by skipping the power-temperature iteration, they can lead to unrealistic thermal results. Therefore, current thermal estimation and modelling does not sit well amongst the various competing factors: e.g. computational efficiency, estimation accuracy, updating period and leakage power.

#### 2.2.2 Direct Readings from Digital Thermal Sensors (DTS)

The simplest and most intuitive way to get the chip/core temperature is by reading the integrated on-chip DTS directly. A number of practical DTM and DTAS techniques [29][70][71][72] take advantage of DTS. However, DTS has some inherent disadvantages which can affect the high level thermal management and optimization. For example, if the DTS reading is lower than the actual temperature, DTM would be triggered and activated later than desired, which may result in the degraded reliability of the processor since the temperature may exceed the predefined threshold; if the DTS reading is higher than actual one, the early activation of DTM can significantly reduce the performance and waste computation resources. Even though DTS is widely used and accepted, there are some issues, particularly relating to its accuracy. In this section, we will focus on those issues.

Zhang [73], Rotem [74] and Sharifi et al. [75] described that the accuracy of DTS readings is a primary limitation. Several reasons can affect the accuracy of DTS reading.

• Noisy behaviour: In reality, on-chip DTSs are affected by a range of noise sources. Some of these noise sources include fabrication randomness, power grid noise, cross coupling, non-linear dependence between temperatures and the circuit parameters and even A/D converter accuracy. Assuming ideal thermal sensor operation can either lead to failure to detect overheating or false alarms that result in costly and unnecessary responses from the thermal management unit [73].

- Placement error: Typically, sensors cannot be placed exactly at the locations

where monitoring is critical, as these locations are high power density areas

(e.g. they are accessed frequently or are high performance components) where

silicon is at a premium. This means that the sensor cannot optimally capture

the chip hot spot [75].

- Calibration error: Many chip manufacturers use un-calibrated DTS due to the high cost and overhead associated with the thermal sensor calibration [75].

This is particularly the case for systems featuring multiple sensors and can result in significant thermal errors [75].

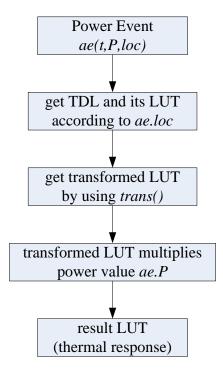

Sharifi et al. [75] also indicated that the current trend is that the number of DTSs per core is decreasing as the number of cores increases. For example, Intel's Core 2 Duo and AMD's Quad-Core Opteron processor have multiple DTSs on each core, while Intel's 48-core SCC only has one DTS for each core. However, in many-core systems, these sensor based approaches are likely to be even less practical. The future many-core systems may even group the cores into clusters which share the DTS among cores [76]. The reason is that more DTS needs more channels for routing, thus increasing the silicon area and test cost.