### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Sensitivity analysis of coupled interconnects for RFIC applications

Shi, Xiaomeng; Yeo, Kiat Seng; Ma, Jianguo; Do, Manh Anh; Li, Erping

2006

Shi, X., Yeo, K. S., Ma, J. G., Do, M. A., & Li, E. (2006). Sensitivity analysis of coupled interconnects for RFIC applications. IEEE Transactions on Electromagnetic Compatibility, 48(4), 607-613.

https://hdl.handle.net/10356/91414

https://doi.org/10.1109/TEMC.2006.884417

© 2006 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder. http://www.ieee.org/portal/site.

Downloaded on 09 Apr 2024 12:15:06 SGT

## Sensitivity Analysis of Coupled Interconnects for RFIC Applications

Xiaomeng Shi, Kiat Seng Yeo, *Member, IEEE*, Jian-Guo Ma, *Senior Member, IEEE*, Manh Anh Do, *Senior Member, IEEE*, and Er-Ping Li, *Senior Member, IEEE*

Abstract—This paper investigates the sensitivity of on-wafer coupled interconnects to the Si CMOS process parameters. Experiments are conducted to emulate state-of-the-art and future technologies. Some important parameters characterizing the coupled interconnects have been examined. The influence of the process parameters on transmission, reflection, near-end, and far-end crosstalk capacities of the coupled interconnects are discussed.

Index Terms—CMOS process, coupled interconnects, sensitivity.

### I. INTRODUCTION

THE recent decade has witnessed the explosion of the development of wireless communication. Portable devices such as pagers, cellular and cordless phones, global positioning system (GPS) devices, wireless local-area network (WLAN) devices, etc., have penetrated into all aspects of our daily lives. Boosted by the demands of this rapidly growing wireless mobile communication market, there is an increasing interest in the development of the radio frequency (RF) integrated circuit (IC). Because of the mature technology, low fabrication cost, high packing density, as well as low power consumption, complementary metal oxide (CMOS) technology has become a strong contender compared with other available technologies, such as the GaAs metal semiconductor field effect transistor (MESFET), heterojunction bipolar transistor (HBT), etc. [1].

Due to the combination of the increasing circuit complexity and higher operating frequencies of CMOS ICs, the circuit performance becomes more and more subjected to the interconnects [2]. On the other hand, the evolving pace of the CMOS process technology is truly spectacular. The process parameters are optimized to improve the circuit performance. However, influences of the process parameter variations on the interconnects have rarely been reported in the literature.

In our previous work [3], influences of the process parameters, such as conductivity of the substrate, thickness, and permittivity of the dielectric, as well as conductivity of the metallic conductor on the transmission and reflection capacities of the single interconnect, are examined. However, in a real case, the

Manuscript received February 22, 2006; revised September 4, 2006.

- X. Shi is with the Centre for Integrated Circuits and Systems, Nanyang Technological University, Singapore 639798, Singapore (e-mail: shixiaomeng@pmail.ntu.edu.sg).

- K. S. Yeo and M. A. Do are with the Division of Circuits and Systems, School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798, Singapore (e-mail: eksyeo@ntu.edu.sg; emado@ntu.edu.sg).

- J.-G. Ma is with the University of Electronic Science and Technology of China, Chengdu 610054, China (e-mail: jgma@uestc.edu.cn).

- E.-P. Li is with A-STAR Institute of High Performance Computing, Singapore, Singapore (e-mail: eplee@ihpc.a-star.edu.sg).

Digital Object Identifier 10.1109/TEMC.2006.884417

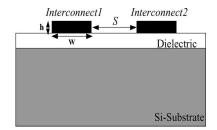

Fig. 1. Cross view of the test structure.

density of the interconnects are very high. The crosstalk among interconnects is one of the most important internal EMC problems [4]. Hence, it would be very useful to provide information about the sensitivity of the interconnects.

The objective of this paper is to investigate the sensitivity of two interconnects to the process parameters at radio frequencies. The dependance of the transmission, reflection, far-end, and near-end crosstalks of the two interconnects on the process parameters are investigated. This examination is dedicated to the interconnects on the top metal layer since it is most commonly allocated for routing critical high-frequency paths.

This paper is organized as follows. In Section II, the test structure is presented. The influences of the process parameters to the coupled interconnects are examined in Section III. Finally, the paper is concluded in Section IV.

### II. TEST STRUCTURE

In order to analyze the sensitivity of the two interconnects, a large number of interconnect samples with various process parameters are needed. There are two ways to obtain the required samples. The most straightforward one is to design and fabricate all the possible test structures with different process parameters. However, it is extremely costly, time-consuming, and impractical. An alternative way is to design and fabricate several typical test structures and adopt an electromagnetic (EM) simulator, using the fabricated samples to calibrate the EM simulator. Then, other possible interconnect stuctures can be investigated using calibrated EM simulation.

In this work, IE3D from Zeland Software Inc. is employed to do the EM simulations. The IE3D is a full-wave, method of moment (MOM) simulator and employs an automatic nonuniform mesh generator with rectangular and triangular cells [5].

The cross view of the test structure is shown in Fig. 1. Three sets of the test structures with various lengths and widths are designed and fabricated using a 0.18- $\mu$ m RF CMOS process by Chartered Semiconductor Manufacture Ltd. (CHRT). In order

Fig. 2. Top view of the test structure.

to calibrate the settings of the EM simulator, on-wafer measurements of the three sets of fabricated test structures are performed [6].

In the next section, the interconnect structure, as illustrated in Fig. 1, is examined. The length (L) of both the interconnects is 400  $\mu$ m, the width (W) is 10  $\mu$ m, the height (h) is 3.5  $\mu$ m, and the line spacing (S) of the two interconnects is 10  $\mu$ m. The top view of the structure and the assignment of the ports are shown in Fig. 2. Interconnect 1 is assumed to be the active line, and Interconnect 2 is assumed to be the victim line. An input signal is applied to port1. S-parameters, i.e.,  $S_{11}, S_{21}, S_{31}$ , and  $S_{41}$  are examined.

### III. INFLUENCES OF THE PROCESS PARAMETERS

Four major process parameters are considered, namely conductivity of the substrate, permittivity of the dielectric, thickness of the dielectric, and conductivity of the metallic conductor. During simulation, these four parameters are changed respectively. Only one parameter is changed each time, while the rest are kept unchanged. The variation range of the parameters is chosen to emulate the state-of-the-art and future Si CMOS technologies.

### A. Conductivity of the Substrate

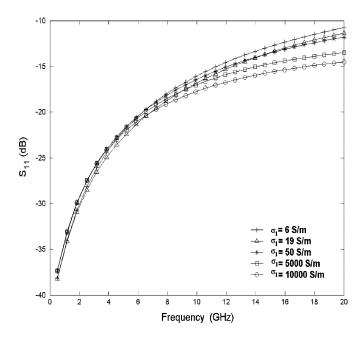

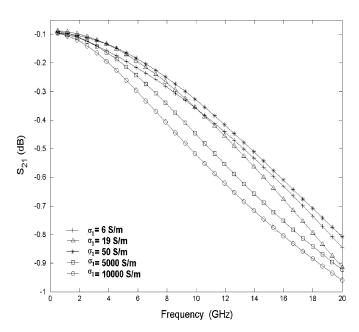

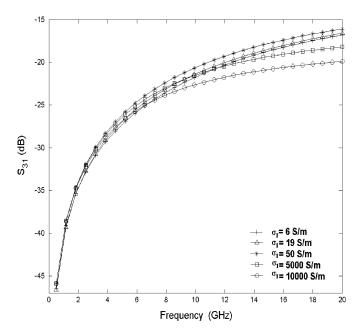

In CMOS technology, low-resistivity substrate is used to improve the yields and suppress the latchup. The performance of the on-wafer interconnects is significantly affected by the lossy nature of the silicon substrate [7]. In the current technology, the substrate conductivity ( $\sigma_1$ ) is approximately 6–50 S/m (2–18  $\Omega$ -cm) [8]. In some processes, the conductivity of the substrate may reach as high as  $5\times 10^3$  to  $1\times 10^4$  S/m (10–20 m  $\Omega$ -cm) [9].

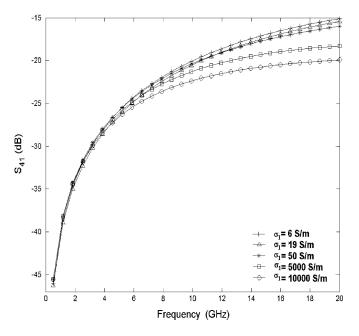

In order to study the influence of the substrate conductivity, typical values of 6, 50,  $5 \times 10^3$ , and  $1 \times 10^4$  S/m as well as 19 S/m, which is provided by the CHRT process, are used for the simulation. Comparisons of  $S_{11}, S_{21}, S_{31}$ , and  $S_{41}$  are shown in Figs. 3–6, respectively.

For  $S_{11}$ , as shown in Fig. 3, it is observed that both its dependence on the substrate conductivity and the corresponding values are the same as that of the depicted single interconnect in [3]. It indicates that the reflection of the active line is not influenced much by the appearance of the victim line. For  $S_{21}$ , it follows the same dependent trend [3]. However, there is an interesting phenomenon that can be noticed in Fig. 4. For low conductivities, the corresponding values of  $S_{21}$  are smaller than those of the single interconnect in [3]. However, for interconnects with very high substrate conductivities, i.e., 5000 and 10 000 S/m, the values of  $S_{21}$  do not change much from those

Fig. 3. Comparison of  $S_{11}$  with respect to various substrate conductivities.

Fig. 4. Comparison of  $S_{21}$  with respect to various substrate conductivities.

of the single interconnect. The reason is that the energy loss caused by the coupling can be neglected compared to the substrate losses due to a high conductivity of the substrate. Figs. 5 and 6 illustrate the crosstalks at the far and the near-end of the victim interconnect. It can be observed that the interconnect with larger  $S_{11}$  has larger near-end crosstalk, while the interconnect with larger  $S_{21}$  suffers more from far-end crosstalk. This is because the energy in the victim line is originated from the energy in the active line. Given the same dielectric permittivity and interconnect physical dimension, the coupling capacitance [10] of the two interconnects is identical. The more the energy at the active line, the more the coupled energy at the corresponding victim line.

Fig. 5. Comparison of  $S_{31}$  with respect to various substrate conductivities.

Fig. 6. Comparison of  $S_{41}$  with respect to various substrate conductivities.

### B. Distance From the Substrate

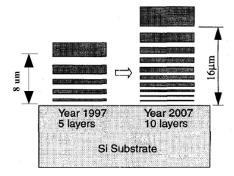

The current trend of the metal technology evolution is shown in Fig. 7. Due to the increase of the metal layers, the vertical dimensions do not scale down with the horizontal dimensions. When it comes to 2007, there will be up to 10 metal layers, and the top metal layer will be away from the Si substrate up to  $16~\mu m$  [11].

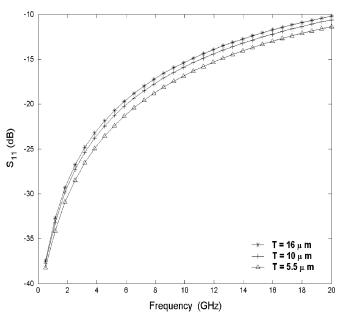

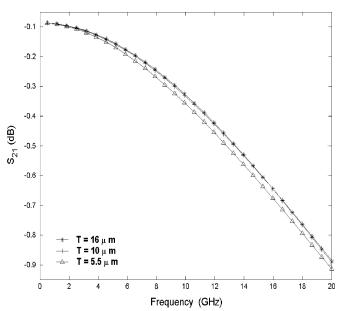

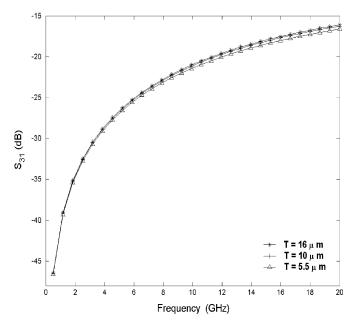

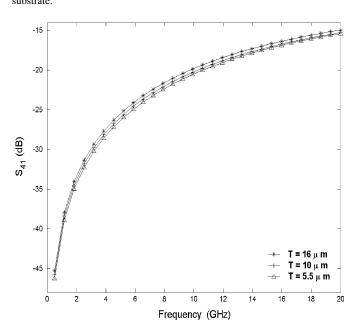

From Figs. 8–11, comparisons of  $S_{11}$ – $S_{41}$  with different top metal distances (T) from the substrate are illustrated. Three chosen distances are 5.5  $\mu$ m, which is provided by CHRT; 16  $\mu$ m, which is the predicted value for the year 2007; and 10  $\mu$ m, which is the value in between.

Fig. 7. Trend of interconnect stack.

Fig. 8. Comparison of  $S_{11}$  with respect to various distances from the substrate.

Fig. 9. Comparison of  $\mathcal{S}_{21}$  with respect to various distances from the substrate.

Fig. 10. Comparison of  $S_{31}$  with respect to various distances from the substrate.

Fig. 12. Comparison of  $S_{11}$  with respect to various dielectric permittivities.

Fig. 11. Comparison of  $S_{41}$  with respect to various distances from the substrate.

Fig. 13. Comparison of  $S_{21}$  with respect to various dielectric permittivities.

For  $S_{11}$ , as shown in Fig. 8, both its dependence on the substrate conductivity and the corresponding values are the same as those of the depicted single interconnect in [3]. It indicates that the reflection of the active line is not influenced much by the appearance of the victim line. For  $S_{21}$ , the same dependent trend can be noted. However, the corresponding values are smaller than those of the single interconnect in [3]. The reason is that a portion of the input energy has been coupled to the victim line.

Figs. 10 and 11 demonstrate that the coupling is more severe for the interconnects located further from the substrate. As is known, metal layers further away from the substrate are recommended for critical interconnects to reduce the substrate losses. However, it is noticed from our investigation that the thicker dielectric does not bring in merit only, but severer coupling is also caused in the meantime, which downgrades circuit performance.

### C. Permittivity of the Dielectric

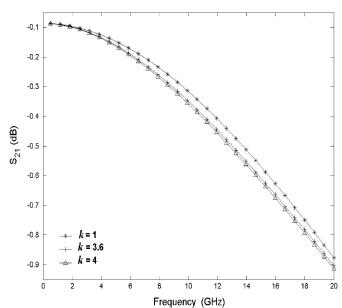

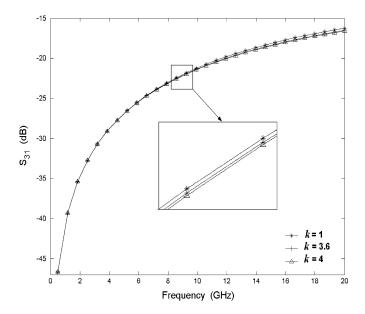

Recently, numerous low-k materials spanning a wide range of dielectric constants, from air (k = 1) to fluorinated oxides (k = 3.6), have been explored for interconnect systems [12].

The values of 4.0 (parameter of the fabricated structures), 3.6, and 1 are used as the relative permittivity (k) of the dielectric for the simulation. The values correspond to the traditionally used silicon dioxide and novel low-k materials. Corresponding

Fig. 14. Comparison of  $S_{31}$  with respect to various dielectric permittivities.

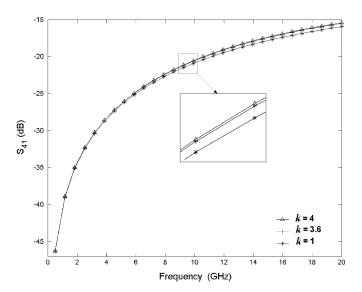

Fig. 15. Comparison of  $S_{41}$  with respect to various dielectric permittivities.

comparisons of  $S_{11}$ – $S_{41}$  are given in Figs. 12–15, respectively. As shown in Figs. 12 and 13, both  $S_{11}$  and  $S_{21}$  are inversely proportional to the relative permittivity of the dielectric. It follows the same trend as the single interconnect in [3]. From Fig. 15, it can be observed that the interconnect structure with higher dielectric permittivity suffers more near-end crosstalk. As presented in (1), given the same physical dimension (A and d, i.e., the area of each plane electrode and the separation between the electrodes, respectively), the structure with larger dielectric permittivity (k) has larger coupling capacitance. With the same energy in the active line, the larger the coupling capacitance, the greater the coupling capacity. Therefore, the near-end crosstalk is proportional to k:

$$C = \varepsilon_0 \frac{k\mathbf{A}}{d} \tag{1}$$

Fig. 16. Comparison of  $S_{11}$  with respect to various metallic conductor conductivities.

Fig. 17. Comparison of  $S_{21}$  with respect to various metallic conductor conductivities.

The far-end crosstalk, as shown in Fig. 14, is inversely proportional to the dielectric permittivity. This can be understood as the crosstalk is affected by both the coupling capacitance and the energy in the active line. Interconnects with larger k have larger coupling capacitances but smaller transmitted energy at the far-end port, which is characterized by  $S_{21}$ .

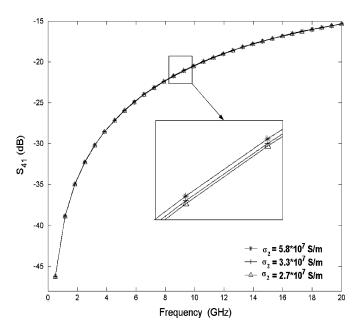

### D. Conductivity of the Metallic Conductor

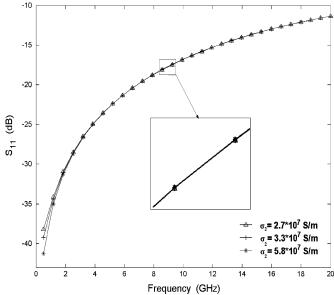

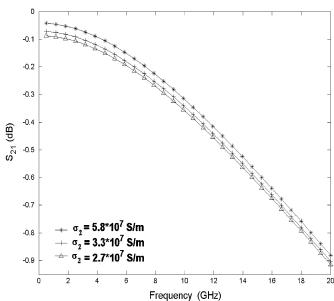

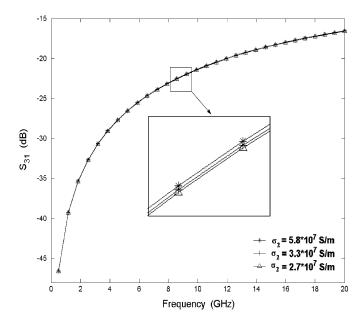

Due to its higher conductivity  $(\sigma_2)$  ( $\sim 5.8 \times 10^7$  S/m), copper metallization has been introduced for the aggressive interconnects instead of traditional Al ( $\sim 2.7 \times 10^7$  S/m) (used by the fabricated structures) or AlCu ( $\sim 3.3 \times 10^7$  S/m) metallization [12].

Fig. 18. Comparison of  ${\cal S}_{31}$  with respect to various metallic conductor conductivities.

Fig. 19. Comparison of  $\mathcal{S}_{41}$  with respect to various metallic conductor conductivities.

As shown in Fig. 16, at low frequency,  $S_{11}$  is inversely proportional to  $\sigma_2$ . However, when the frequency approaches several gigahertz, the influence of  $\sigma_2$  on  $S_{11}$  becomes negligible. The reason is that at high frequency, the impedance is dominated by the inductance and capacitance instead of resistance.  $S_{21}$  in Fig. 17 follows the same trend in [3], while the transmission capacity  $(S_{21})$  is slightly downgraded compared to the single interconnects because of the energy coupling. From Figs. 18 and 19, it is observed that the interconnects with larger conductivity suffer slightly more from coupling than those with lower conductivities. It can be understood that the conductor with higher conductivity has larger currents and hence a larger induced mag-

netic field and severer coupling. However, at high frequencies, the resistance is not dominant compared with inductance. Therefore, as shown in Figs. 18 and 19, couplings are not strongly affected by the variations in the conductor's conductivities.

### IV. CONCLUSION

The sensitivity of on-wafer coupling interconnects of current and future Si CMOS technologies has been investigated based on the calibrated deck of a 0.18- $\mu$ m RF CMOS process. With comparisons to the sensitivity study of a single interconnect in [3], it is observed that the reflection  $(S_{11})$  and transmission  $(S_{21})$  of the coupled interconnects follow the same trend when the process parameters (conductivity of the substrate, permittivity of the dielectric, thickness of the dielectric, and conductivity of the metallic conductor) vary. Both the far-end crosstalk  $(S_{31})$ and the near-end crosstalk  $(S_{41})$  are proportional to the conductivity of the conductors and the distance between the conductors and the substrate. It is highlighted that although further distance between the interconnects and the substrate can reduce the effect of substrate losses, severer coupling is caused, which will downgrade the circuit performance. Hence, a tradeoff must be made. As for the dielectric permittivity,  $S_{31}$  is inversely proportional to it, while  $S_{41}$  has a proportional relationship. The impact of the substrate conductivity is more complicated. No monotonic relationship can be observed.

### REFERENCES

- [1] X. Shi, J.-G. Ma, K. S. Yeo, M. A. Do, and E. Li, "Equivalent circuit model of on-wafer CMOS interconnects for RFICs," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 13, no. 9, pp. 1060–1071, Sep. 2005.

- [2] X. Shi, J.-G. Ma, B. H. Ong, K. S. Yeo, M. A. Do, and E. Li, "Equivalent circuit model of interconnect bends based on S-parameter measurements," *Microw. Opt. Technol. Lett.*, vol. 45, no. 2, pp. 170–173 2005.

- [3] X. Shi, J.-G. Ma, E. Li, K. S. Yeo, and M. A. Do, "Sensitivity of on-wafer interconnects to CMOS process parameters at radio frequency," in *Proc.* 16th Int. Zurich Symp. EMC, Zurich, Switzerland, Feb. 2006, pp. 590–594.

- [4] T. R. Gazizov, "Far-end crosstalk reduction in double-layered dielectric interconnects," *IEEE Trans. Electromagn. Compat.*, vol. 43, no. 4, pp. 566–572, Nov. 2001.

- [5] IE3D Manual, I. Zeland Software, 2002.

- [6] X. Shi, K. S. Yeo, J.-G. Ma, M. A. Do, and E. Li, "Scalable model of on-wafer interconnects for high-speed CMOS ICs," *IEEE Trans. Adv. Packag.*, to be published.

- [7] J. Zheng, Y. Hahm, V. K. Tripathi, and A. Weisshaar, "CAD-oriented equivalent circuit modeling of on-chip interconnects on lossy silicon substrate," *IEEE Trans. Microw. Theory Tech.*, vol. 48, no. 9, pp. 1443–1451, Sep. 2000.

- [8] A. Deutsch, P. W. Coteus, G. V. Kopcsay, H. H. Smith, C. W. Surovic, B. L. Krauter, D. C. Edelstein, and P. L. Restle, "On-chip wiring design challenges for gigahertz operation," *Proc. IEEE*, vol. 89, no. 4, pp. 529– 555, Apr. 2001.

- [9] B. Kleveland, C. H. Diaz, L. Madden, T. H. Lee, and S. S. Wong, "Exploiting CMOS reverse interconnect scaling in multigigahertz amplifier and osillator design," *IEEE J. Solid-State Circuits*, vol. 36, no. 10, pp. 1480–1489, Oct. 2001.

- [10] Y. Eo, W. R. Eisenstadt, J. Y. Jeong, and O.-K. Kwon, "A new on-chip interconnect crosstalk model and experimental verification for CMOS VLSI circuit design," *IEEE Trans. Electron Devices*, vol. 47, no. 1, pp. 129–142, Jan. 2000.

- [11] B. Kleveland, T. H. Lee, and S. S. Wong, "50-GHz interconnect design in standard silicon technology," in *Proc. IEEE MTT-S Int. Microw. Symp. Dig.*, vol. 3, 1998, pp. 1913–1916.

- [12] R. H. Havemann and J. A. Hutchby, "High-performance interconnects: An integration overview," *Proc. IEEE*, vol. 89, no. 5, pp. 586–601, May 2001.

modeling.

Xiaomeng Shi received the B.Sc. degree in microelectronics from Peking University, Beijing, China, in 2003. Currently, she is working toward the Ph.D. degree at the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore.

Currently, she is a Project Officer at the Centre for Integrated Circuits and Systems, Nanyang Technological University. Her current research interests include on-wafer interconnects modeling and radio frequency integrated circuit (RFIC) device

**Kiat Seng Yeo** (M'00) received the B.E.(Hons.) degree in electronics and the Ph.D. degree in electrical engineering from Nanyang Technological University, Singapore, in 1993 and 1996, respectively.

In 1996, he joined the School of Electrical and Electronic Engineering, Nanyang Technological University, as a Lecturer, and became an Assistant Professor and an Associate Professor in 1999 and 2002, respectively. He was appointed as Sub-Dean (Student Affairs) in 2001 and Head of the Department of Circuits and Systems in 2005. He provides

consultancy services to statutory boards and multinational corporations in the areas of semiconductor devices and electronic circuit design. He has been extensively involved in the modeling and fabrication of small MOS/bipolar integrated technologies for the last 12 years. His current research interests include the design of new circuits and systems (based on scaled technologies) for low-voltage low-power applications, radio frequency integrated circuit (RFIC) design, integrated circuit design of BiCMOS/CMOS multiple-valued logic circuits, domino logic and memories, and device characterization of deep submicrometer MOS-FETs.

**Jian-Guo Ma** (SM'97) received the B.Sc. and M.Sc. degrees (with honors) in electrical engineering from Lanzhou University, Lanzhou, China, in 1982 and 1988, respectively. He received the Doctoral degree in engineering from Gerhard-Mercator University, Duisburg, Germany, in 1996.

From 1982 to 1991, he was with Lanzhou University, where he worked on RF and microwave engineering. He then joined the Technical University of Nova Scotia, Halifax, NS, Canada. From 1997 to 2005, he was an Associate Professor and a Direc-

tor of the Center for Integrated Circuits and Systems, Nanyang Technological University, Singapore. Currently, he is with the University of Electronic Science and Technology of China (UESTC), Chengdu, China. His current research interests include RFIC designs for wireless applications, RF characterization and modeling of semiconductor devices, RF interconnects and packaging, SoC, and applications and electromagnetic compatibility/electromagnetic interference (EMC/EMI) in RFICs. He is the author or coauthor of more than 180 technical papers and two books. He is a holder of seven patents in CMOS RFICs

Dr. Ma is now an Associate Editor for the IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

Manh Anh Do (SM'05) received the B.Sc. degree in physics from the University of Saigon, Saigon, Vietnam, in 1969. He received the B.E.(Hons.) degree in electronics and the Ph.D. degree in electrical engineering from the University of Canterbury, Canterbury, New Zealand, in 1973 and 1977, respectively.

From 1977 to 1989, he was a Research and Development Engineer and a Production Manager at Radio Engineering Ltd., a Research Scientist at Fisheries Research Centre, New Zealand, and a Senior Lec-

turer at the National University of Singapore. In 1996, he was a Senior Lecturer at the School of Electrical and Electronic Engineering, Nanyang Technological University (NTU), Singapore, where he became an Associate Professor in 1996 and a Professor in 2001. He has been a Consultant for many projects in the Singapore electronic industry. From 1990 to 2001, he was the Principal Consultant for the design, testing, and implementation of the 200 million Electronic Road Pricing (ERP) island-wide project in Singapore. His current research interests include digital and mobile communications, RFIC design, mixed-signal circuits, and intelligent transport systems. He is the author or coauthor of more than 180 published papers in the areas of electronic and communication circuits and systems. Between 1995 and 2005, he was the Head of the Division of Circuits and Systems, School of Electrical and Electronic Engineering, NTU, a Chartered Engineer (UK), and a Professional Engineer (Singapore). Currently, he is the Director of the Centre for Integrated Circuits and Systems (CICS) of NTU.

Dr. Do was a Council Member of Institution of Electrical Engineers (IEE), U.K., from 2001 to 2004. He is a Fellow of the IEE. Since April 2005, he has been an Associate Editor for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

**Er-Ping Li** (SM'01) received the Ph.D. degree in electrical engineering from Sheffield Hallam University, Sheffield, U.K., in 1992.

During 1989–1990 and 1991–1992, respectively, he worked as a Research Fellow and as a Lecturer with the School of Electronic and Information Technology, Sheffield Hallam University. From 1993 to 1999, he was a Senior Research Fellow and Principal Research Engineer with the Singapore Research Institute and Industry. Since 2000, he has been with A-STAR Institute of High Performance Computing,

Singapore, where he is currently a Senior Scientist and Senior Research and Development Manager of the Computational Electromagnetics and Electronics Research Division. He has been invited to give numerous speeches to academic institutions and international conferences. He has filed three U.S. patents. He is the of more than 100 technical papers in international referred journals and conferences and a co-author of three book chapters. His current research interests include fast and efficient computational electromagnetics, electromagnetics for high-speed electronic packaging/nanoelectronics and RFIC, and electromagnetics for biomedical applications.

Dr. Li was the President for the 17th International Zurich Symposium on EMC held in March 2006 in Singapore. He is currently a Chairman of the IEEE EMC Singapore Chapter, Guest Editor of the IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY NOVEMBER SPECIAL ISSUE, and Associate Editor of the IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.