# Fully Symmetrical Monolithic Transformer (True 1:1) for Silicon RFIC

Chee Chong Lim, Kiat Seng Yeo, *Member, IEEE*, Kok Wai Chew, *Member, IEEE*, Alper Cabuk, *Member, IEEE*, Jiang-Min Gu, Suh Fei Lim, Chirn Chye Boon, and Manh Anh Do, *Senior Member, IEEE*

Abstract—A novel on-chip transformer configuration that gives an identical inductor pair, a higher individual coil self-resonant frequency (SRF), and excellent area efficiency are presented. This technique involves the unique way of inter-crossing the transformer's primary and secondary coils using multiple metallization layers. Truly symmetrical transformer configuration (100%) is demonstrated using minimum die size. Thus, a true 1:1 transformer has been realized on silicon. The effects of the parasitic within the transformer are represented by an equivalent-circuit model. Accurate semiempirical expressions describing the circuit components are provided based on the various layout parameters. Of all the transformer structures presented, the two designs occupying the minimum silicon area by a factor of  $> 2 \times$  have been selected for performance evaluation of the SRF, coupling coefficient, input impedance, quality factor, and inductance. The transmission line transformer mode has also been studied to examine the designs' performance in the differential mode. The second proposed design reported in this paper, with enhancements in S21 and k performance, is created by adding a unique routing technique onto the first proposed structure. The method presented is fully compatible with the standard foundry CMOS processes. The silicon data reported in this study are based on Chartered Semiconductor Manufacturing's 0.13-µm RF CMOS technology

Index Terms—Area efficiency, coupling coefficient, differential inductor, fully symmetrical transformer, identical inductor pair, inter-coil crossing, interleaved transformer, multidirectional coupling, RF CMOS, self-resonant frequency (SRF), stacked transformer, system-on-chip (SoC), transmission line transformer (TLT).

# I. INTRODUCTION

HE HIGH demand for system-on-chip promotes the interest of integrating on-chip transformers for RF CMOS applications. Due to the physical isolation property of the transformer, it can be easily exploited to implement several functional blocks such as impedance matching, low-noise feedback, differential-to-single-ended conversion, and input differential-mode inductor pair [1]–[4].

In recent years, on-chip transformers have become more profound in high-frequency applications. This is mainly because many RF integrated circuit (RFIC) designers started to integrate transformer blocks with voltage-controlled oscillators (VCOs), power amplifiers (PAs), etc. [5]–[8]. The majority of the research done has shown enhancement in circuit performance

Manuscript received March 25, 2008; revised July 25, 2008. First published September 23, 2008; current version published October 8, 2008.

The authors are with the Division of Circuits and Systems, Nanyang Technological University, Singapore 639798 (e-mail: limc0042@ntu.edu.sg)

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2008.2003531

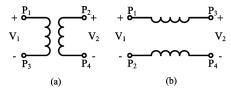

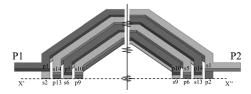

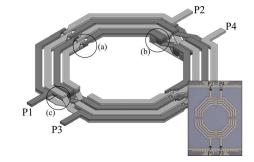

Fig. 1. (a) FL transformer mode. (b) TLT mode.

compared to that of a nontransformer integrated design. In general, the key advantage of using a transformer is the ability to reduce the large silicon area consumption by as high as 50%. This reduction has become a figure-of-merit, as the silicon area is a limiting factor in current and future RFIC designs.

A transformer is primarily designed to couple alternating current from one winding to the other without significant loss of power. Impedance levels between the windings are transformed in the process as the ratio of the terminal voltage to current flow changes across windings. In addition, direct current flow is isolated by the transformer, allowing the windings to be biased at different potentials. A microstrip line is the simplest on-chip element for monolithic implementation of an inductor. Interwinding or overlapping of the microstrip inductors to magnetically coupled independent conductors results in a simple monolithic transformer [3].

Commonly, there are two main types of transformer structure, i.e., the interleaved and stacked transformer, which are widely used in two different transformer modes (i.e., flux-linkage (FL) and transmission line transformer (TLT) mode [9] [refer to Fig. 1(a) and (b)]). Many RFIC designs such as VCOs, low-noise amplifiers (LNAs), and mixers prefer a fully differential architecture in order to suppress common-mode noise. In these circuits, one fully symmetrical passive component can be adopted to replace two asymmetric ones in the differential paths so as to save chip area and cost. Most importantly, by means of the miniaturized symmetric architecture, the effective inductance can be increased by inherent mutual coupling. Usually, the FL transformer is limited to lower frequency applications by its inherent distributed winding capacitance. Thus, the TLT mode is introduced for higher frequency applications. In fact, the TLT mode design requires a pair of fully symmetrical coils. The ideal way of constructing the TLT, using transmission lines, is often too bulky for high inductance applications. The area needed to build a pair of high inductance transmission lines is too large. Therefore, an alternative solution comprised of monolithic transformers has been introduced to realize an on-chip TLT by trading off the bandwidth as compared to the conventional transmission line design.

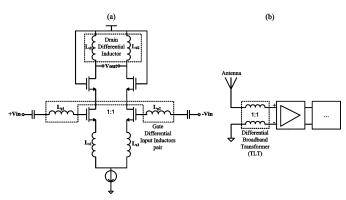

Fig. 2. Fully symmetrical (1:1) transformer used as: (a) drain and input differential inductor pairs in simple differential LNA design [15] and (b) input stage of the system as differential broadband transformer in TLT configuration.

Significant efforts have already been reported in the literature that aim at characterizing the existing transformer design [3], [10], [11]. In general, achieving a turn ratio of 1:n is proven to be relatively simpler than realizing an ideal 1:1 fully symmetrical transformer in the monolithic implementation [3]. It is well known that the real world monolithic transformers, be it interwinding or overlapping of the coils, have problems such as the different finite metal line resistances on various backend layers, unmatched finite inductances between the primary and secondary coils, and imperfect power losses, especially with a lossy silicon substrate. With the challenge identified, [12] and [13] have proposed a new type of transformer structure that demonstrates a nearly 1:1 ratio design. However, a *True 1:1* transformer on-chip has yet to be developed. Some general circuit applications for a fully symmetrical device are shown in Fig. 2. In [14], Kluge et al. has highlighted that a symmetric differential inductor is proven to be better in suppressing commonmode signals instead of two single-ended inductors. However, using conventional differential inductor, it does not have true symmetricity property. The coupling coefficient is low and the area consumption is usually very high for large inductance applications. Thus, a fully symmetrical transformer connected as a differential inductor is one of the solutions to this limitation.

The need for a fully symmetrical transformer extends to unconventional circuits as well such as an *LC*-VCO [16]. In [16], it requires an electrically symmetrical structure to form the parallel *LC*-tank that yields identical inductance and resistance values.

In this study, two novel monolithic fully symmetrical transformer designs are proposed and compared with the existing transformer structures. The first proposed design demonstrates better performance in terms of area efficiency, self-resonant frequency (SRF), and symmetry. An equivalent-circuit model that shows good agreement to the measured novel transformer is also reported in this study using accurate geometry-based equations. The tradeoff option between the SRF and S21 and k are introduced in the second proposed design, offering more flexibility to RFIC designers.

This paper is organized as follows. In Section II, the detailed introduction for the first proposed fully symmetrical transformer (FST1) is discussed together with its proposed equivalent lumped-circuit model. In Section III, having the

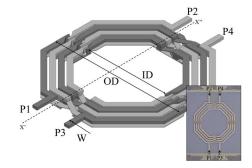

Fig. 3. 3-D view of the FST1 and  $0.13-\mu m$  silicon die photograph.

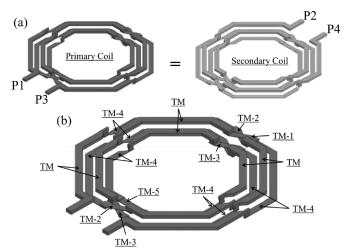

Fig. 4. (a) Virtual separation of the primary and secondary coil that depicts the fully symmetrical property of the FST1. (b) Layers description of the FST1 based on one of the coils.

inductance as a benchmark, a silicon area comparison is carried out for all different types of configurations. Subsequently, the transformers are normalized to the smallest device size for performance evaluation based on same on-chip area. In the latter part of Section III, the second proposed fully symmetrical transformer (FST2) is introduced, demonstrating enhancements to the transformer's S21 and k performance. Finally, a conclusion is drawn in Section IV.

#### II. NOVEL FULLY SYMMETRICAL TRANSFORMER

## A. Description

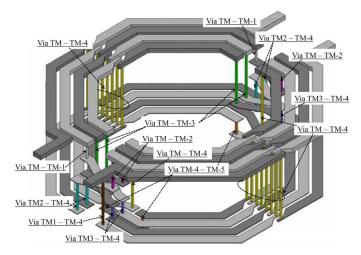

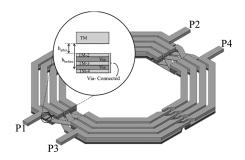

The FST1 has its primary and secondary coils inter-crossed, equalizing the physical aspect of the two windings [17]. The concept of the design is based on using several metallization layers as interconnects to achieve inter-coil crossing. Thus, the impedance looking into the two windings are expected to be identical. The 3-D view of the FST1 is depicted in Fig. 3 together with its silicon die photograph.

The structure consists of four segments. Each quadrant will experience a switching from the top layer to the corresponding bottom layer. The fully symmetrical property of the design can be illustrated by virtually separating the two coils from their inter-crossing, as shown in Fig. 4(a). Each coil will be experiencing an equal amount of various metallization layers, while maintaining the same physical length (number of turns, irrespective of the layers). For example, Fig. 4 demonstrates a four-turn

Fig. 5. Cross-sectional view of the FST1 along X'-X'', as shown in Fig. 3.

Fig. 6. 3-D exploration view of the FST1 with detail vias mapping.

transformer design with each coil having eight quadrants of both the top and bottom layers. It is clearly visible that the two coils are, in fact, identical. They are integrated with  $180^{\circ}$  difference in the port orientation.

In the conventional transformer design, the mutual coupling is *unidirectional*, either laterally or vertically. However, in the FST1, a *multidirectional* mutual coupling can be achieved. Fig. 5 illustrates this process using the cross-sectional view of the proposed design along the X'-X'' axis. Quadrant s6 is not limited to vertical coupling provided by quadrant p5, it has quadrant p9 and p13 contributing to the lateral coupling. Thus, the mutual coupling of the FST1 is expected to improve. The routing of the design must also ensure the current travels only in one direction within the same coil. This is crucial, as the reverse current will result in a negative self-inductance effect that substantially reduces the overall coil inductance.

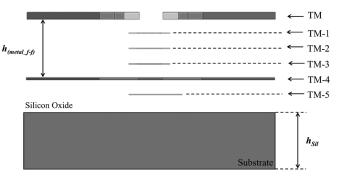

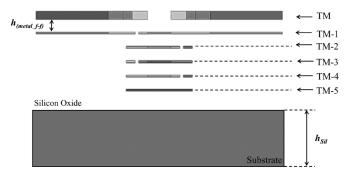

The proposed transformer's novel way of inter-coil crossing method, requires six metallization layers as shown in Fig. 4(b). By expanding the 3-D view of the design shown in Fig. 6, it reveals the detailed via mapping of the FST1. The vertical deck of the metal layers is illustrated in Fig. 7. TM and TM-4 are the layers forming the turns quadrant, whereby TM-1, TM-2, TM-3, and TM-5 are used to form underpasses and overpasses for this design. TM being the topmost metal layer and TM-5 being the bottommost layer.

## B. Equivalent Lumped-Circuit Model

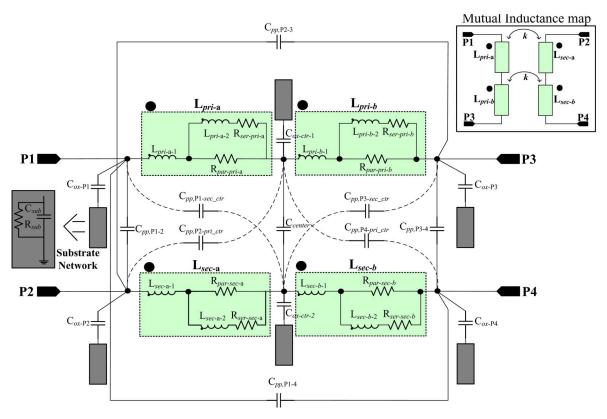

Generally, a simple two-port lumped-circuit element is sufficient to model all multiport devices, as one or more ports will be grounded in most practical circuit applications. However, for this fully symmetrical device, the model with independently driven terminals is much more appropriate in showing the cred-

Fig. 7. Vertical metallization profile of the FST1 design.

ibility of the differential mode applications. Fig. 8 illustrates the proposed equivalent lumped-circuit model for the novel design. The electrical model of this design is relatively simpler as compared to the conventional transformer. This is because both winding are identical, requiring only single branch solutions. The proposed design's turns are described by ideal inductors together with resistors in a ladder network, as suggested in [18] and [19]. The magnetic coupling coefficient are modeled in terms of k. The port-to-port capacitive effects from various nodes are captured with  $C_{pp,P2-3}$ ,  $C_{pp,P1-4}$ ,  $C_{pp,P1-\sec\_ctr}$ ,  $C_{pp,P2-pri\_ctr}$ ,  $C_{pp,P3-\sec\_ctr}$ , and  $C_{pp,P4-pri\_ctr}$ , whereas  $C_{ox,P1}$ – $C_{ox,P4}$  models the parasitic capacitance of the device to the silicon substrate. The entire substrate network (silicon area beneath the device) is separated into six blocks of  $C_{\rm sub}$  and  $R_{\rm sub}$  to better model the distribution effect of the lossy substrate.

1) Series Inductance and Resistance: Extensive effort has been reported in finding an accurate analytical expression for the self-inductance. In this study, a well-known formula suggested by Mohan *et al.* [20] is used as follows in (1):

$$L_{\text{DC}} = \frac{\mu \times n^2 \times d_{\text{avg}} \times c_1}{2} \left( \ln \left( \frac{c_2}{\delta} \right) + c_3 \times \delta + c_4 \times \delta^2 \right)$$

$$d_{\text{avg}} = \frac{\text{OD} + \text{ID}}{2}$$

$$\delta = \frac{\text{OD} - \text{ID}}{\text{OD} + \text{ID}}$$

(1)

where coefficients  $c_1$ – $c_4$  has the value of 1, 2.29, 0, and 0.19, respectively. The OD and ID correspond to the outer and inner diameters of the structure.

The series resistance computation is expressed in (2). This formula consists of two main parts: the resistance contributed by the metallization layers and the vias. The huge amount of vias utilization in this design demands a necessity to include via resistance in the ohmic calculation. The technology parameters of the Chartered Semiconductor Manufacturing's 0.13- $\mu$ m process are summarized in Table I

$$R_{\rm DC} = \rho_{\rm metal} \times \frac{l_{\rm length}}{2(w_{\rm width} \times t_{\rm TM\_thickness})} + \rho_{\rm metal} \times \frac{l_{\rm length}}{2(w_{\rm width} \times t_{\rm TM\_4\_thickness})} + \rho_{\rm via} \times t_{\rm via\_height}.$$

(2)

Fig. 8 shows two series L–R branches to model the skin and proximity effects. An analytical equation is suggested in [18].

Fig. 8. Equivalent lumped-circuit model for the proposed design.

TABLE I TECHNOLOGY PARAMETERS FOR 0.13- $\mu$ m Process

| D                                                      | \$ 7 <sub>0</sub> 1 <sub>000</sub> |  |

|--------------------------------------------------------|------------------------------------|--|

| Parameter                                              | Value                              |  |

| Silicon resistivity                                    | 10 Ω-cm                            |  |

| Silicon thickness $(h_{sil})$                          | $150~\mu\mathrm{m}$                |  |

| Silicon dielectric constant                            | 11.9                               |  |

| Top Metal thickness $(T_{TM})$                         | $3.03 \ \mu m$                     |  |

| Metal 1-5 thickness $(T_M)$                            | $0.465~\mu{\rm m}$                 |  |

| Metal sheet resistivity ( $\rho_{metal}$ )             | $26.55 \text{ m}\Omega$ - $\mu$ m  |  |

| Inter-metal oxide thickness                            | $0.42~\mu{\rm m}$                  |  |

| Eff. Inter-metal dielectric constant                   | 4.2                                |  |

| Eff. Via sheet resistance $(\rho_{via})$               | 90 m $\Omega/\mu$ m                |  |

| Metal Vert. plate-plate separation $(h_{(metal-f-f)})$ | $3.038 \mu m$                      |  |

| Top Metal - Silicon distance $(h_{(TM-Sil)})$          | $6.595 \mu m$                      |  |

| Metal 2 - Silicon distance $(h_{(TM-4-Sil)})$          | $1.593 \mu m$                      |  |

However, for SPICE simplicity, Gao and Yu have reported using a semiempirical equation to compute the ladder elements shown as follows in (3) [19]:

$$R_{\text{ser-pri-}a,b} = K_{Rp} \times R_{\text{par-pri-}a,b}$$

$$L_{\text{pri-}a-2,\text{pri-}b-2} = K_{Lp} \times L_{\text{pri-}a-1,\text{pri-}b-1}$$

$$R_{\text{par-pri-}a} = R_{\text{par-pri-}b} = \left(\frac{1+1}{K_{Rp}}\right) \times \frac{R_{\text{DC}}}{2}$$

$$L_{\text{pri-}a-1} = L_{\text{pri-}b-1} = \frac{L_{\text{DC}}}{[2+2K_{Lp} \times (1+K_{Rp})^{-2}]}.$$

The semiempirical coefficients  $K_{Rp}$  and  $K_{Lp}$  are held constant for this work, e.g.,  $K_{Rp} = 1.1$  and  $K_{Lp} = 0.3$ . The k term indicates the strength of the magnetic coupling between the primary and secondary coils. The use of  $SiO_x$  as the isolation median instead of ferromagnetic material results in finite

magnetic losses. The relationship between the k factor and the fabrication parameters can be rather complicated. Alternatively, [10] and [21] proposed a closed-form k expression based on the layout parameters. However, those suggested equations are based on unilateral coupling that underestimate the capability of this novel design. Therefore, a semiempirical geometries-based equation proposed by Mohan  $et\ al.$ , expressing the k term as a function of the layout offset, is applied in this study [22]. The  $d_s$  suggested are modified to take into account the vertical separation between the primary and secondary coils, as shown in (9)

$$k = 0.9 - \left(\frac{d_s}{d_{\text{avg}}}\right) \tag{4}$$

where  $d_s = \sqrt{(\Delta x)^2 + (\Delta y)^2 + (\Delta h)^2}$ . In this proposed design,  $\Delta x$  and  $\Delta y$  are zero, as the two windings do not offset in the x- and y-axis. Thus, it can be simplified as  $d_s = \Delta h$ .

2) Parasitic Capacitances: Beneath the device's lowest metal, there is a series of oxide layers before the silicon—oxide interface. This is described as a parasitic capacitance in the lumped-circuit model. For a passive device, the coplanar dimensions are much larger than the oxide thickness. Hence, the oxide capacitance is proportional to the total area occupied by the device (10)

Area =

$$8 \times \tan 22.5^{\circ} \left( \left( \frac{\text{OD}}{2} \right)^2 - \left( \frac{\text{ID}}{2} \right)^2 \right)$$

(5)

$$C_{\text{ox-pri,ox-sec}} = \frac{\varepsilon_0 \times \varepsilon_r \times \text{Area}}{2 \times t_{\text{TM-4-Sil}}}.$$

(6)

Fig. 9. Cross-sectional view of the fully symmetrical transformer showing multidirectional electrical coupling.

Fig. 3 shows that ~80% of the trace is part of the main octagonal block. Therefore, the distribution of the oxide capacitance can be expressed as  $C_{\text{ox},P1} = C_{\text{ox},P3} = C_{\text{ox},P2} = C_{\text{ox},P3} = 0.1 \times C_{\text{ox-pri}}$ , whereas  $C_{\text{ox-ctr-1}} = C_{\text{ox-ctr-2}} = 0.8 \times C_{\text{ox-pri}}$ .

The  $C_{PP}$  and  $C_{\mathrm{center}}$  modeling in this design is slightly different from the conventional transformer. The proposed design's electrical capacitive coupling from one winding to another involves both the vertical and lateral axes, as shown in Fig. 9.

The total vertical overlapping and horizontal length is geometrically computed by

$$l_{\text{vertical}} = 8 \times \tan(22.5^{\circ})$$

$$\times \left( \sum_{i=1}^{i=N} \text{ID} + (2 \times i - 1) \times W + 2 \times (i - 1) \times S \right)$$

$$l_{\text{horizontal}} = 8 \times \tan(22.5^{\circ})$$

$$\times \left( \sum_{i=1}^{i=N} \text{ID} + 2 \times i \times W + \frac{(2 \times i - 1) \times S}{2} \right). \quad (7)$$

Subsequently, the overall port–oxide–port capacitance can be derived by substituting the length into the general capacitance (13). The overall port–oxide–port capacitance is distributed across the lumped-circuit model with minimum fitting coefficient, i.e.,  $C_{pp,P1-2} = C_{pp,P3-4} = 0.1 \times C_{pp-\text{overall}}$ ,  $C_{\text{center}} = 0.2 \times C_{pp-\text{overall}}$ , and  $C_{pp,P2-3} = C_{pp,P1-4} = 0.3 \times C_{pp-\text{overall}}$ .

The components  $C_{pp,P1-\mathrm{sec\_ctr}}$ ,  $C_{pp,P2-\mathrm{pri\_ctr}}$ ,  $C_{pp,P3-\mathrm{sec\_ctr}}$ , and  $C_{pp,P4-\mathrm{pri\_ctr}}$  are introduced to model the inter-quadrants electrical coupling. However, the derivation is rather complicated. Therefore, an optimization process has been performed on these components using Agilent Technologies' Advanced Design System (ADS) to identify its value. In order to lower the dynamic range for optimization, all these capacitance are set to be equal since this is a fully symmetrical design.

3) Substrate Network: The capacitance  $C_{\rm sub}$  models the parasitic capacitive effect between the device and substrate. The area equation based on device's layout parameters (10) is calculated using (13)

$$C_{\text{sub}} = \frac{2 \times \varepsilon_0 \times \varepsilon_r \times \text{Area}}{h_{\text{sil}}}.$$

(8)

TABLE II COMPONENTS VALUE FOR THE PROPOSED DESIGN

| Component           | Measured value   Computed value |                   | Optimized value |  |

|---------------------|---------------------------------|-------------------|-----------------|--|

| $L_{DC-pri}$        | 2.933 nH 2.999 nH               |                   | 2.999 nH        |  |

| $L_{DC-sec}$        | 2.933 nH                        | 2.999 nH          | 2.999 nH        |  |

| $R_{DC-pri}$        | $10.074~\Omega$                 | $9.907~\Omega$    | $9.907~\Omega$  |  |

| $R_{DC-sec}$        | $10.074~\Omega$                 | $9.907~\Omega$    | $9.907~\Omega$  |  |

| $C_{pp-overall}$    | -                               | 349.23 fF         | 350 fF          |  |

| $\hat{C}_{ox-pri}$  | -                               | 176.69 fF         | 176.69 fF       |  |

| $C_{sub}$           | -                               | 18.156 <i>f</i> F | 18 <i>f</i> F   |  |

| $R_{sub}$           | -                               | 522.78 $\Omega$   | 530 Ω           |  |

| $C_{pp,P1-sec_ctr}$ | -                               | -                 | 3 <i>f</i> F    |  |

| k                   | 0.86                            | 0.86              | 0.86            |  |

For the ohmic losses in the substrate, [23] suggested an analytical layout parameter-based equation

$$R_{\text{sub}} = \frac{1}{\pi \times \sigma_{\text{sub}} \times l_{\text{mean}}} \times \ln \left[ 2 \times \coth \left( \frac{\pi \times (W_{\text{dev}} + 6 \times h_{\text{TM-4-Sil}} + T_M)}{8 \times h_{\text{sil}}} \right) \right]$$

(9)

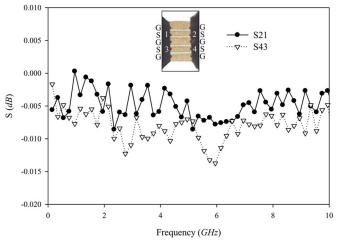

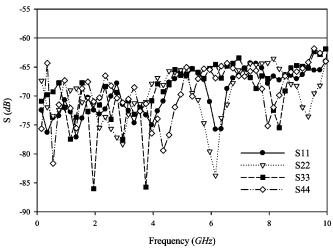

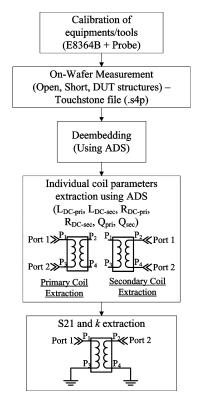

where  $W_{\text{dev}} = (\text{OD} - \text{ID})/2$  is the complete width of the coil, and  $l_{\rm mean} = 8 \times \tan(22.5^{\circ}) \times d_{\rm avg}$  denotes the mean perimeter of the device. All the component values are optimized using ADS optimization tools, as shown in Table II. The variation of the optimization is kept to be <1% so as to maintain the credibility of all the proposed semiempirical equations. The model is verified with the measurement data obtained using Agilent Technologies' E8364B PNA network analyzer and physical layer test system (PLTS) on a Cascade S300 probe station. Ground-signal-ground-signal-ground (G-S-G-S-G) type of Infinity probes (pitch: 100  $\mu$ m) are carefully calibrated using a short, open, load, reciprocal thru (SOLR) on an impedance standard substrate (ISS: 129-239) so as to ensure no measurement errors are brought over to the device data. Figs. 10 and 11 show the transmission and reflection power of the through structure with 2-ps delay found in the ISS. The results has demonstrated that the calibration is well performed with minimum transmission loss ( $\approx 0$  dB, refer to Fig. 10) and excellent noise floor (<-60 dB, refer to Fig. 11).

Good agreement between the modeled and measured parameters (S-parameters and figure-of-merits) of the device has been achieved. Details measurement techniques and extraction procedure are depicted in Fig. 12.

#### III. EXPERIMENTAL EVALUATION

## A. Existing Transformer Design

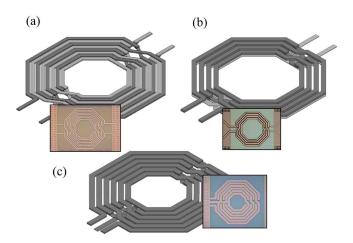

The existing transformer designs are studied in this section prior to their performance evaluation. Fig. 13(a)–(c) illustrates the interleaved, stacked, and differential inductor configurations, respectively. Each figure comes with the silicon die photograph based on Chartered Semiconductor Manufacturing's 0.13- $\mu$ m process. In this study, all the configurations will be standardized to octagonal shape. The closest approximation to a circle is an octagon, which does not violate any design rule.

Fig. 10. Transmission power of the 2-ps delay through line.

Fig. 11. Reflection power of the 2-ps delay through line.

## B. Silicon Area Efficiency

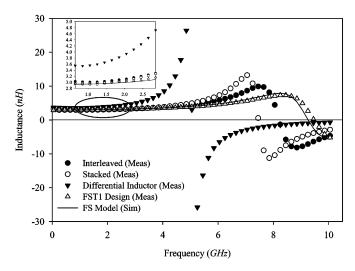

To conduct a study on the area efficiency of various configurations, the inductance has been identified as a reference figure-of-merit (15). All the designs are drawn to achieve individual coil inductance of  $\sim 3-3.5$  nH, as displayed in Fig. 14. The geometry parameters are tabulated in Table III with the silicon area normalized to the smallest device size (stacked and fully symmetrical design)

$$L_p = \frac{\mathrm{imag}\left(\frac{1}{Y_{11}}\right)}{2 \times \pi \times f}.$$

(10)

Table III demonstrates that the interleaved and differential inductor occupied more than twice the silicon area as compared to the stacked or the fully symmetrical transformer. Therefore, in order to perform a fair evaluation, these transformers with the smallest silicon area are chosen to be the suitable candidates.

## C. Stacked Versus Fully Symmetrical

Stacked and fully symmetrical transformer with the same silicon area of 228.28  $\mu m^2$  have been tested. The quality (Q) factor, inductance, coupling coefficient, and S21 between the two transformers are compared and discussed in Section III-C.1. The proposed equivalent lumped-circuit model is also tested

Fig. 12. Flowchart of the measurement and extraction process.

Fig. 13. 3-D view of the: (a) interleave transformer, (b) stacked transformer, and (c) differential inductor configuration with their respective 0.13- $\mu$ m silicon die photograph.

against the measured silicon data to demonstrate the ability to achieve good agreement.

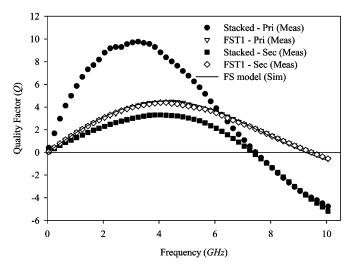

1) Q Factor and SRF: The individual Q factors illustrated in Fig. 15 is extracted from (16). During this extraction, the coil of no interest will be isolated (unconnected) so as not to affect the extracted data, i.e., while extracting for  $Q_{\rm pri}$ , terminal P1 and P3 will be connected to Port 1 and Port 2 leaving terminal P2 and P4 unconnected; the same method applies for  $Q_{\rm sec}$  extraction (refer to Fig. 12)

$$Q_{\text{pri,sec}} = \frac{\text{imag}\left(\frac{1}{Y_{11}}\right)}{\text{real}\left(\frac{1}{Y_{11}}\right)}.$$

(11)

Fig. 14. Inductance plot of the various transformer configurations.

TABLE III

LAYOUT PARAMETERS OF THE VARIOUS TRANSFORMERS

| Design            | ID        | W         | N | OD        | Area        | Norm |

|-------------------|-----------|-----------|---|-----------|-------------|------|

|                   | $(\mu m)$ | $(\mu m)$ |   | $(\mu m)$ | $(\mu m^2)$ | Area |

| Interleaved       | 100       | 6         | 4 | 238       | 469.25      | 2.06 |

| Stacked           | 100       | 6         | 4 | 160       | 228.28      | 1    |

| Differential      | 100       | 15        | 6 | 310       | 796.12      | 3.49 |

| Fully symmetrical | 100       | 6         | 4 | 160       | 228.28      | 1    |

Fig. 15. Q factor plot of the stacked and FST1 design.

The outcome for the FST1, in term of the Q factor, does not show any advantage as compared to the primary (topmost) coil of the stacked transformer, and it does exhibit excellent symmetry between the two windings. In fact, the resulting lower individual Q factor for the proposed transformer is due to the mixture of multiple thick and thin metal quadrants. Thinner metal layers (t) has higher ohmic losses, shown as follows in (12):

$$R = \rho \times \frac{\text{length}}{\text{width} \times \text{thickness}}.$$

(12)

For the same reason, the stacked transformer's secondary winding demonstrates a much lower Q factor of < 4. The data has clearly shown that the stacked's primary winding is able

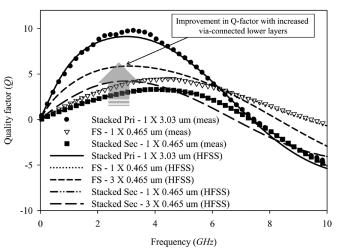

Fig. 16. Q factor plot of the ordinary FST1 design, stacked design, and the FST1 design with via-connected three lower metal layer, together with the respective HFSS simulation result.

to achieve a high Q factor, its secondary winding exhibits a much poorer asymmetrical performance. This asymmetricity will cause degradation in the circuit performance, especially for a differentially driven design. Majority of the practical RF circuits require inductors/transformers to have a higher Q factor, but there are certain parts of the circuit that do not really require a high-Q factor, i.e., see Fig. 2(a) [15]—the drain inductors and source inductors can be replaced by a fully symmetrical transformer configured as differential inductors as this portion of the design demands the device to be fully symmetrical instead of having a higher Q factor.

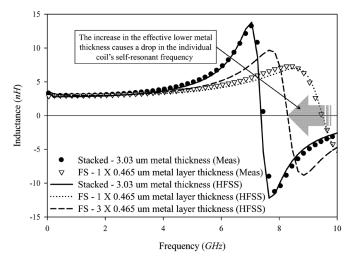

Nonetheless, it is still plausible to mitigate the low-Q factor drawback faced by the proposed design using physical layout optimization. The top metal has a thickness of 3.03  $\mu$ m, which is more than six times thicker than the lower layers (0.465  $\mu$ m). By increasing the thickness of the bottom layer that is formed by via-connected multiple layers of lower metal, the effective real term of the coil's impedance real $(1/Y_{11})$  will decrease. To justify this argument, simulation has been performed using Ansoft's High Frequency Structure Simulator (HFSS). The HFSS simulation profile is calibrated to the Chartered's 0.13-µm technology so as to ensure that the results obtained are credible. The calibrated HFSS has demonstrated an excellent matching on the comparison of the simulated ordinary FST1 design  $(FS - 1X0.465 \,\mu\text{m})$  metal layer thickness) and the stacked design with its measured silicon data, as shown in Fig. 16. The 3-D view of the FST1 design with a via-connected three lower metal layer is illustrated in Fig. 17. In Fig. 16, the HFSS simulation demonstrates that with the increase of the effective thickness of the lower metal layers, a higher Q factor can be achieved. The inductance plot shown in Fig. 18 illustrates that the Q improvement technique does not affect the dc inductance value of the device. In contrast, the SRF of the individual coil has dropped. This reduction is attributed to the shortening of the distance between the two coils, which increases the distributed winding capacitance. (i.e.,  $h_{\rm before} > h_{\rm after}$ , as displayed in Fig. 17). On top of that, Danesh et al. has also suggested that a microstrip winding driven differentially gives a higher Q factor and broader bandwidth than a single-ended terminal [24].

Fig. 17. 3-D view of the FST1 design with via-connected three lower metal layer.

Fig. 18. Inductance plot of the ordinary FST1 design, stacked design, and the FST1 design with via-connected three lower metal layer, together with their respective HFSS simulation result.

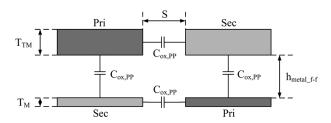

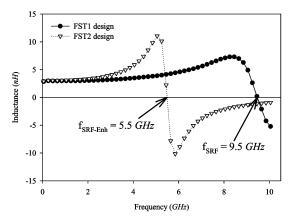

The individual SRF  $(f_{SRF})$  demonstrated by the FST1 design shows a significant improvement as compared to the stacked transformer depicted in Figs. 14 and 15, i.e., the stacked transformer's  $f_{\rm SRF}=7.5~{\rm GHz}$  and the FST1 design's  $f_{\rm SRF}=9.5$  GHz. This increment in  $f_{\rm SRF}$  can be attributed to the larger separation of the winding's vertical plate-to-plate distance  $(h_{(\text{metal}\_f-f)})$ . The stacked transformer is formed using TM and TM-2, whereas the new design uses TM and TM-4 layers. The increment in the separation causes an decrease in capacitance, which translates to higher  $f_{SRF}$ . In order to model the individual SRF  $(f_{SRF})$  of the proposed design, a modification to Zhou and Allstot's differential SRF equation in [2] is used, as shown in (13). The individual SRF is extracted with the coil of no interest unconnected. This is to isolate the mutual coupling effect that causes the individual coil inductance to change (e.g., while extracting primary coil, the secondary coil is unconnected). Based on the novel inter-coil crossing method, the oxide height of each proposed winding is not constant throughout. Thus, an average oxide height [refer to (14)] is needed to determine the effective oxide capacitance  $(C_{\text{ox-avg}})$  using (13) as follows:

$$f_{\text{SRF}} = \frac{1}{2 \times \pi \sqrt{L \times C_{\text{ox-avg}}}} \left( 1 - \frac{R_{\text{DC}}^2 \times C_{\text{ox-avg}}}{L} \right)^{0.5} \tag{13}$$

$$h_{\text{ox-avg}} = \frac{h_{\text{TM-Sil}} + h_{\text{TM-4-Sil}}}{2}.$$

(14)

Fig. 19. S21 and coupling coefficient (k) plot of the stacked and FST1 designs.

Based on (13), the computed  $f_{\rm SRF-model}$  is 9.483 GHz and the extracted  $f_{\rm SRF-meas}$  is 9.5 GHz (see Fig. 15). It can be concluded that the equation is able to predict the SRF of the proposed design with less than 0.2% error.

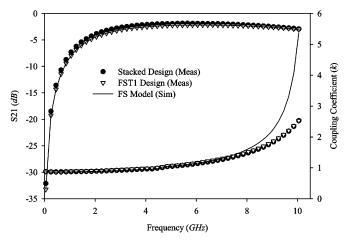

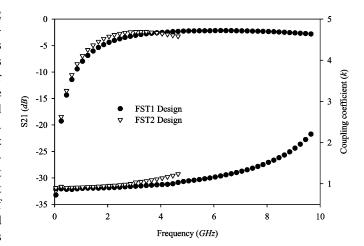

2) S21 and Coupling Coefficient (k): Lastly, the most critical figure-of-merits, S21—transmission gain and k—are addressed. Both transformers are connected in a two-port configuration to evaluate the ability to transfer power (S21) and its magnetic strength (k) from one winding to another. The schematic connection of the transformers is shown in the S21 and k extraction block of Fig. 12. The magnetic coupling coefficient is extracted using (9). Both S21 (in decibels) and k are plotted in Fig. 19

$$k = \sqrt{\frac{\operatorname{imag}(Z_{12}) \times \operatorname{imag}(Z_{21})}{\operatorname{imag}(Z_{11}) \times \operatorname{imag}(Z_{22})}}.$$

(15)

These two parameters are considered the most fundamental requirements in transformer design. In Fig. 19, the FST1 is able to attain the same comparable transmission power as the stacked transformer, having S21 < 5 dB. However, the FST1 shows a slight improvement in the k value as compared to the stacked transformer, i.e., the stacked transformer has k = 0.82 and the FST1 has k = 0.86. The enhancement demonstrated by the novel inter-coil crossing method is not drastic, as it does not allow the coils to have maximum overlapping surface area (which is needed to facilitate the quadrants crossing shown in Fig. 4). Nevertheless, the comparison with the stacked transformer that has the highest k value (having the largest coil overlapping surface area) ever reported demonstrates that although the proposed design does not geometrically favor its k value, it is still able to attain a comparable value with slight improvement. The above finding has proven that this unique way of connecting the coils is both electrically and magnetically effective.

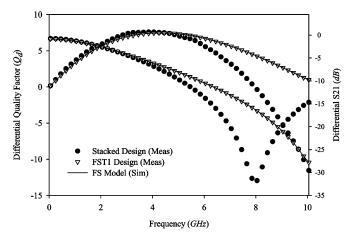

3) Differentially Driven TLT Mode: In this section, the proposed and stacked designs are tested in the differentially driven TLT mode shown in Fig. 1(b). The differential data can be extracted using PLTS (as touchstone (.s2p) file) or standard

Fig. 20. Differential Q and S21 of the stacked and FST1 design in TLT mode.

single-ended to differential mode conversion method (16) as follows:

$$S_{D11} = 0.5 \times (S11 - S21 + S12 - S22)$$

$$S_{D12} = 0.5 \times (S13 - S23 + S14 - S24)$$

$$S_{D21} = 0.5 \times (S31 - S41 + S32 - S42)$$

$$S_{D22} = 0.5 \times (S33 - S43 + S34 - S44).$$

(16

The differential performance ( $Q_d$  and  $S_d21$ ) are taken using (16) and plotted in Fig. 20. The result has shown that the proposed design is suitable for higher frequency band applications as compared to the stacked design. Based on Fig. 20, it shows that the stacked design's differential S21 rolls off rapidly after 5 GHz and reaches its self-resonant point at  $\approx 8$  GHz. On the other hand, the proposed design is able to attain a more gradual rolloff in its transmission loss  $(S_d21)$  with its SRF at 10 GHz. This is to say that the proposed design is able to achieve 2 GHz more operating frequency than the stacked design at no additional cost. Looking into the differential Q performance plot (see Fig. 20), it has proven that the symmetricity is an important aspect in differential application. The single-ended Q factor of the stacked's primary coil (refer to Fig. 15) has been reduced by its asymmetric secondary coil. Thus, the stacked design has experienced a lower differential Q value shown in Fig. 20. On the other hand, the proposed design (with a fully symmetrical structure) has further boosted the differential Q value comparable to that of the stacked design. In general, the proposed design is expected to perform even better with a higher individual coil's Q value. This can be achieved based on the discussion in Section III (Q factor and SRF).

4) Enhancement to the Proposed Design: The FST1 shows improvement in the k value,  $f_{\rm SRF}$ , and better area efficiency. However, the transmission power (S21) illustrated in Fig. 19 is only able to achieve a similar value to that of the stacked transformer. It is because the proposed design's primary and secondary coil vertical plate-to-plate distance has become further apart. This physical implementation reduces the electrical coupling capability. To demonstrate the ability to achieve higher transmission gain, the FST1 design has been enhanced by shifting the lower metal quadrants from TM-4 to TM-1, as

Fig. 21. 3-D view of the FST2 design using the top two metal layers to enhance the transmission power.

Fig. 22. Cross-sectional view of the second proposed transformer design using the top two metal layers to enhance the transmission power.

Fig. 23. Measured S21 and coupling coefficient (k) plot of the FST1 and FST2 designs.

shown in Fig. 21, the 3-D view of the second proposed design (FST2). The vertical profile of the second proposed design is depicted in Fig. 22.

Fig. 21(a) and (c) presents the narrowing of the inter-coil plate-to-plate distance. Fig. 21(b) shows the rerouted traces from the lower metal layer (TM-4) to the higher one (TM-1).

The performance parameters of the FST2 design are plotted in Fig. 23. It has demonstrated improvement in terms of the transmission gain, up to a frequency band of 4 GHz. In Fig. 23, at 2 GHz, the S21 value of the first design is -4.4 dB and the second design has a S21 of -3.29 dB. The high frequency response of the S21 starts to roll off rapidly after 4 GHz. This phenomenon is caused by the intensive electrical coupling within

Fig. 24. Measured inductance of the FST1 and FST2 designs reflecting the drop in the  $f_{\rm SRF}$ .

the coils that induced high leakage in high-frequency applications. Concurrently, the plot also displays an increase in the k value. It has risen from  $k_{1\rm st}=0.86$  to  $k_{2\rm nd}=0.9$ .

There is a tradeoff point for this enhancement technique. The increase in the electrical capacitive effect results in a reduction of the individual coil SRF ( $f_{\rm SRF}$ ), as revealed in Fig. 24. The FST2 design's  $f_{\rm SRF}$  drops from 9.5 GHz, for the FST1 design, to 5.5 GHz. This is caused by the large distributed shunt capacitance that dominates the oxide–substrate capacitance. Although fabricating an ideal 1:1 fully symmetrical design is now feasible, the realization of a 1:n (where  $n \gg 1$ ) transformer design that uses the minimum silicon area is still a challenge. In [25] and [26], the authors have reported that an extremely high turn ratio monolithic transformer design is also plausible.

#### IV. CONCLUSION

An area efficient fully symmetrical transformer has been developed. Compared to the existing transformers, the new design is able to achieve higher SRF without much degradation in the other device performance at no additional cost. The full symmetry feature of the design has been investigated and confirmed with measured silicon data. The proposed design has also proven that a fully symmetrical design is able to produce a better Q factor in differential applications. In addition, the novel transformer configuration has opened another means of creating an identical inductor pair without expending on the expensive silicon area. The second proposed design has offered RFIC designers a choice between higher  $f_{\rm SRF}$  and better S21. The credibility of the semiempirical equations introduced in this study have been verified with measurement data based on Chartered Semiconductor Manufacturing's 0.13- $\mu$ m process.

## ACKNOWLEDGMENT

The content of this paper are pending patent filing in the U.S. and Singapore under application 11/750,341, May 18, 2007.

#### REFERENCES

- [1] A. M. Niknejad and R. G. Meyer, "Analysis, design, and optimization of spiral inductors and transformers for Si RFIC's," *IEEE J. Solid-State Circuits*, vol. 33, no. 10, pp. 1470–1481, Oct. 1998.

- [2] J. J. Zhou and D. J. Allstot, "Monolithic transformers and their applications in a differential CMOS RF low-noise amplifier," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 2020–2027, Dec. 1998.

- [3] J. R. Long, "Monolithic transformers for silicon RF IC design," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1368–1382, Sep. 2000.

- [4] D. J. Cassan and J. R. Long, "A 1-V transformer-feedback low-noise amplifier for 5-GHz wireless LAN in 0.18

µm CMOS," IEEE J. Solid-State Circuits, vol. 38, no. 3, pp. 427–435, Mar. 2003.

- [5] M. Straayer, J. Cabanillas, and G. M. Rebeiz, "A low-noise transformer-based 1.7 GHz CMOS VCO," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 3–7, 2002, vol. 1, pp. 286–287.

- [6] W. L. Ping and S. I. Long, "A 5 GHz CMOS low phase noise transformer power combining VCO," in *IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 11–13, 2006, pp. 4–4.

- [7] Y. J. Lee and C. S. Kim, "Q-enhanced 5 GHz CMOS VCO using 4-port transformer," in *Silicon Monolithic Integr. Circuits in RF Syst. Top. Meeting*, Jan. 10–12, 2007, pp. 119–122.

- [8] I. Aoki, S. D. Kee, D. B. Rutledge, and A. Hajimiri, "Fully integrated CMOS power amplifier design using the distributed active-transformer architecture," *IEEE J. Solid-State Circuits*, vol. 37, no. 3, pp. 371–383, Mar. 2002.

- [9] J. Sevick, "A simplified analysis of the broadband transmission line transformer," *High Freq. Electron.*, pp. 48–53, Feb. 2004.

- [10] O. El-Gharniti, E. Kerherve, and J.-B. Begueret, "Modeling and characterization of on-chip transformers for silicon RFIC," *IEEE Trans. Microw. Theory Tech*, vol. 55, no. 4, pp. 607–615, Apr. 2007.

- [11] C. C. Lim, K. S. Yeo, C. Y. Tan, K. W. Chew, J. G. Ma, M. A. Do, and L. Chan, "Equivalent circuit model of a stacked inductor for high-Q on-chip RF applications," *Proc. Inst. Elect. Eng.—Circuits, Devices*, Syst., vol. 153, no. 6, pp. 525–532, Dec. 2006.

- [12] S.-G. Lee, "Area efficient and symmetric design of monolithic transformers for silicon RF ICs," in *IEEE Proc. TENCON'99*, Sep. 15–17, 1999, vol. 2, pp. 880–882.

- [13] C. C. Lim, K. S. Yeo, K. W. Chew, S. F. Lim, C. C. Boon, Q. Ping, M. A. Do, and L. Chan, "High self-resonant and area efficient monolithic transformer using novel inter-coil-crossing structure for silicon RFIC," *IEEE Electron Device Lett.*, Jul. 2008, submitted for publication.

- [14] W. Kluge, F. Poegel, H. Roller, M. Lange, T. Ferchland, L. Dathe, and D. Eggert, "A fully integrated 2.4-GHz IEEE 802.15.4-compliant transceiver for ZIGbee applications," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2767–2775, Dec. 2006.

- [15] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, pp. 384–389.

- [16] C.-H. Chang and C.-Y. Yang, "A low-voltage high-frequency CMOS LC-VCO using a transformer feedback," in *IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 15–17, 2008, pp. 545–545.

- [17] C. C. Lim, K. W. Chew, K. S. Yeo, S. F. Lim, M. A. Do, and L. Chan, "Integrated transformer," U.S. Patent Applicat. 11/750,341, May 18, 2007

- [18] S. Kim and D. P. Neikirk, "Compact equivalent circuit model for the skin effect," in *IEEE MTT-S Int. Microw. Symp. Dig*, 1996, vol. 3, pp. 1815–1818.

- [19] W. Gao and Z. Yu, "Scalable compact circuit model and synthesis for RF CMOS spiral inductors," *IEEE Trans. Microw. Theory Tech*, vol. 54, no. 3, pp. 1055–1064, Mar. 2006.

- [20] S. S. Mohan, M. d. M. Hershenson, S. P. Boyd, and T. H. Lee, "Simple accurate expressions for planar spiral inductances," *IEEE J. Solid-State Circuits*, vol. 34, no. 10, pp. 1419–1424, Oct. 1999.

- [21] T. Biondi, A. Scuderi, E. Ragonese, and G. Palmisano, "Analysis and modeling of layout scaling in silicon integrated stacked transformers," *IEEE Trans. Microw. Theory Tech*, vol. 54, no. 5, pp. 2203–2210, May 2006.

- [22] S. S. Mohan, C. P. Yue, M. Hershenson, S. S. Wong, and T. H. Lee, "Modeling and characterization of on-chip transformers," in *IEEE Int. Electron Devices Meeting*, 1998, pp. 531–534.

- [23] D. Kehrer, W. Simburger, H. D. Wohlmuth, and A. L. Scholtz, "Modeling of monolithic lumped planar transformers up to 20 GHz," in *IEEE Custom Integr. Circuit Conf.*, 2001, pp. 401–404.

- [24] M. Danesh, J. R. Long, R. Hadaway, and D. Harame, "A Q factor enhancement technique for MMIC inductors in silicon technology," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 1998, pp. 217–220.

- [25] C. C. Lim, K. W. Chew, K. S. Yeo, S. F. Lim, M. A. Do, and L. Chan, "Effective high turn ratio transformer," U.S. Patent Applicat. 11/779,892, Jul. 19, 2007.

- [26] C. C. Lim, K. S. Yeo, K. W. Chew, S. F. Lim, C. C. Boon, Qiu-ping, M. A. Do, and L. Chan, "An area efficient high turn ratio monolithic transformer for silicon RFIC," in *IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 15, 2008, pp. 167–170.

Chee Chong Lim was born in Singapore, in 1978. He received the B.E. (Hons.) degree in electrical electronic engineering from Nanyang Technological University, Singapore, in 2004, and is currently working toward the Ph.D. degree at Nanyang Technological University.

His research interests mainly focus on design, modeling, and characterization of on-chip multiple port passive components for RFIC applications.

**Jiang-Min Gu** received the B.Sc. degree in physics and M.Eng. degree in electronic engineering and information science from the University of Science and Technology of China, Hefei, China in 1997, and 2000, respectively, and the Ph.D. degree from Nanyang Technological University, Singapore, in 2005.

In 2004, he joined Nanyang Technological University as a Project Officer, and in 2005 became a Research Fellow. His research interests include design and optimization of low-power low-voltage CMOS arithmetic circuits, and low-power RFIC circuits for

wireless transceivers in short-range communication applications.

**Kiat Seng Yeo** (M'00) received the B.E. (Hons.) degree in electronics and Ph.D. degree in electrical engineering from Nanyang Technological University, Singapore, in 1993 and 1996, respectively.

In 1996, he joined the School of Electrical and Electronic Engineering, Nanyang Technological University, as a Lecturer, and became an Assistant Professor and an Associate Professor in 1999 and 2002, respectively. He became Sub-Dean (Student Affairs) in 2001 and Head of the Department of Circuits and Systems in 2005. He provides consultancy

services to statutory boards and multinational corporations in the areas of semiconductor devices and electronic circuit design. He has been extensively involved in the modeling and fabrication of small MOS/bipolar integrated technologies for the last 12 years. His current research interests include the design of new circuits and systems (based on scaled technologies) for low-voltage low-power applications, RFIC design, integrated circuit design of BiCMOS/CMOS multiple-valued logic circuits, domino logic and memories, and device characterization of deep-submicrometer MOSFETs.

**Kok Wai Chew** (M'02) received the B.E. (Hons.) degree in electrical engineering and M.Eng. and Ph.D. degrees in electrical engineering from Nanyang Technological University, Singapore, in 1996, 1999 and 2007, respectively.

In 1998, he joined Chartered Semiconductor Manufacturing, Singapore, as an Engineer with the Mixed-Signal/RF CMOS Technology Development Group, where he was involved in mixed-signal process characterization and integration, RF CMOS device layout, and characterization. In 2002, he

became a Senior Engineer and joined the Spice Modeling Group, where he is currently responsible for RF CMOS and SiGe BiCMOS actives and passives test-chip design, characterization, modeling, and customer support across all technologies. He is a Member of Technical Staff and Group Leader for RF CMOS characterization and modeling. He has authored or coauthored over 15 papers in leading technical journals and conferences worldwide. He holds 18 U.S. patents. His research interests include characterization and modeling of RF MOS/bipolar transistors, RF passives, and noise characterization and modeling of MOS transistors.

Alper Cabuk (M'07) was born in Istanbul, Turkey, in 1977. He received the B.Sc. degree in electrical engineering from the Middle East Technical University (METU), Ankara, Turkey, in 1999, and the M.Eng. and Ph.D. degrees in electrical and electronic engineering from Nanyang Technological University (NTU), Singapore, in 2002 and 2006, respectively.

From 1998 to 1999, he was with the Information Technologies Institute (Bilten), Ankara, Turkey, where he was an RFIC Engineer designing circuits for the Turkish Armed Forces. From 2005 to 2006,

he was a Research Associate with NTU. From 2006 to 2007, he was a Research Fellow with NTU. He is currently a Teaching Fellow with NTU. His research interests include CMOS RFIC design, low-voltage low-power analog/baseband circuit design, and clock and data recovery circuits for SONET systems.

**Suh Fei Lim** received the B.E. (Hons.) degree in electrical engineering and M.Eng. degree in electrical engineering from Nanyang Technological University, Singapore, in 2001, and 2004, respectively.

In 2003, she joined Chartered Semiconductor Manufacturing, Singapore, as an Engineer with the Electric Testing Department. In 2005, she joined the Spice Modeling Group, where she is currently responsible for device test-chip design, measurement, characterization, modeling, and customer support across all technologies. Her research interests in-

clude device design, characterization, and modeling of RF passive device such as inductors, transformers, and baluns.

Chirn Chye Boon received the B.E. (Hons.) degree in electronics and Ph.D. degree in electrical engineering from Nanyang Technological University (NTU), Singapore, in 2000 and 2004, respectively.

In 2005, he joined NTU as a Research Fellow and became an Assistant Professor that same year. Prior to that, he was with Advanced RFIC, where he was a Senior Engineer. He specializes in direct conversion RF transceiver front-end design, phase-locked-loop frequency synthesizers, clock and data recovery circuits, and frequency dividers.

Dr. Boon is a reviewer for the IEEE TRANSACTIONS OF CIRCUITS AND SYSTEMS—PART I: REGULAR PAPERS, the IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

Manh Anh Do (SM'05) received the B.Sc. degree in physics from the University of Saigon, Saigon, Vietnam, in 1969, and the B.E. (Hons.) degree in electronics and Ph.D. degree in electrical engineering from the University of Canterbury, Canterbury, New Zealand, in 1973 and 1977, respectively.

From 1977 to 1989, he was a Research and Development Engineer and a Production Manager with Radio Engineering Ltd., a Research Scientist with the Fisheries Research Centre, and a Senior Lecturer with the National University of Singapore.

In 1996, he was a Senior Lecturer with the School of Electrical and Electronic Engineering, Nanyang Technological University (NTU), Singapore, where he became an Associate Professor in 1996 and a Professor in 2001. He has been a Consultant on numerous projects in the Singapore electronic industry. From 1990 to 2001, he was the Principal Consultant for the design, testing, and implementation of the 200 million Electronic Road Pricing (ERP) island-wide project in Singapore. From 1995 to 2005, he was the Head of the Division of Circuits and Systems, School of Electrical and Electronic Engineering, NTU. He is the Director of the Centre for Integrated Circuits and Systems (CICS), NTU. He has authored or coauthored over 180 papers in the areas of electronic and communication circuits and systems. His current research interests include digital and mobile communications, RFIC design, mixed-signal circuits, and intelligent transport systems.

Dr. Do is a Chartered Engineer in the U.K. He is a Professional Engineer in Singapore. He is a Fellow of the Institution of Electrical Engineers (IEE), U.K. From 2001 to 2004, he was a council member of the IEE.